FPGA学习记录4——Modelsim和Quartus II联合使用

Quartus II编译通过只能说明我们的语法没有问题,所以我们必须借助于另外一个工具Modelsim进行仿真,通过波形查看具体的逻辑是否正确。

我们可以将仿真理解为我们平时测试电路板的过程,就是给待测单元一定的输入,观察它有什么样的输出以及内部过程如何。因此,在调用Modelsim之前,我们需要编写一段测试激励,给待测模块输入测试激励。

一.测试激励

-

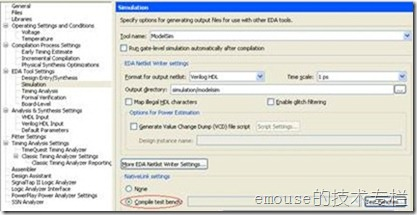

设定仿真工具

assignmentèsettingèEDA tool settingèsimulation 选择你需要的工具。

![]()

-

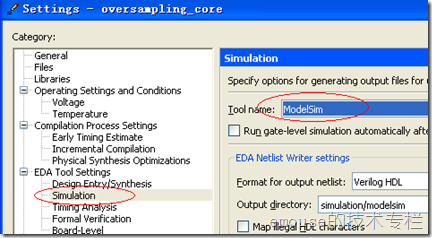

自动产生测试激励文件模板:

processingèstartèStart test bench template writer

![]()

我们点击之后系统会自动在目录:当前文件夹è simulation è modelsim (这个文件夹名字跟你选的仿真工具有关) 中产生一个测试激励文件 xxx.vt(Verilog test bench) 或者 xxx.vht(VHDL test bench), 文件名跟你工程中的Top module 的名字一样, 后缀为.vt或者.vht。

-

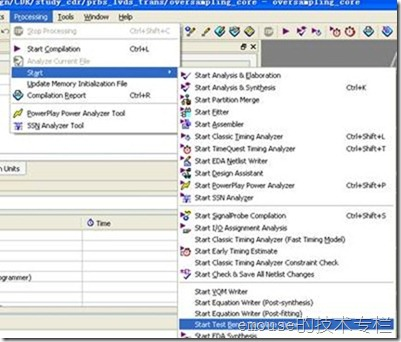

编辑走动生成的test bench文件

我们加入自己需要的激励以及初始化语句,这里我们还要修改test bench的模块名字为tb(我们会看到这个名字和后面的设定有联系)。

![]()

-

连接test bench,我们需要从Quartus中自动调用仿真工具,所以需要设定Native Link选项。

a) 还是在simulation的设置页面里,设定 Native Link对话框中的设定。我们这里因为需要工具自动调用激励所以选中

b) 点击右边的Test Benches, 我们需要在这里设定一个相关联的test bench.

这里会弹出一个让你指定test bench的对话框,因为我们之前没有指定任何的test bench,所以这里是空白的。

c) 指定test bench

因为我们是第一次产生test bench,点击new.

点击New之后会产生一个New Test bench setting的对话框,在这里你将test bench和你的相应的test bench file进行绑定。

我们这里在Test bench name的对话框中输入一个名字”my_1st_tb”, 我们将看到,在下面的Top level module in test bench对话框中也自动显示”my_1st_tb”. 注意这个名字应该和你的test bench 中的module name一致,我们之前在第3步的时候将test bench的module name已经改成了tb,所以我们这里应该把对话框中的名字改成tb。

d) 加入test bench文件

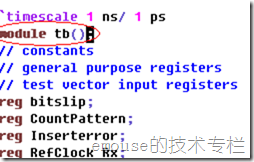

- 进行仿真

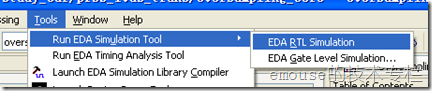

当这些设定都完成了之后, 选择菜单

toolèRun EDA Simulation toolèEDA RTL simulation

![]()

就可以直接调用modelsim进行仿真。

浙公网安备 33010602011771号

浙公网安备 33010602011771号