关于FPGA内部资源的一些了解

从前从来没有深度了解过FPGA片内资源,因为本身自己的做一些小的项目的时候从来就没有考虑过逻辑资源量的问题。但是也遇见过因为逻辑资源没有妥善运用导致的一些警告。最长见的就是某一个变量的最高的几位一直是0的警告,因为在赛林斯或者阿特拉综合时会有系统优化你的设计,也就是它会自动检测到你设计的寄存器其实对你最后生成的查找表没有任何影响却占据了逻辑资源系统就会自动对其进行优化。

FPGA的片内资源主要有分可编程输入输出单元,可配置逻辑块,丰富的布线资源,嵌入式RAM资源,底层内嵌功能资源等等,当然现在最新出的7系列的芯片可能有更多的逻辑资源。那么这些资源对应于我们的verilog代码是怎样的一个体现形式?首先我们知道,我们写的verilog代码包含时序逻辑,组合逻辑,在这其中我们肯定就会用到一些寄存器了,再有有些时候我们也会调用内部的IP核,比如说我们的PLL,RAM,ROM之内的资源。

我们首先来看一看我们用verilog代码所设计出来的到底是哪种电路?

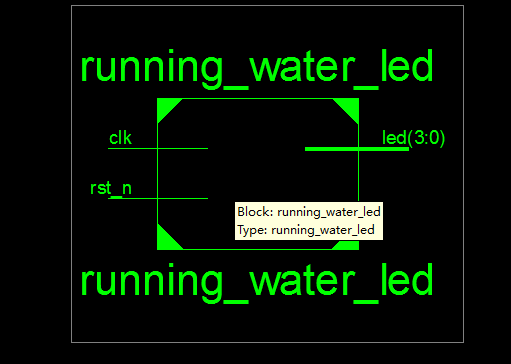

这是一个简单的跑马灯设计模块,用我们的寄存器级视图所显示的功能模块。那么其里面的内部结构又是一个什么样子?

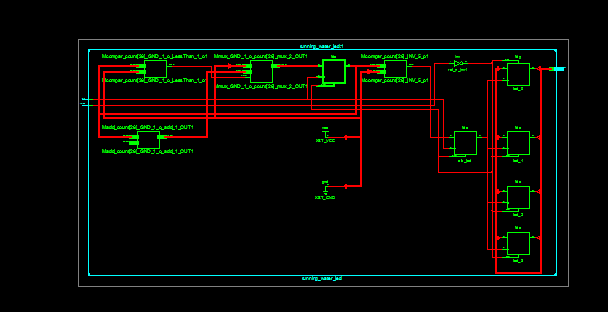

可以看出这就是我们数字电路设计里面学过的D触发器,还是一些组合逻辑,比如选择器,比较器之内的电路。那么真正的下载到FPGA里面的电路就是这些吗?这句话可以说对可以说错?因为触发器,确实是下载到了FPGA里面,但是组合逻辑的选择器,比较器之内的电路会根据其输入输出的功能生成对应的查找表(look up table),查找表又是什么?简单的我们可以理解为数字电路里面的真值表,也就是你只需要关心它的输入输出,不会去管这个中间经过了多少运算。最后根据查找表取出对应的结果就可以。这就是我们最常用的可配置逻辑块了。

还有一点常用的片内RAM(random access memory),这其中需要区分和知道的就是DRAM,和BRAM之分?通常我们在IP核里面调用的RAM就是BRAM,然后我们所使用的寄存器就是DRAM。那么想一想为什么我们调用的IPRAM总是用作数据缓存的作用,几乎不会真正作为存储设备。原因很简单,就是因为如果我们所要存储的数据超过了BRAM的最大极限,其他的数据就会存储到DRAM里面,大量的占用我们的寄存器资源。大家都知道我们的功能模块,时序逻辑也需要很多的寄存器资源。所以这样就会造成一个资源占用量过大,不仅对FPGA本身造成负荷,而且肯定会影响我们最开始设定的逻辑功能。

如果有错误,欢迎大家讨论。

浙公网安备 33010602011771号

浙公网安备 33010602011771号