关于JTAG,你知道的和不知道的都在这里

01、JTAG简介

JTAG(JointTest ActionGroup)是一个接口,为了这个接口成立了一个小组叫JTAG小组,它成立于1985年。在1990年IEEE觉得一切妥当,于是发布了IEEE Standard 1149.1-1990,并命名为Standard Test Access Port and Boundary-ScanArchitecture,这就是大名鼎鼎的JTAG了。

JTAG的三大功能你知道吗,响当当的:

1.下载器,即下载软件到FLASH里。

2. DEBUG,跟医生的听诊器似的,可探听芯片内部小心思。

3. 边界扫描,可以访问芯片内部的信号逻辑状态,还有芯片引脚的状态等等。

JTAG根本没有标准的接口定义,甚至每家公司定义都不一样。在ARM的《系统和接口设计参考》文档中

文档下载地址:

链接:https://pan.baidu.com/s/13aQXOXR73_wiERz2kwN15w

提取码:xaaf

这篇文档列举了不同的JTAG接口

而我们经常在互联网看到的下图,是SEGGER公司的Jlink的JTAG接口。

J-Link是德国SEGGER公司推出基于JTAG的仿真器。简单地说,是给一个JTAG协议转换盒,即一个小型USB到JTAG的转换盒,其连接到计算机用的是USB接口,而到目标板内部用的还是jtag协议。它完成了一个从软件到硬件转换的工作。

同时Jlink也是个人觉的最流行的调试器。通过《系统和接口设计参考》可知,这个ARM官方的JTAG20pin并不相同。

在这里希望大家明白,ARM,Jlink,JTAG之间的关系。

使用频率也挺高的ST-linkV2的接口由上文可知,这也是ST公司自己定义的接口,如下:

Ulink、CMSIS_DAP和其他STM32的仿真器是一样的道理。

02、JTAG介绍

边界测试:

举个例子你有两个芯片,这两个芯片之间连接了很多很多的线,怎么确保这些线之间的连接是OK的呢,用JTAG,它可以控制所有IC的引脚。这叫做芯片边界测试。

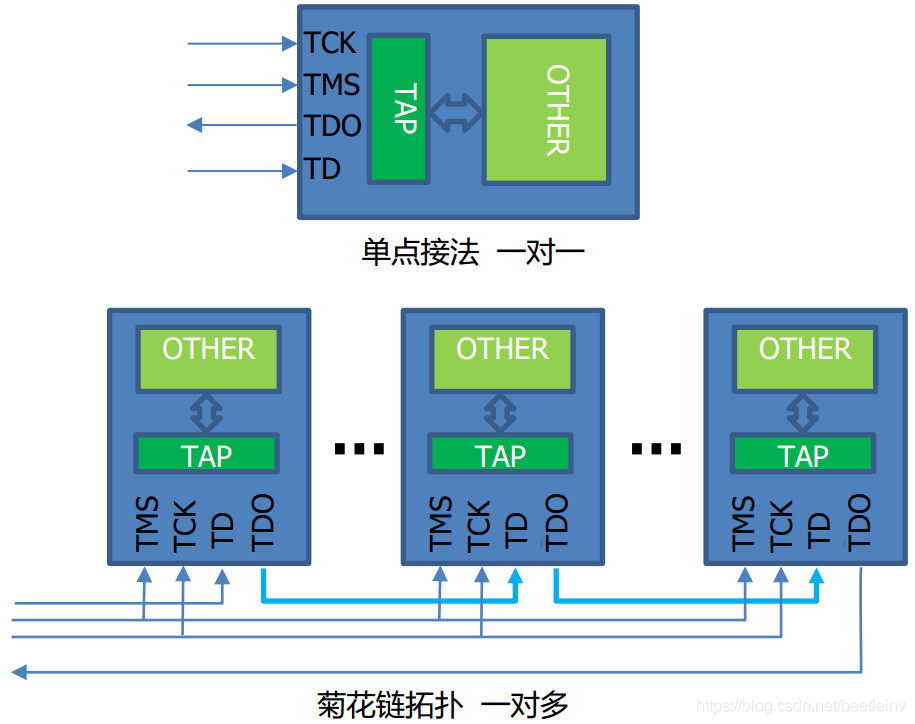

在JTAG接口中,最常用的信号有四个,分别是TCK/TMS/TDO/TDI。JTAG接口可以一对一的使用,也可以组成菊花链的一对多拓扑结构,两种拓扑结构如下图所示。多核的芯片,其芯片内部已经接成了菊花链的形式。

JTAG的菊花链还有很多玩法

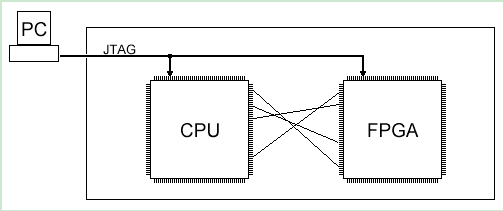

CPU和FPGA制造商允许JTAG用来端口debug;FPGA厂商允许通过JTAG配置FPGA,使用JTAG信号通入FPGA核。

03、JTAG和SWD

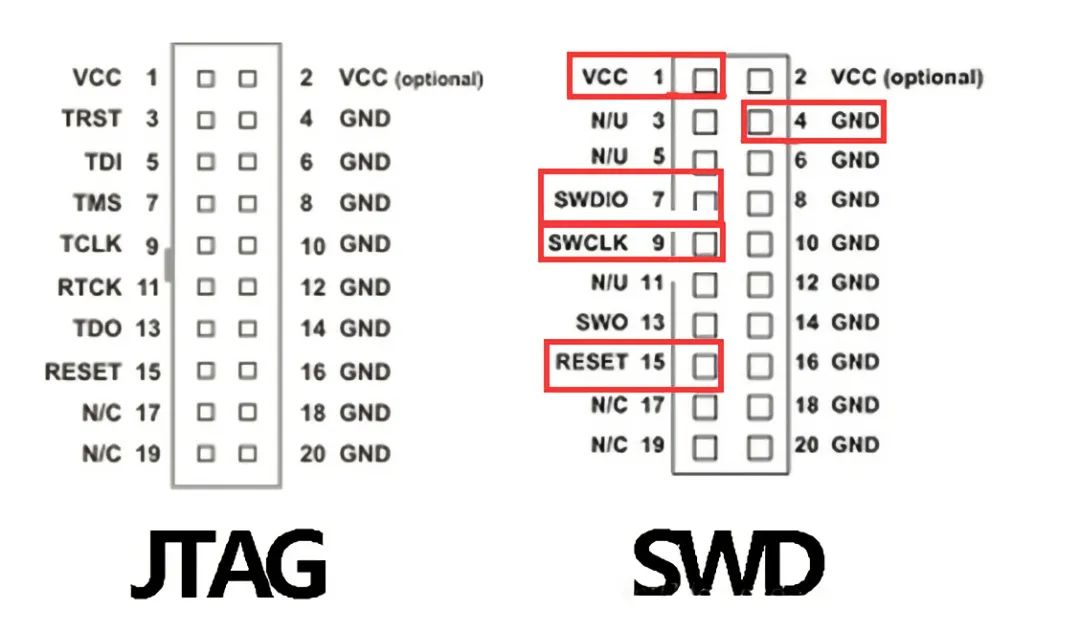

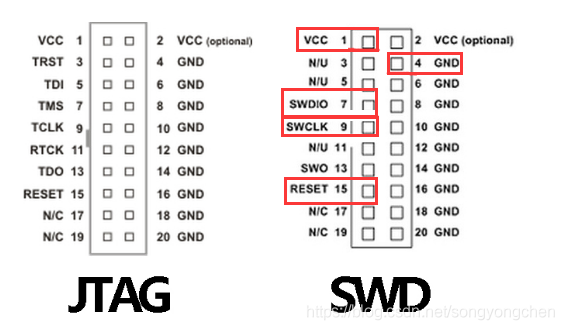

SWD接口:串行调试(SerialWireDebug),应该可以算是一种和JTAG不同的调试模式,最直接的体现在调试接口上,与JTAG的20个引脚相比,SWD只需要4(或者5)个引脚。

VCC、SWDIO、SWCLK、GND(有些情况,也加上了RESET脚)。

SWD和传统的调试方式区别:

-

SWD模式比JTAG在高速模式下面更加可靠。在大数据量的情况下面JTAG下载程序会失败,但是SWD发生的几率会小很多。基本使用JTAG仿真模式的情况下是可以直接使用SWD模式的,只要你的仿真器支持,所以推荐大家使用这个模式。

-

当CPU的GPIO不够用的时候,可以使用SWD仿真,这种模式支持更少的引脚。

-

在硬件PCB的体积有限的时候推荐使用SWD模式,它需要的引脚少,当然需要的PCB空间就小,可以选择一个很小的2.54间距的5芯端子做仿真接口。

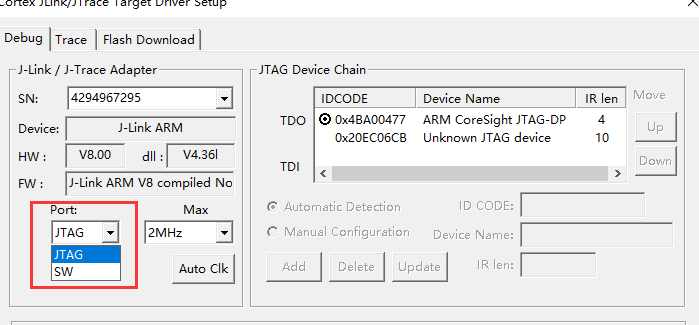

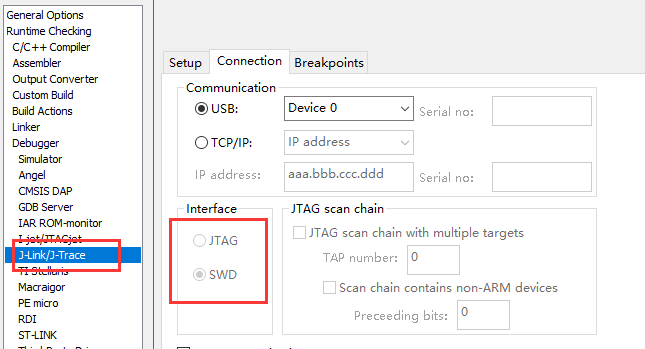

Keil环境下Jlink调试器的JTAG模式和SWD模式

IAR环境下Jlink调试器的JTAG模式和SWD模式

Jlink的JTAG模式和SWD模式对比图

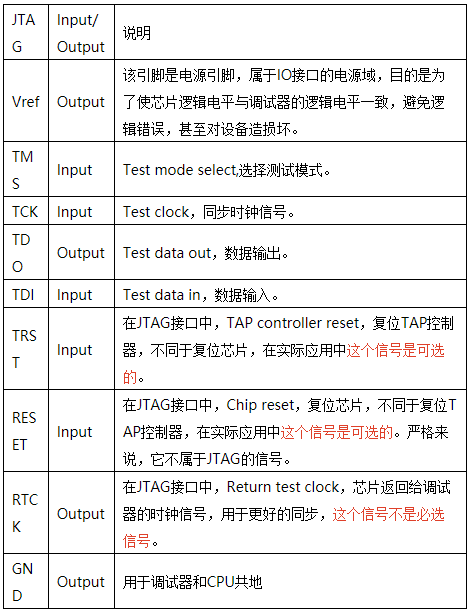

JTAG引脚说明

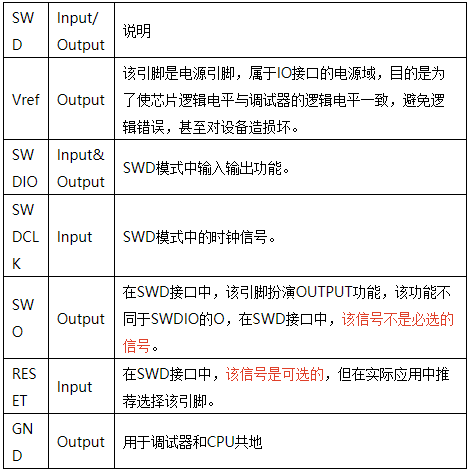

SWD引脚说明

04、关于Vref引脚

上面我们提到Vref引脚,属于IO接口的电源域,目的是为了使芯片逻辑电平与调试器的逻辑电平一致,避免逻辑错误,甚至对设备造损坏。

在Jlink上有Vref的跳线帽。

三个排针:①是NC,②是Vref,是和输出的1脚相连的,③是3.3V

如果要Jlink的1脚Vref输出3.3V,直接将②和③短接即可。

05、关于TRST引脚

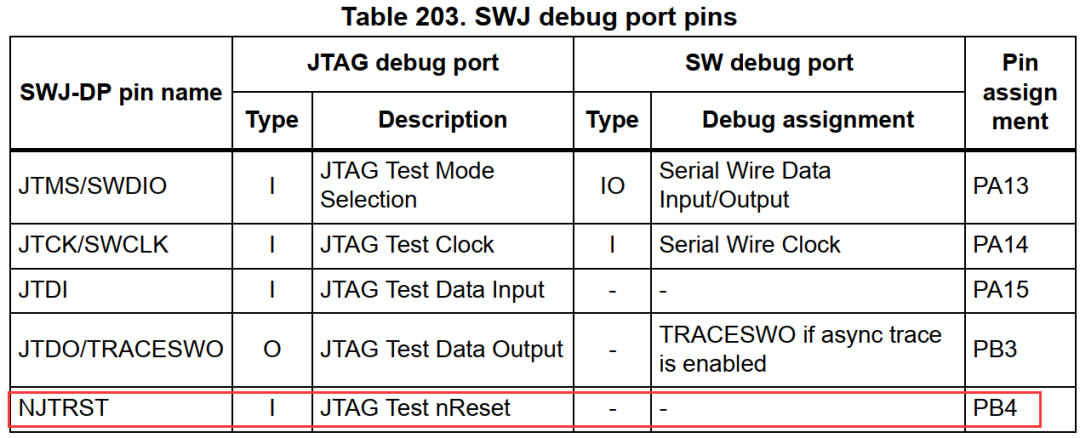

JTAG定义中的TRST引脚,用来复位TAP控制器的。在STM32系列单片机中,并没有TRST引脚,名字为NJTRST。

以STM32F207为例,NJTRST引脚在JTAG和SWD模式中的说明。

STM32F207的SWJI/O引脚可用性

06、RESET引脚作用

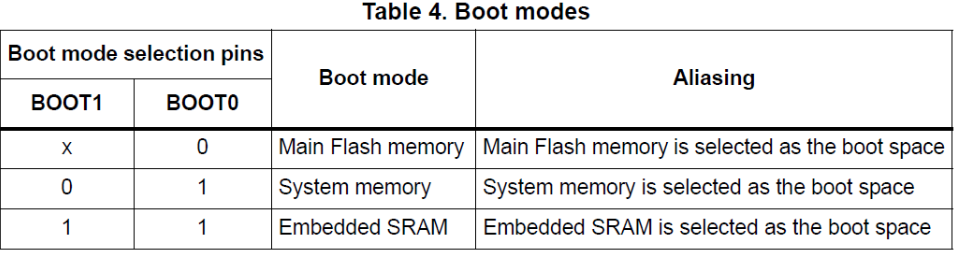

在一些STM32的产品仿真时使用4线的SWD模式,发布版通常会将JTAG口设置为普通IO,或者由于管脚不够用,在发布版用作其他用途。我们在调试发布版,因为禁止了JTAG模式,没有办法仿真了。

这个时候,最常用的做法是,拉高BOOT0管脚,进入MainFlash memory模式,进行debug仿真。

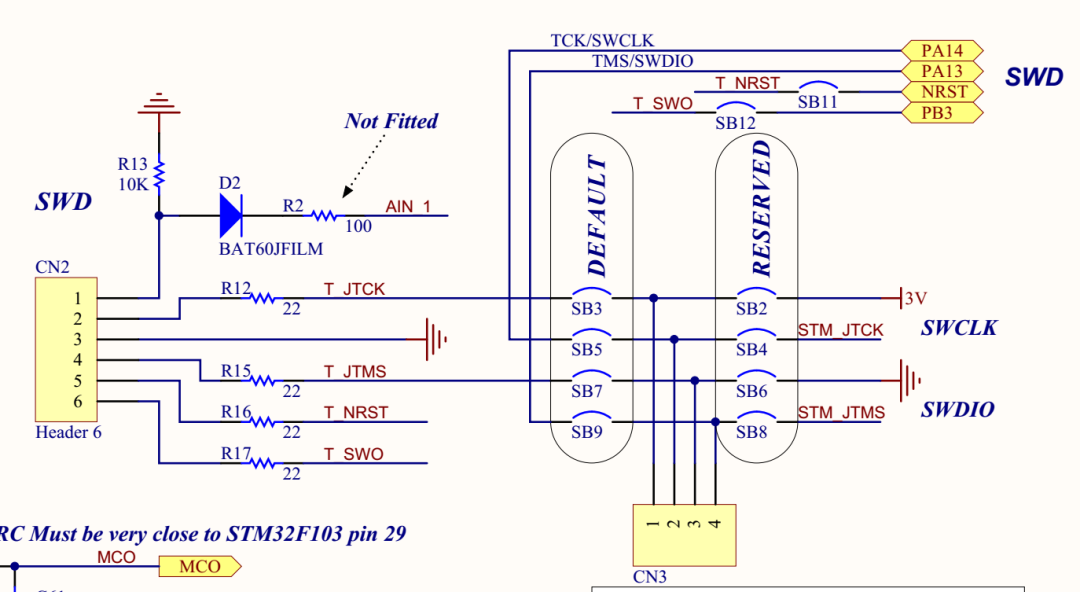

对比STM32的官方开发板,我们在使用SWD模式没有引出RST引脚,当然属于SWD的还有SWO信号,这是个监视用的,也是非常有用。这两个信号都可以连接仿真器的。

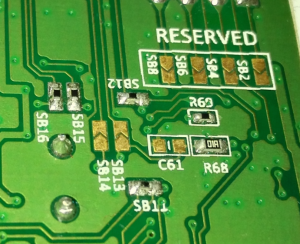

板子上对照:

仿真器有UnderReset的方式,因此,仿真器在需要仿真的时候,会把RST信号送到MCU,让MCU处于RST,或者采用Reset后仿真,代码还没执行到禁止JTAG状态下,所以可以直接仿真。当然,也可以主动复位供电,也是可以脱离原来的JTAG禁止状态。也可以拉高boot0管脚。

浙公网安备 33010602011771号

浙公网安备 33010602011771号