1、创建工程

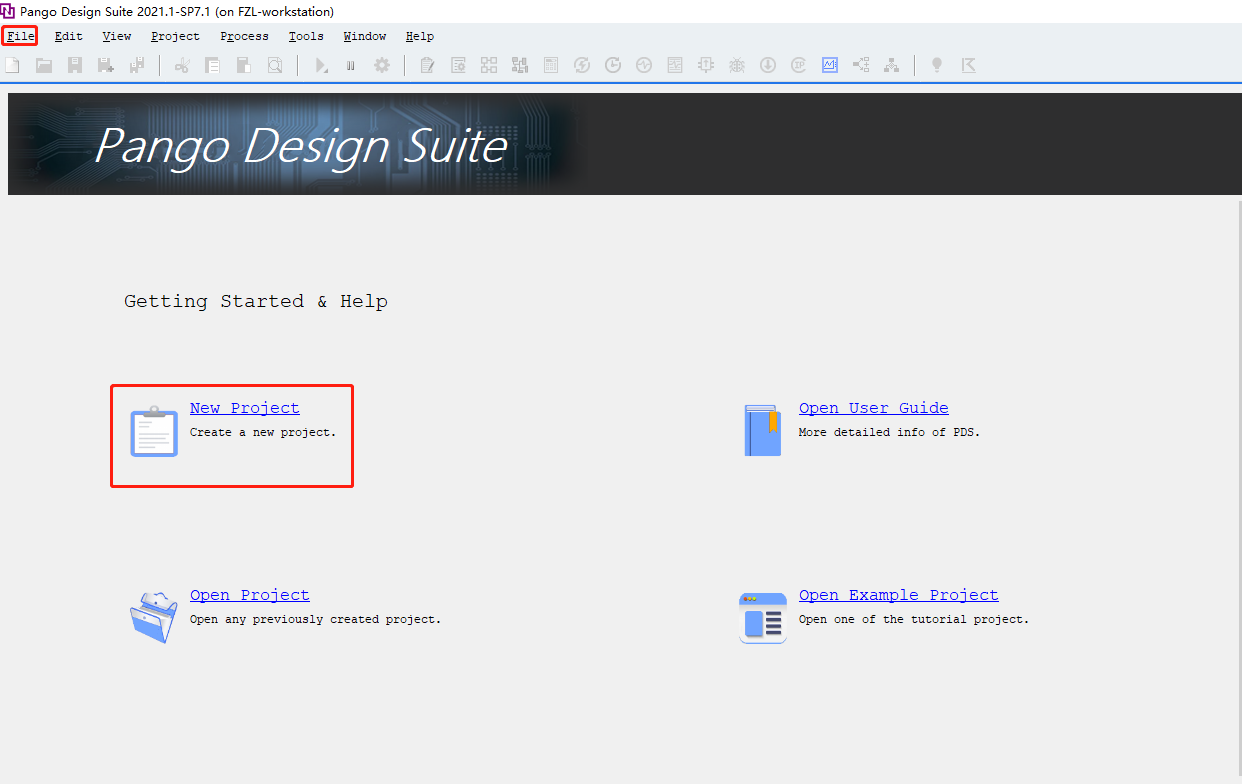

1.1、双击桌面Pango Design Suite图标直接打开软件

1.2、在PDS开发环境里双击Create Project,或者点击file--->New Project,

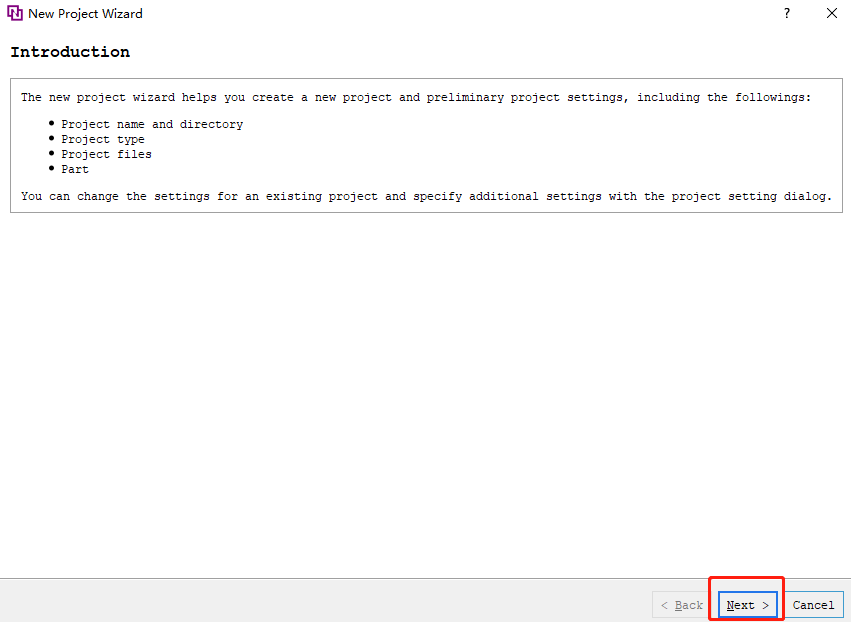

1.3、在弹出的PDS工作向导,点击Next按钮

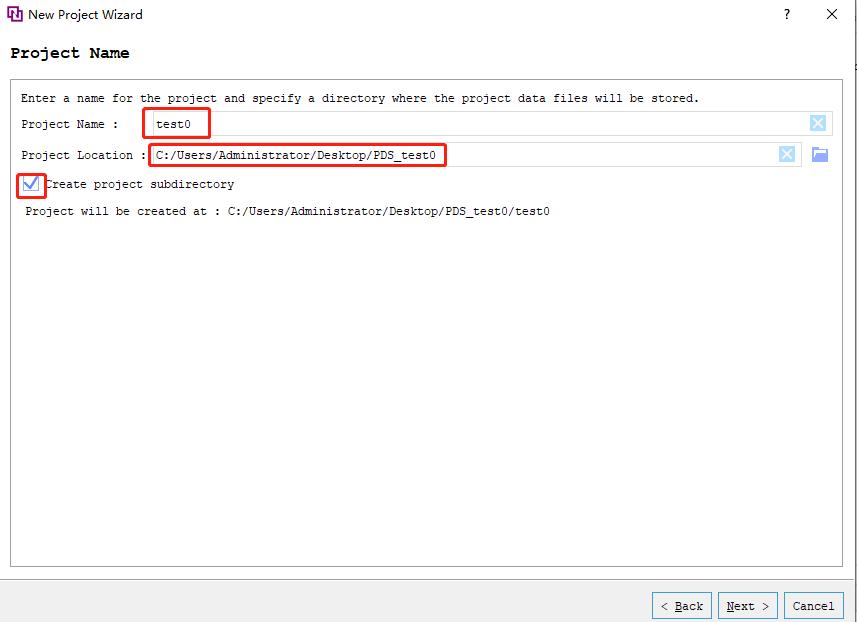

1.4、 在弹窗中输入工程名称和工程保存路径

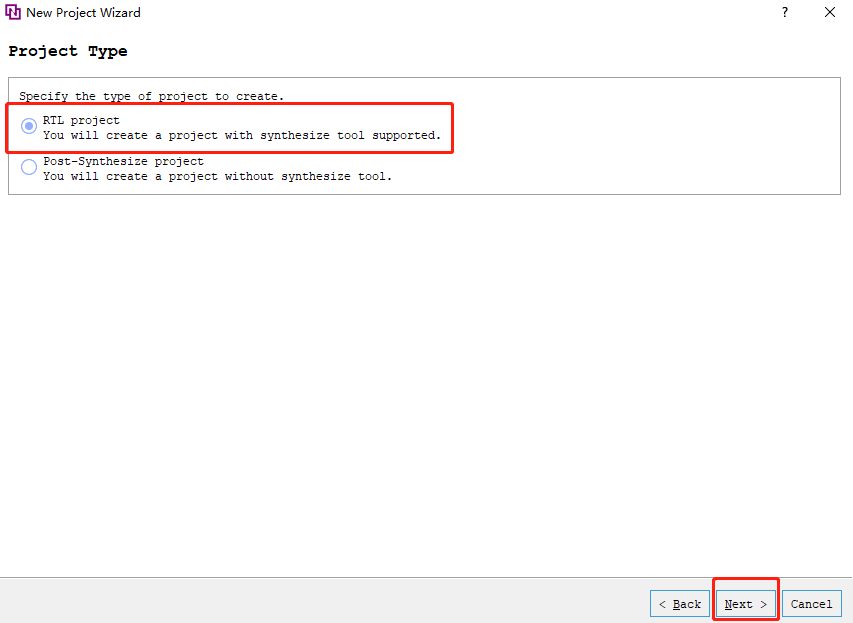

1.5、在弹窗中选择默认的RTL Project

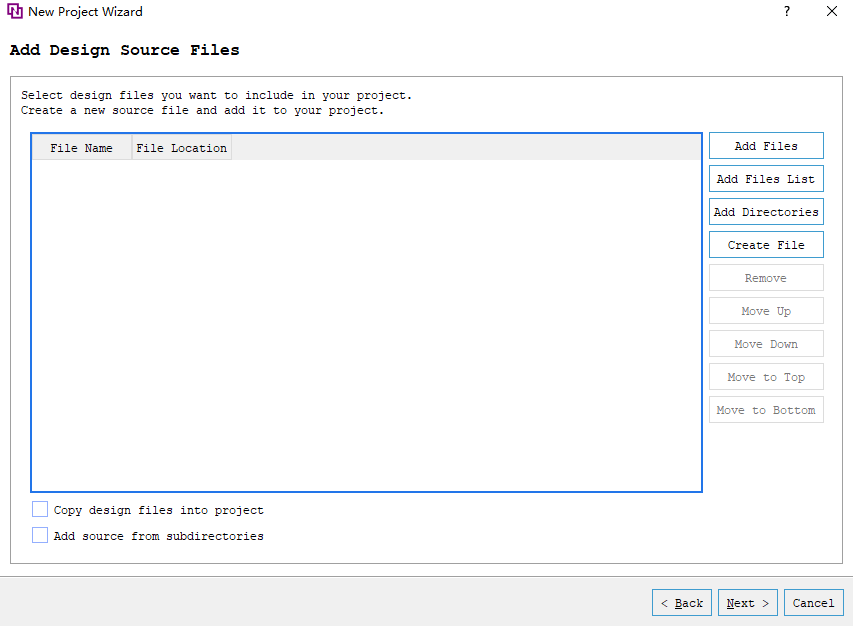

1.6、进入Add Design Source Files界面,先不添加任何文件。点击Next;

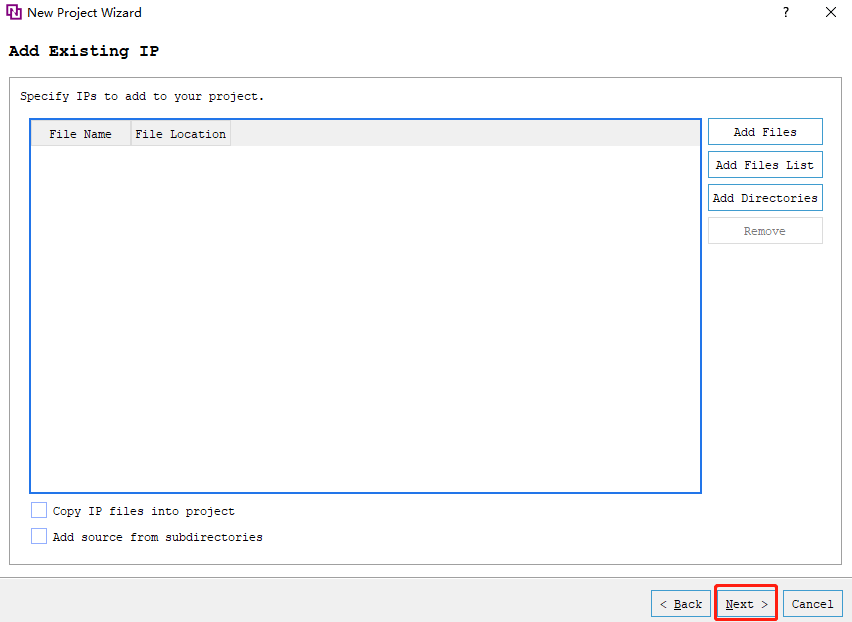

1.7、在弹出的添加IP窗口中,保持默认不添加,点击Next

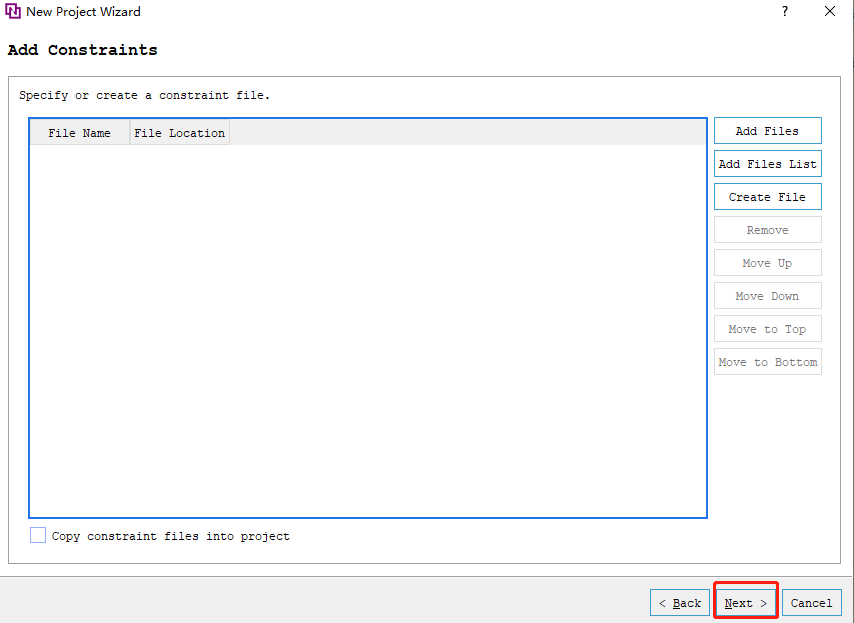

1.8、在添加约束文件弹窗中,也先不添加

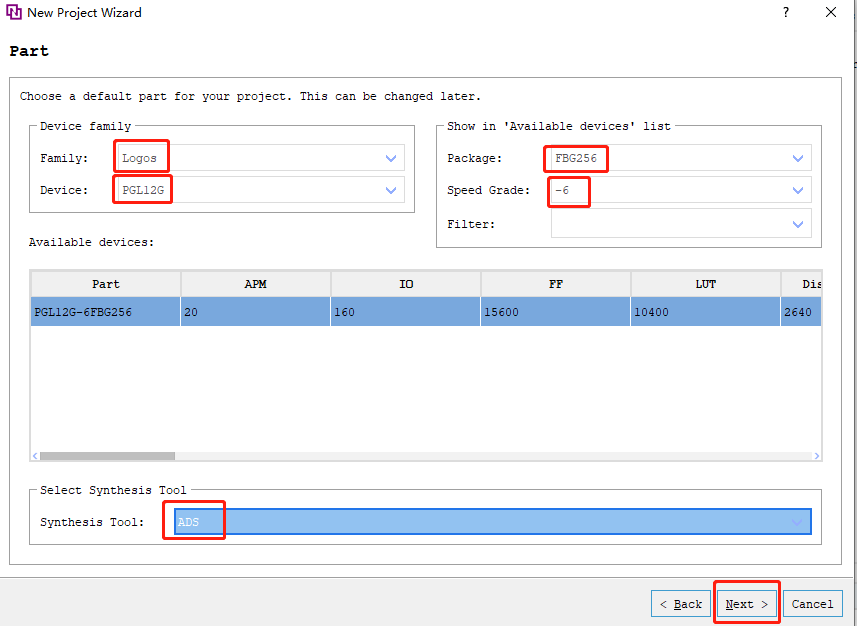

1.9、选择选用的FPGA器件,以及综合工具选择

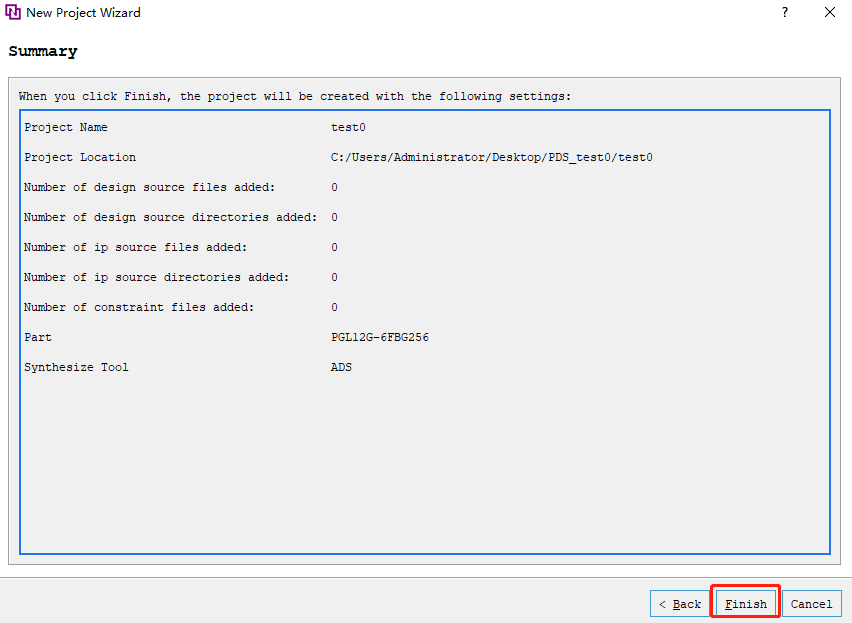

1.10、弹出工程的概要信息,点击Finish,工程创建完成

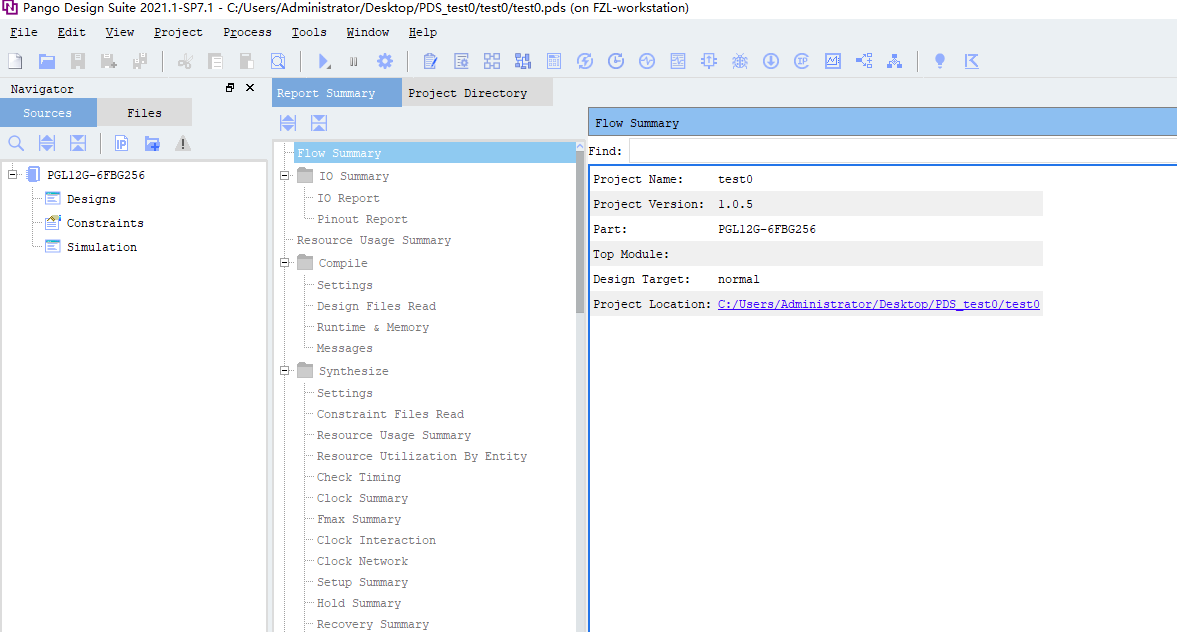

1.11、工程创建好的界面如下所示

2、添加源文件代码

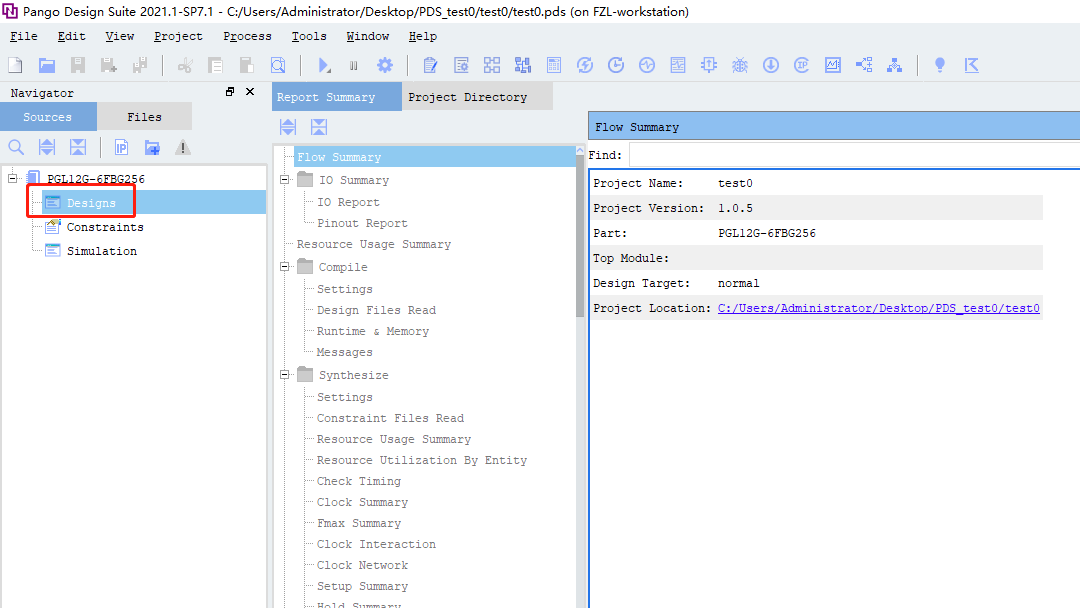

2.1、双击Sources下的Designs,或者右击Designs,点击Add Source

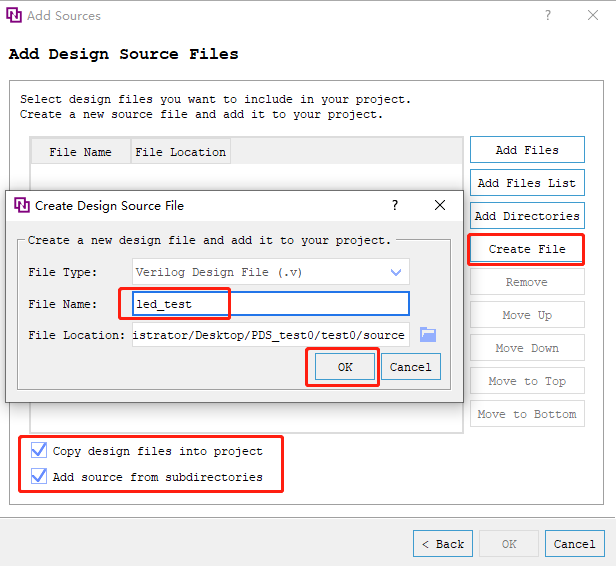

2.2、在Add Design Source File界面中进行如下设置,点击OK,OK

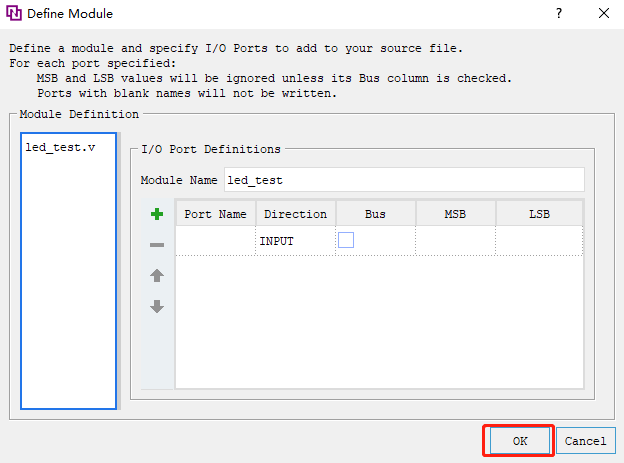

2.3、弹出的IO定义窗口,直接点击OK,以后可以在程序中编写

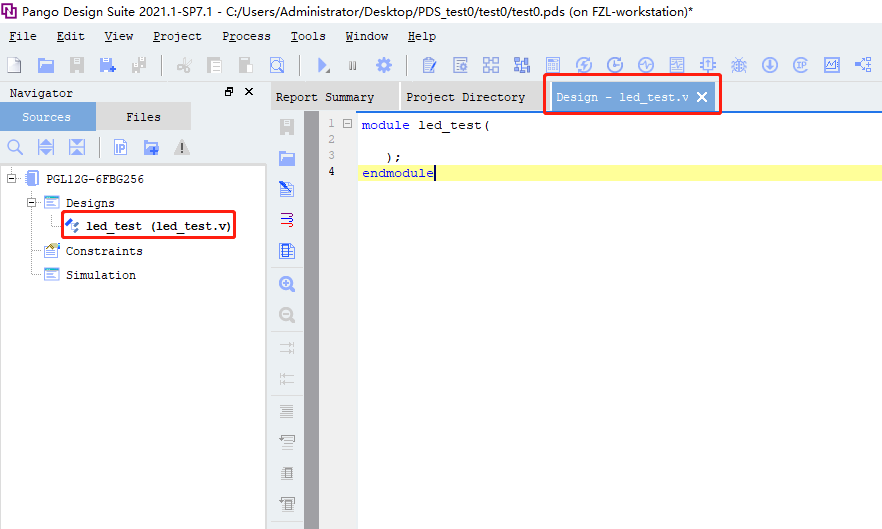

2.4、此时在Navigator--> Sources -->Designs下面就出现了.v文件

2.5、在led_test.v中添加代码,Ctrl +S保存

1 `timescale 1ns/1ns 2 module led_test( 3 sys_clk, 4 rst_n, 5 led 6 ); 7 8 input sys_clk; 9 input rst_n; 10 output [3:0] led; 11 12 reg [31:0] timer; 13 reg [3:0] led; 14 15 always @(posedge sys_clk or negedge rst_n) begin 16 if(~rst_n) 17 timer <= 32'd0; 18 else if(timer == 32'd199_999_999) 19 timer <= 32'd0; 20 else 21 timer <= timer + 1'b1; 22 end 23 24 always @(posedge sys_clk or negedge rst_n) begin 25 if(~rst_n) 26 led <= 4'b0000; 27 else if(timer == 32'd49_999_999) 28 led <= 4'b0001; 29 else if(timer == 32'd99_999_999) 30 led <= 4'b0010; 31 else if(timer == 32'd149_999_999) 32 led <= 4'b0100; 33 else if(timer == 32'd199_999_999) 34 led <= 4'b1000; 35 end 36 endmodule

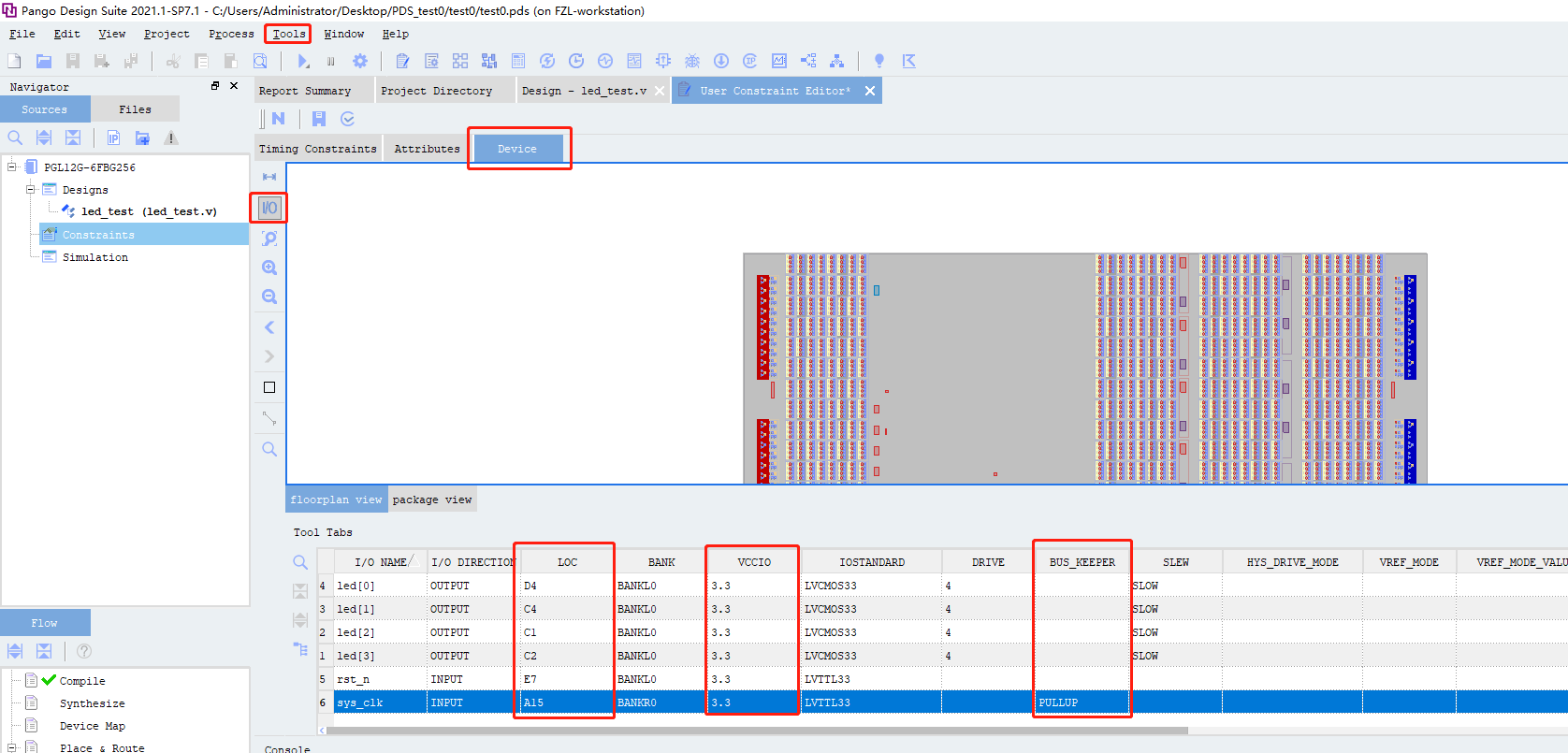

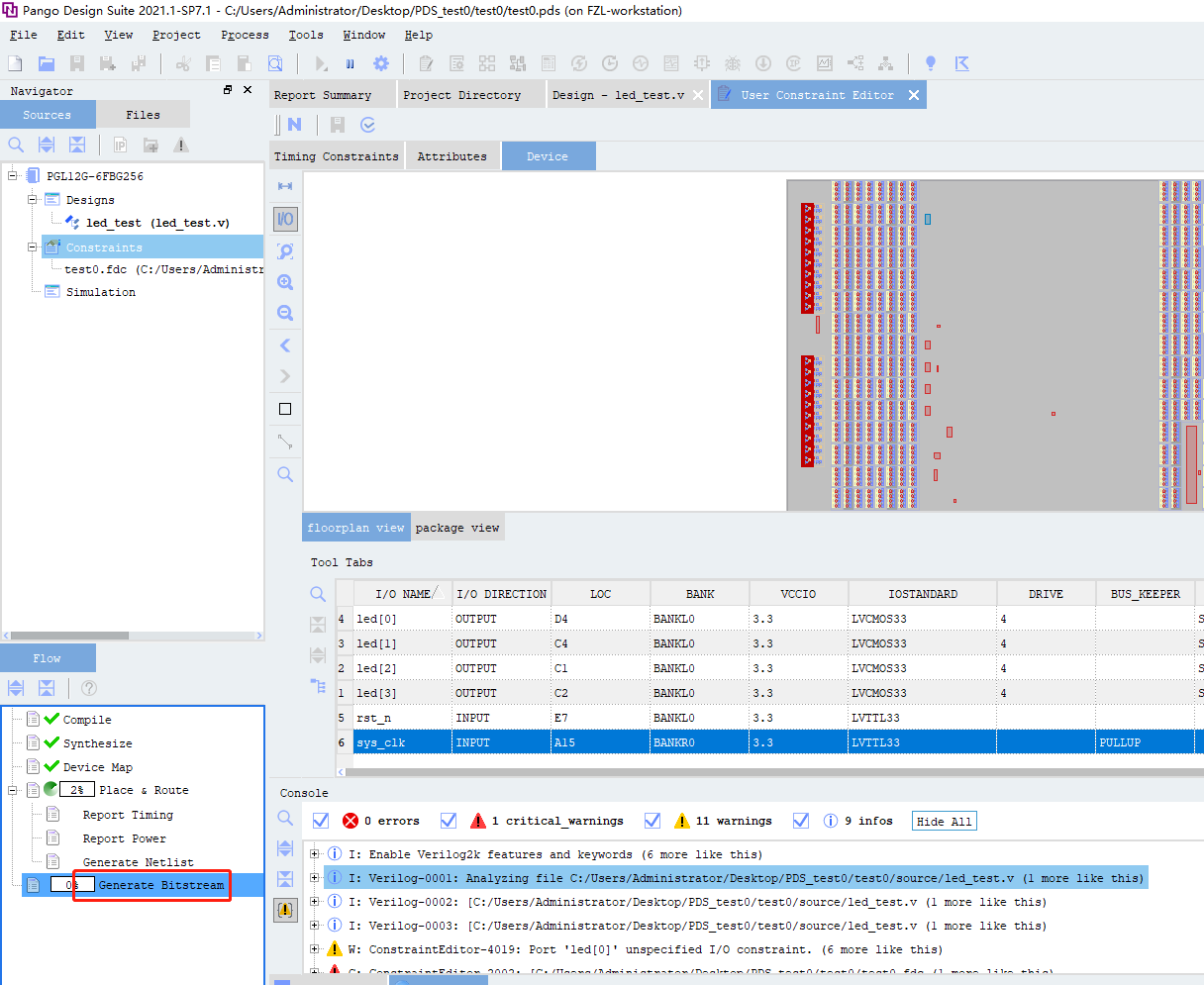

2.6、添加约束文件,就是时钟和管脚,点击Tools --> User Constraint Editor;

在弹窗中点击Device 、I/O、

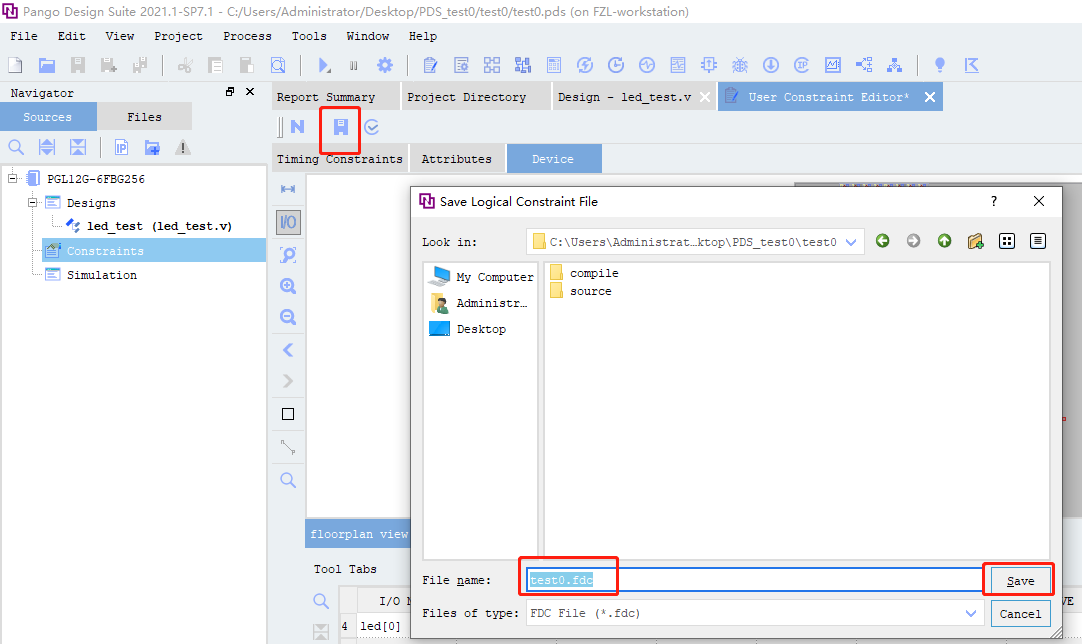

2.7、点击保存按钮,弹窗中内容保持默认

3、生成位流文件,也叫比特流文件

3.1 、直接双击 Flow窗口的Generate Bitstream;

软件会按照Synthesize -> Device Map -> Place & Route -> Generate Bitstream的顺序来产生位流文件

4、下载位流文件(在FPGA运行,掉电会消失)

4.1、JTAG下载器和电路板连接好,电路板上电

4.2、单击界面中的Configuration按钮

4.3、在弹出的界面中单击Boundary Scan,然后点击左上方的 Scan Device

4.4、在扫描到JTAG设备后,会弹出如下对话框,加载.sbit文件

4.5、点击选中芯片,右击会弹出下拉菜单,选择Program...开始下载

5、FLASH程序固化(掉电不会丢失)

5.1、将sbit文件转换成能下载flash的sfc文件,在上一节的基础上选择菜单Operations -->Convert File进行文件转换;

5.2、在弹出的界面,根据电路板上的flash型号来选择厂家和设备信息点击OK开始文件转换

5.3、转换完成之后,单击选中FPGA芯片,右击,在弹出的下拉菜单中选择Scan Outer Flash;

5.4、选择已经生成的sfc文件,点击Open

5.5、单击选中flash器件,右击,选择Program,开始将sfc文件固化到flash中

浙公网安备 33010602011771号

浙公网安备 33010602011771号