计组复习笔记

重点

•冯.诺依曼计算机型计算机的五大特点(p1)

•计算机系统的分类(SISD SIMD SIMD MIMD)

•计算机能够普及的主要原因

• 异或门在组成原理中的应用

•74LS181 4位超前进位加法器

•码制的转换、BCD码的概念,BCD码运算后需要修正、补码的双符号位表示

•计算机中数据的表示范围和精度

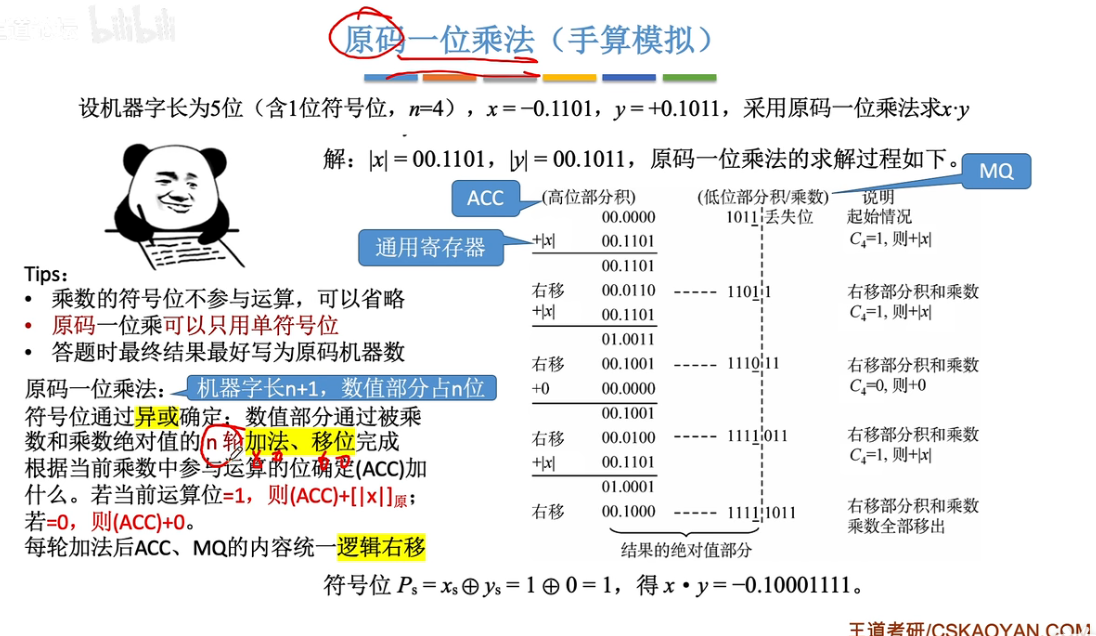

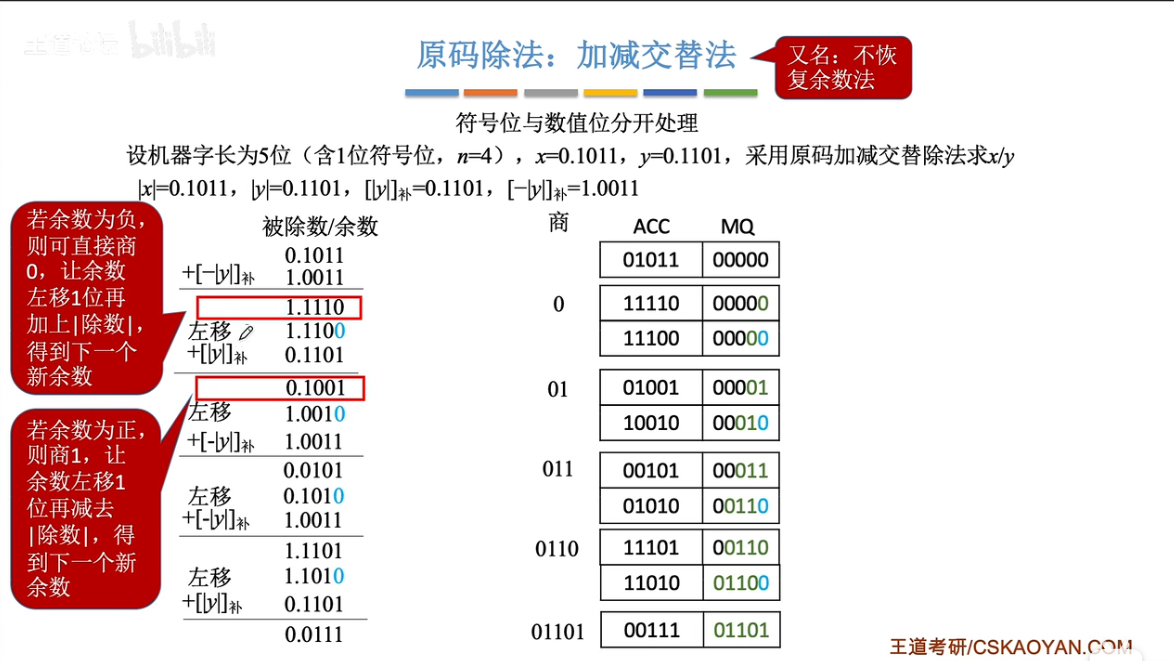

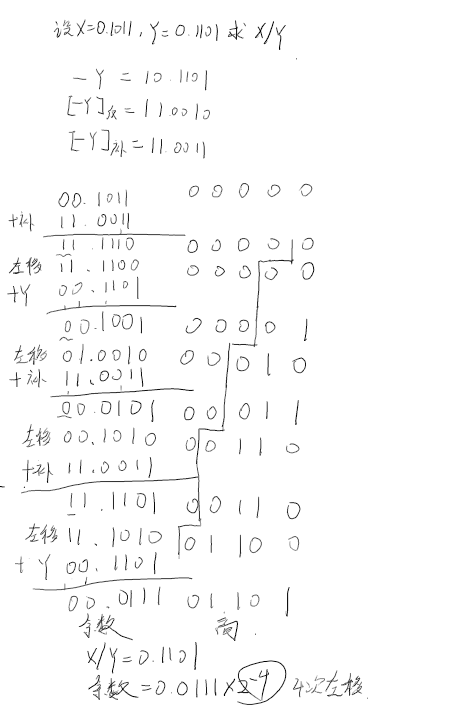

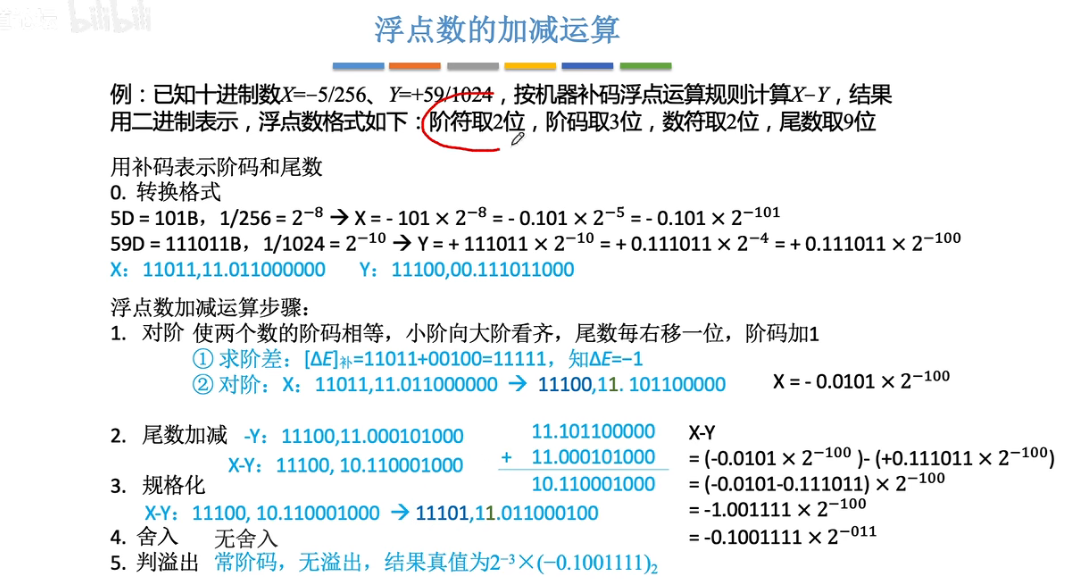

•原码一位乘、原码一位除(加减交替法);浮点数的加减法、乘除法运算(需 掌握步骤,会进行运运算)

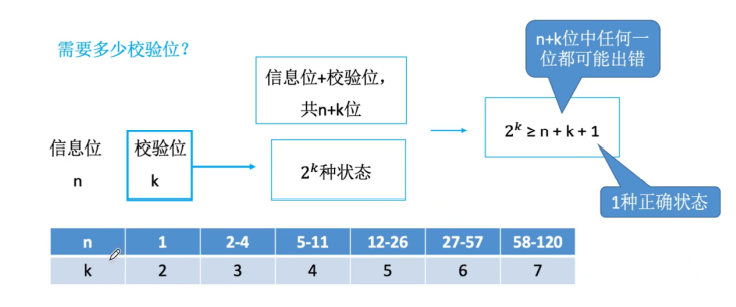

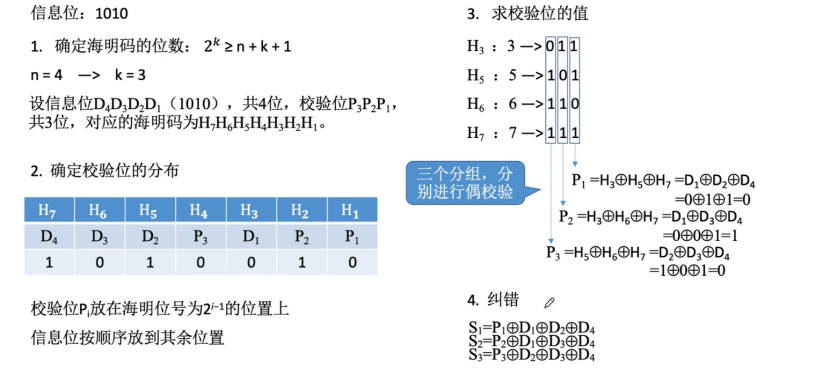

•掌握奇偶校验方法,会进行海明码、循环冗余校验码的编码

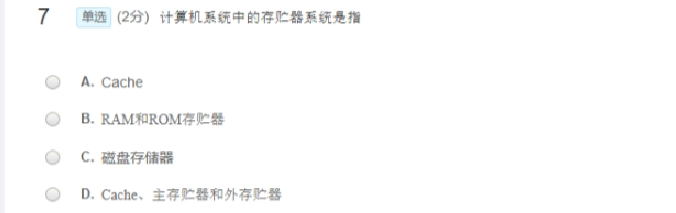

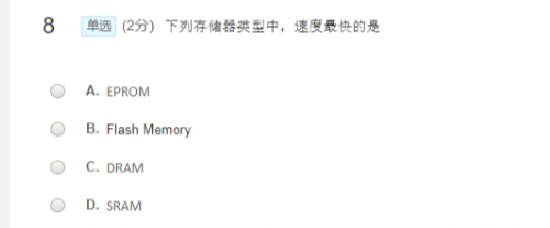

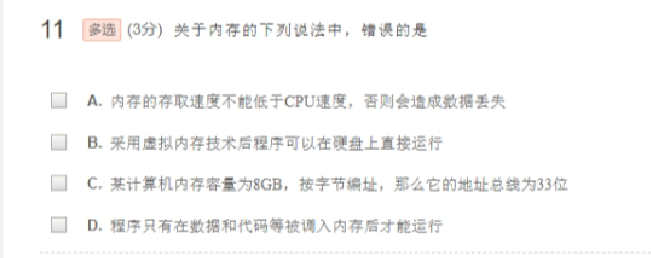

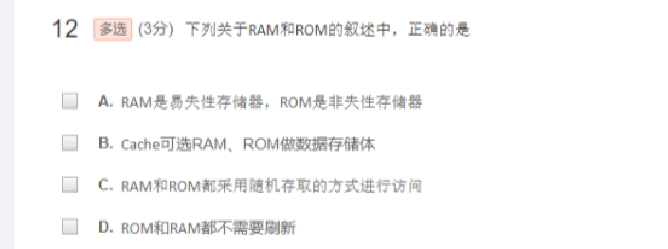

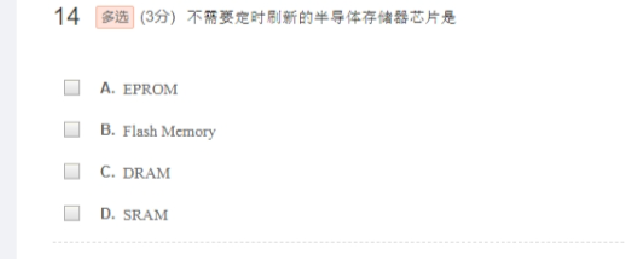

•掌握SRAM和DRAM的区别(从访问速度、集成度、单位价格、用途等方面进行比较);ROM与RAM的区别

•动态存储器的刷新(习题4.5)

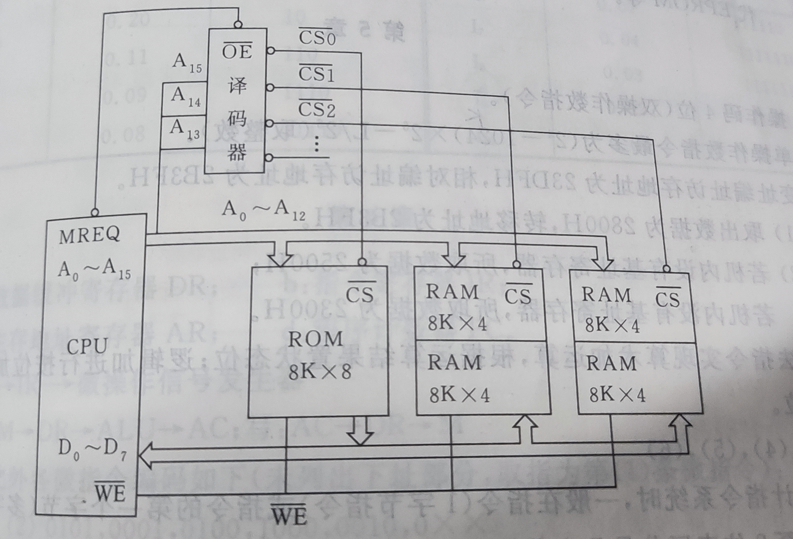

•存储器的扩展(类似于习题4.6)

• 多体交叉存储器

•指令的扩展(习题5.1)

•寻址方式( 5.9 )

•CISC和RISC的区别

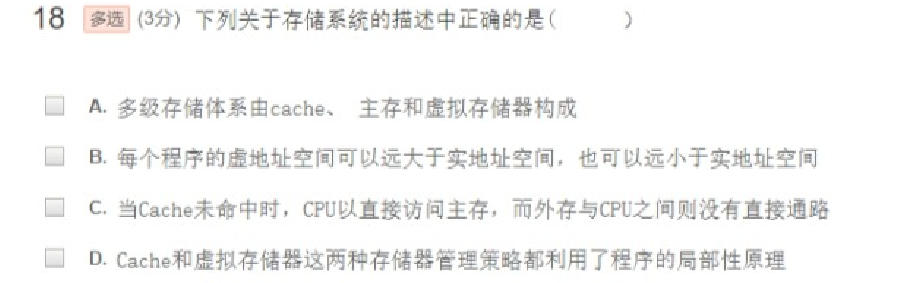

•写出给定指令对应微指令控制信号(习题6.2)

•指令、微指令、微命令的概念,它们之间的关系

•字段编译发每个控制字段位数的确定(习题*6.18)

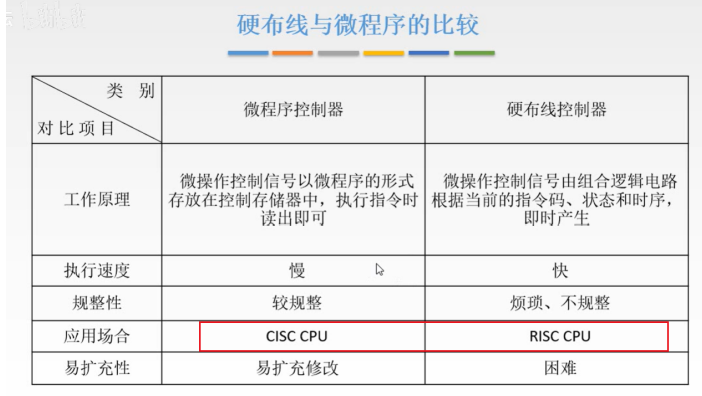

•微程序控制与硬布线控制的比较

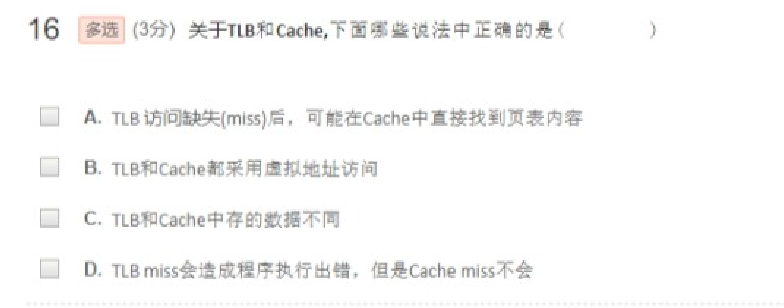

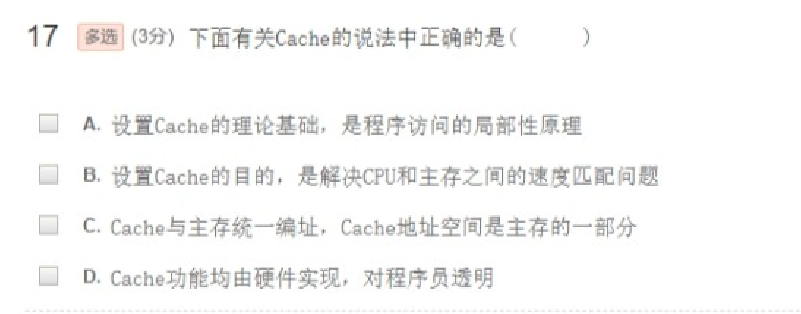

•Cache存储器与虚拟存储器的比较(目的、连接通路、评价指标)

•Cache/虚拟存储器的三种地址映像方式;主存和Cache不一致问题的解决(写直达法,写回法);等效时间的计算(习题7.3)

•虚拟存储器的快表和慢表(习题7.8)

冯.诺依曼计算机型计算机的五大特点

- 计算机硬件系统由五大部件组成(存储器、运算器、控制器、输出设备、输入设备)

- 指令和数据以同等地位存于存储器,可按地址寻访

- 指令和数据用二进制表示指令由操作码和地址码组成

- 存储程序

- 以运算器为中心

计算机系统的分类

按照指令和数据流可以分为:

- 单指令流和单数据流系统(SISD),即传统的冯·诺依曼体系结构。

- 单指令流和多数据流系统(SIMD),包括阵列处理器和向量处理器系统。

- 多指令流和单数据流系统(MISD),这种计算机实际上不存在。

- 多指令流和多数据流系统(MIMD),包括多处理器和计算机系统。

计算机能够普及的主要原因

微型机的出现与发展

异或门在组成原理中的应用

异或门是数字逻辑中实现逻辑异或的逻辑门,有多个输入端、一个输出端,若两个输入的电平相异,则输出为高电平1;若两个输入的电平相同,则输出为低电平0。1

异或门在组成原理中的应用有以下几种:

半加器 全加器

半加器是一种可以实现两个二进制数相加的组合逻辑电路,

它有两个输入端A和B,分别表示两个加数,

和两个输出端S和C,分别表示和与进位。

半加器的输出S可以用A和B的异或门实现,

输出C可以用A和B的与门实现。(https://zhuanlan.zhihu.com/p/148238633)

全加器是一种可以实现三个二进制数相加的组合逻辑电路,

它有三个输入端A、B和Cin,分别表示两个加数和前一位的进位,

和两个输出端S和Cout,分别表示和与进位。

全加器可以用两个半加器来实现,其中一个半加器先计算A和B的结果,然后把这个结果作为另一个半加器的输入之一,另一个输入为Cin

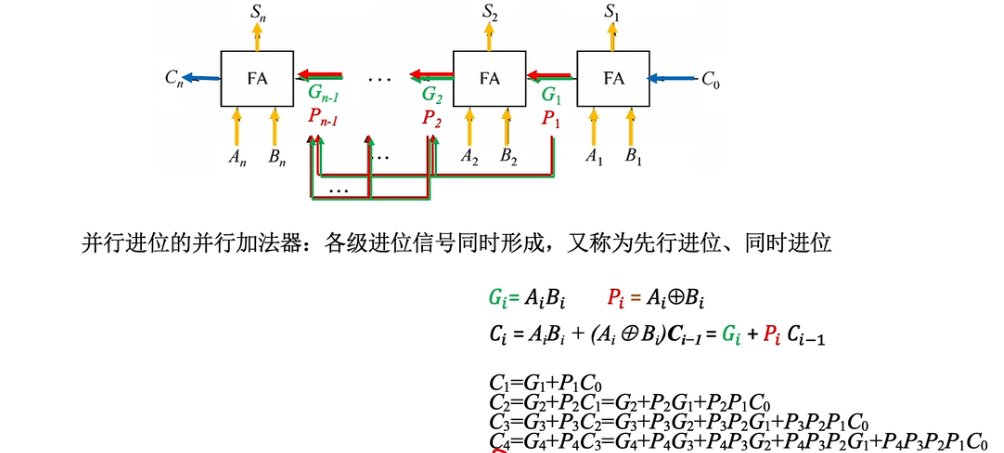

74LS181 4位超前进位加法器

超前进位加法器是一种优化了行波进位加法器的关键路径的组合逻辑电路,它可以几乎同时产生所有进位,而不像串行加法器那样依次产生。

A0 ──┬───────────────┐

│ │

A1 ──┤ ├──── S0

│ │

A2 ──┤ ├──── S1

│ │

A3 ──┤ ├──── S2

│ 74LS181 ├──── S3

B0 ──┤ ├──── Cout

│ │

B1 ──┤ ├── Cin

│ │

B2 ──┤ ├── Gout

│ │

B3 ──┴───────────────┴── Gin

A0-A3和B0-B3分别表示两个4位二进制数的输入端,

S0-S3表示和的输出端,

Cin和Cout分别表示低位和高位的进位输入和输出端,

Gin和Gout分别表示低位和高位的组合进位输入和输出端。

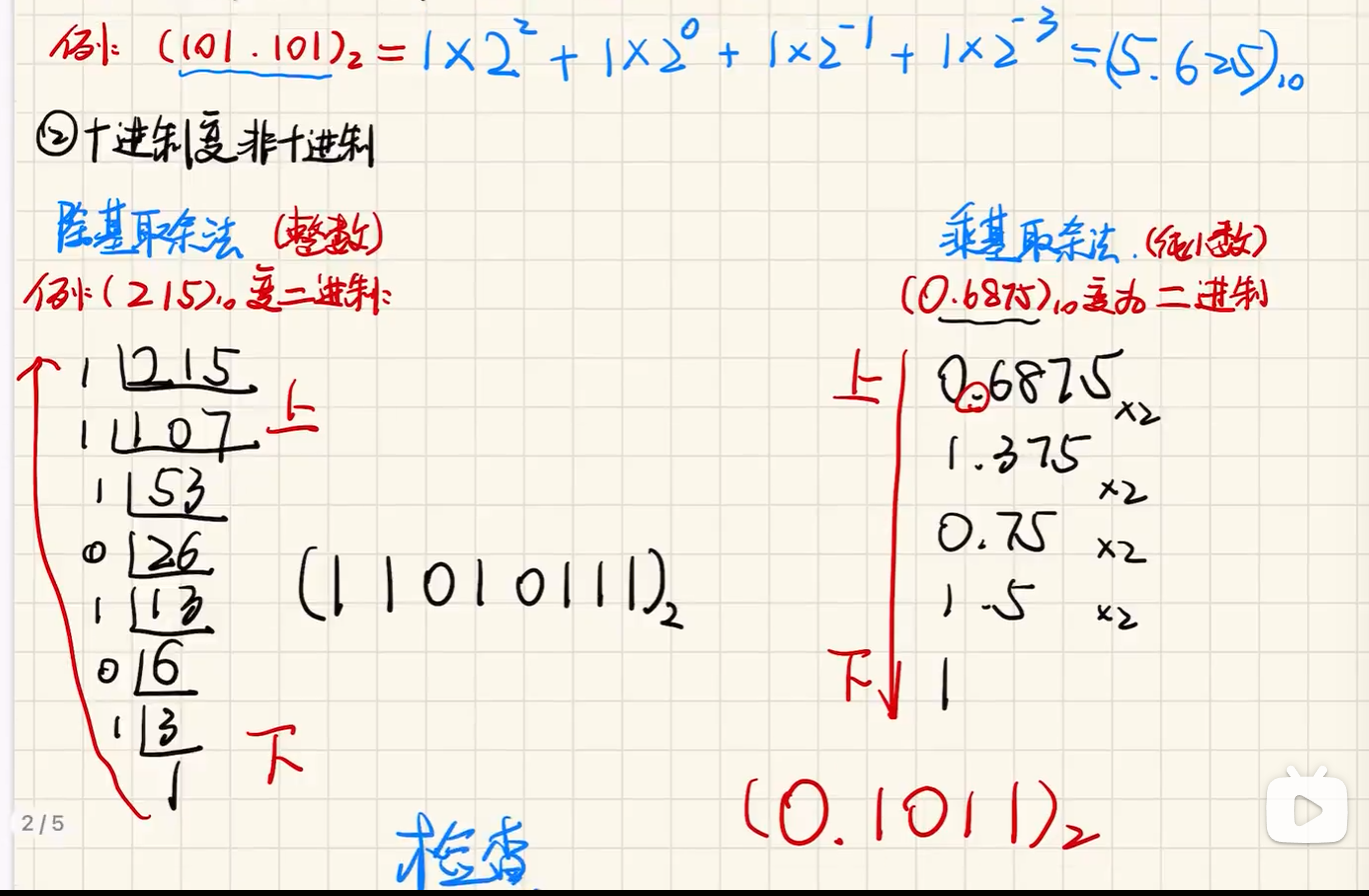

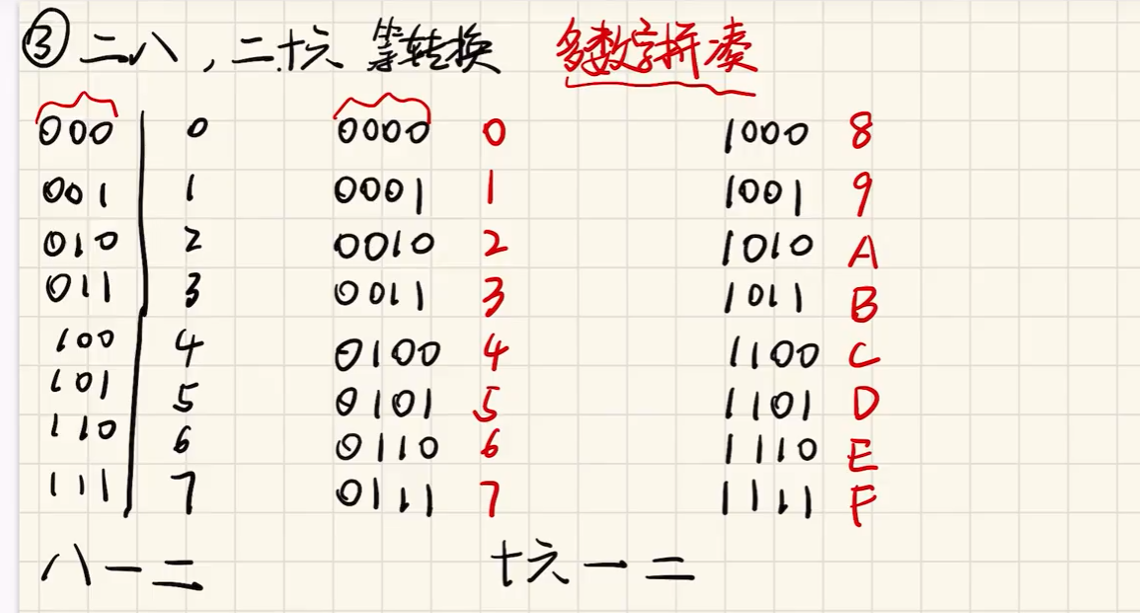

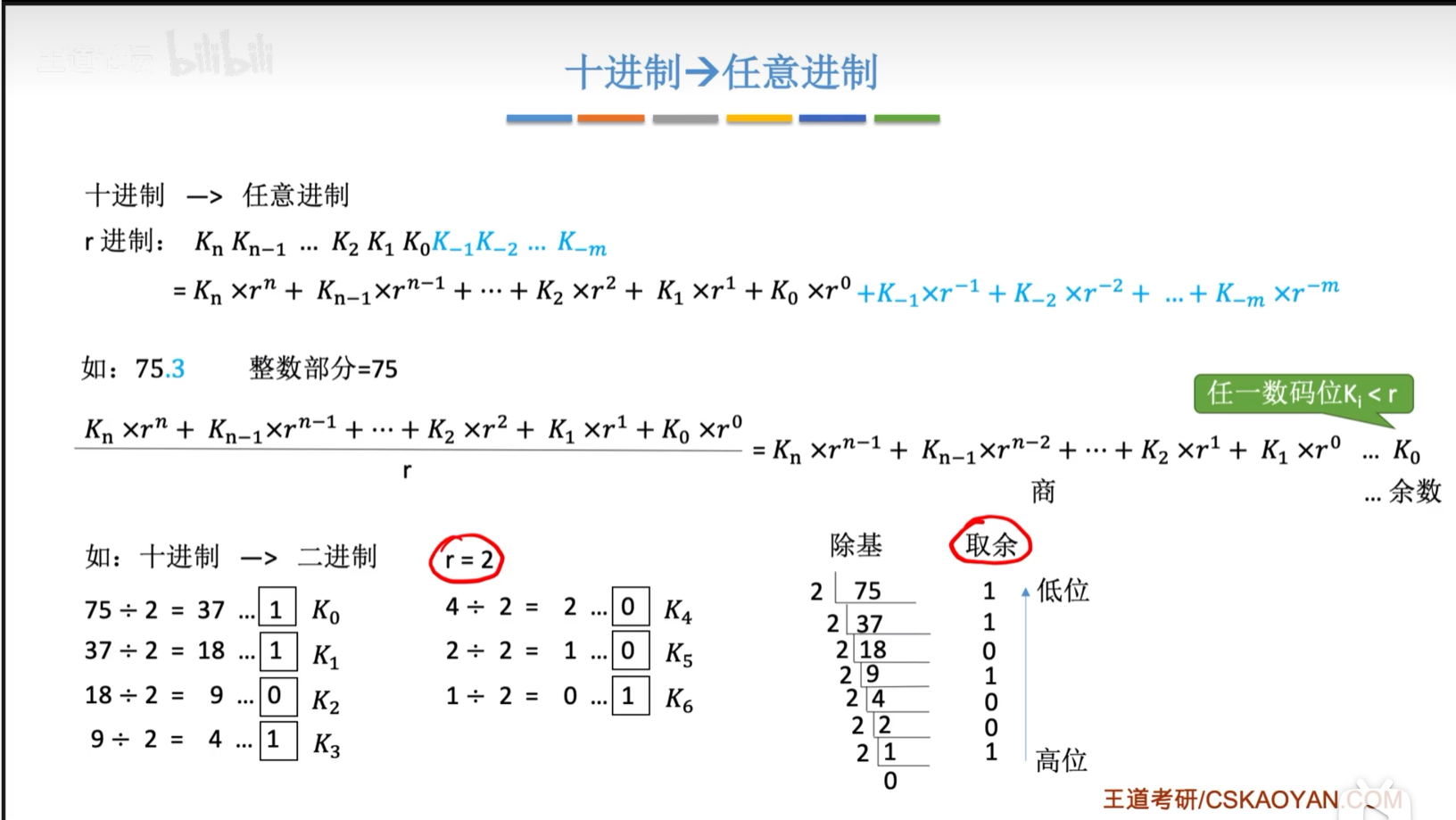

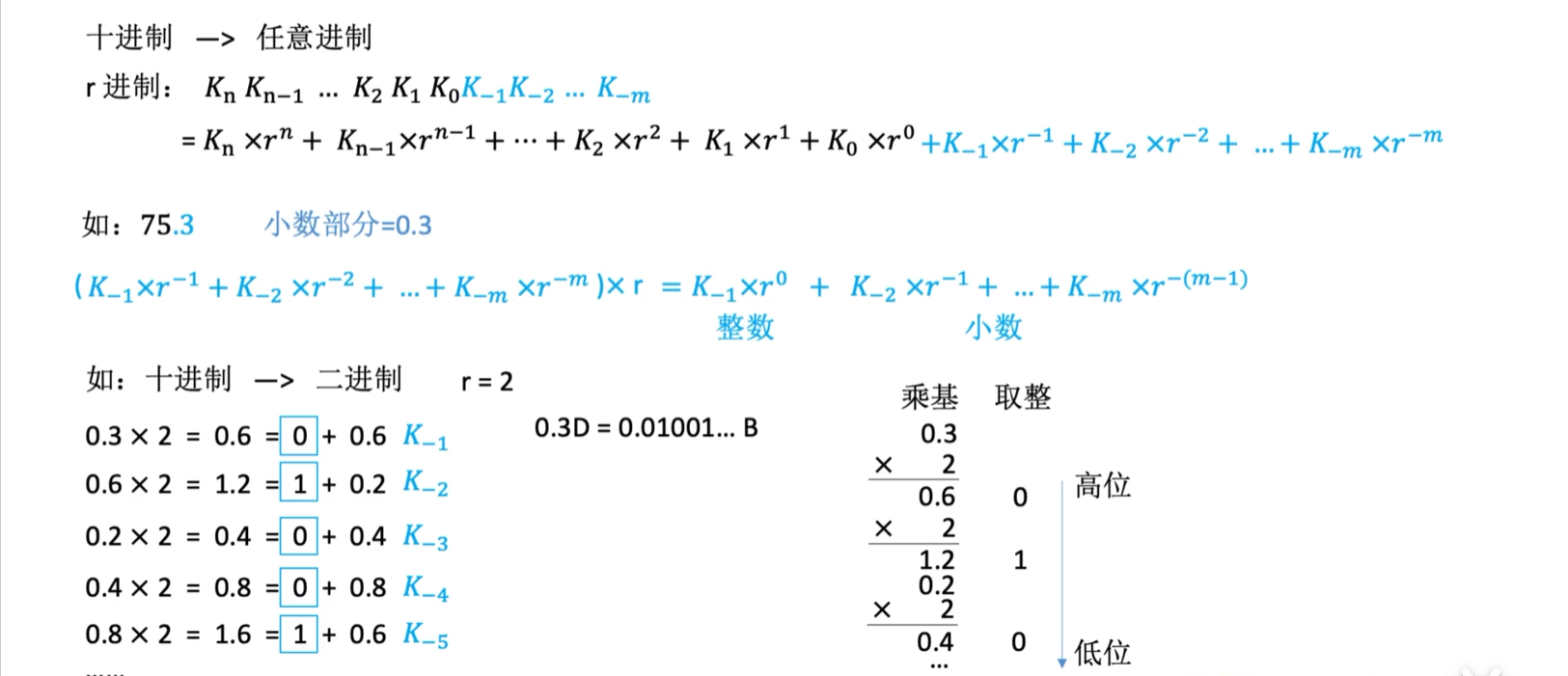

进制转换

原码 补码 反码

原码、反码和补码是计算机中存储数字的编码方式。原码就是符号位加上真值的绝对值,即用第一位表示符号,其余位表示值⁵。正数的原码、反码和补码是一致的;负数的补码是反码加1,反码是对原码按位取反,只是最高位(符号位)不变²。

源: 与必应的对话, 2023/3/1(1) 原码、反码、补码 - 知乎. https://zhuanlan.zhihu.com/p/118432554 访问时间 2023/3/1.

(2) 一文搞懂原码、反码、补码 - 简书. https://www.jianshu.com/p/36ec7a047f29 访问时间 2023/3/1.

(3) 二进制的原码、反码、补码 - 知乎. https://bing.com/search?q=原码+补码+反码 访问时间 2023/3/1.

(4) 【原创】什么是原码、反码、补码?_原码反码补码_赵大仁的博客-CSDN博客. https://blog.csdn.net/boyzhaotian/article/details/83790193 访问时间 2023/3/1.

(5) 原码,补码,反码之间怎么转换以及简单运算?-百度经验. https://jingyan.baidu.com/article/c85b7a649ec664003bac95e9.html 访问时间 2023/3/1.

(6) 原码,反码,补码相互转换在线计算器. https://www.23bei.com/tool/56.html 访问时间 2023/3/1.

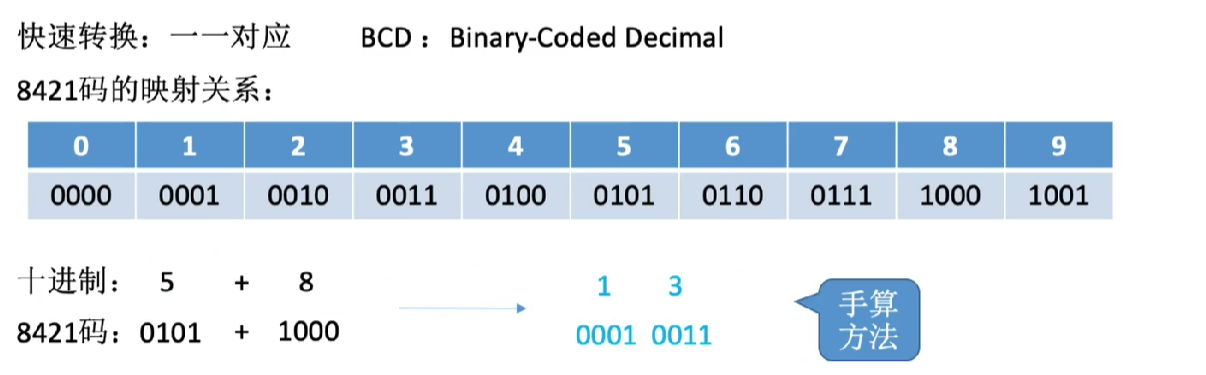

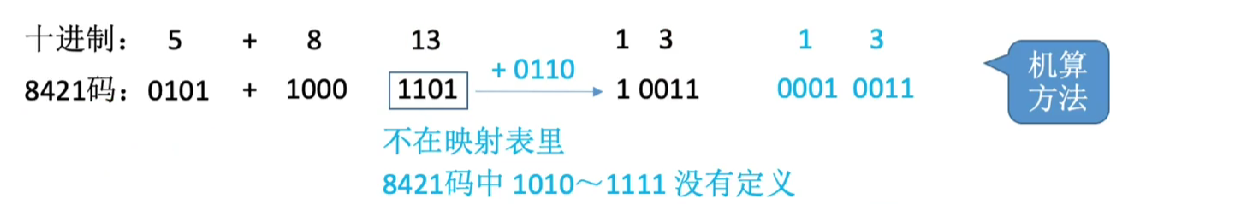

BCD码

用四位二进制码表示一个十进制数

8421码

有权码 固定二进制位权值固定

二进制相加后若范围不合法再加6

合法不东

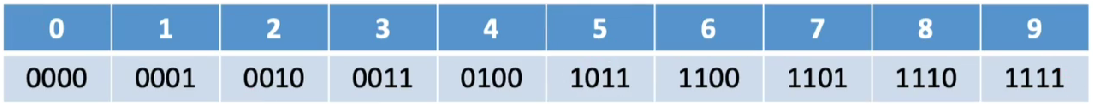

余三码

8421码加3

无权码

2421码

补码的双符号位表示

正数的双符号位为00

负数的双符号位为11

01为正溢出

10为负溢出

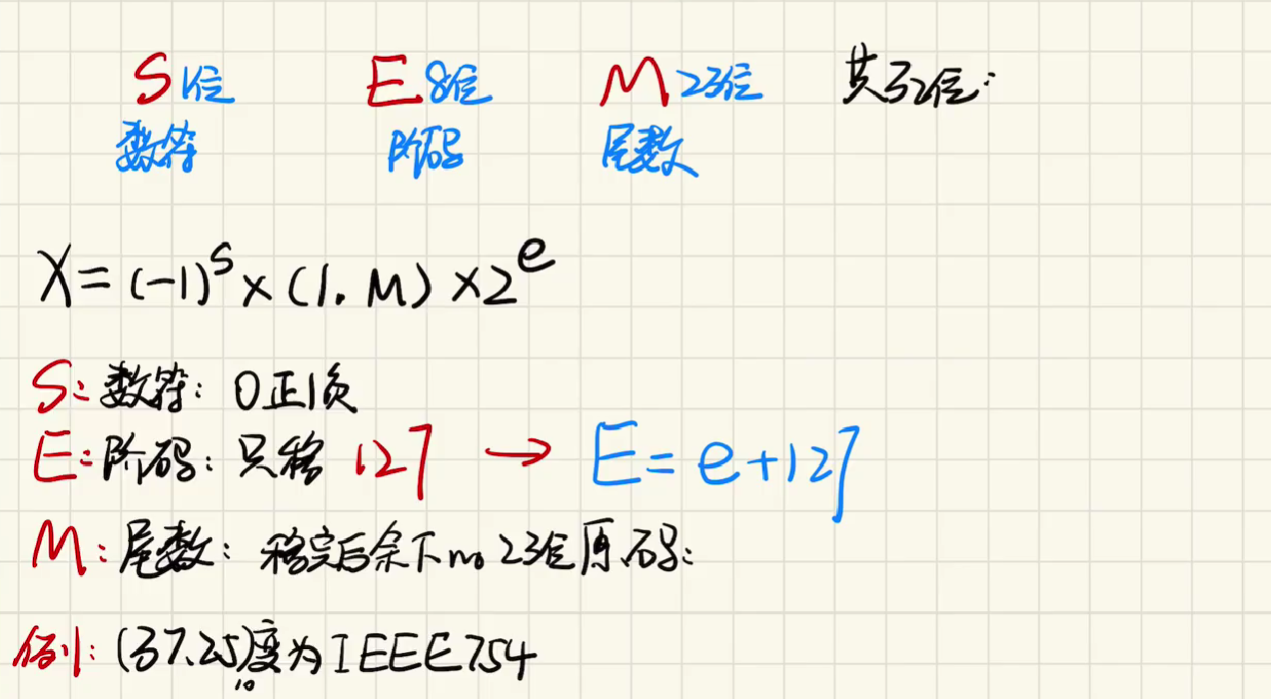

数据精度与范围

单精度浮点数 32位的

双精度浮点数 64位 阶码11位 尾数53位

=

计算机中数据的表示范围和精度是指机器所能表示的一个数的最大值与最小值间的范围,以及一个数的有效位数¹。数据的表示范围和精度受到机器字长和数据类型的影响²⁴⁵。机器字长是指计算机一次能处理的二进制位数,字长越长,数的表示范围也越大,精度也越高²。数据类型有定点数和浮点数两种,定点数是指小数点位置固定不变的数据,浮点数是指小数点位置可以根据需要而浮动的数据⁴⁵。浮点数又分为单精度浮点数和双精度浮点数,单精度浮点数占用4个字节(32位),双精度浮点数占用8个字节(64位)³。

源: 与必应的对话, 2023/3/1(1) 计算机组成原理学习之路(一)——数据表示_stepondust的博客-CSDN博客_求单精度浮点数43940000h对应的十进制数. https://blog.csdn.net/qq_44009891/article/details/107219217 访问时间 2023/3/1.

(2) 机器字长_百度百科. https://baike.baidu.com/item/机器字长/3220551 访问时间 2023/3/1.

(3) 计算机组成原理,浮点数的表示以及对其范围的理解 - 知乎. https://zhuanlan.zhihu.com/p/400006735 访问时间 2023/3/1.

(4) 图解计算机中的数值范围和浮点运算 - 冰河团队 - 博客园. https://www.cnblogs.com/binghe001/p/14337767.html 访问时间 2023/3/1.

(5) 浮点数的范围和精度_浮点数范围_Elec_z的博客-CSDN博客. https://blog.csdn.net/zuolindian/article/details/119082996 访问时间 2023/3/1.

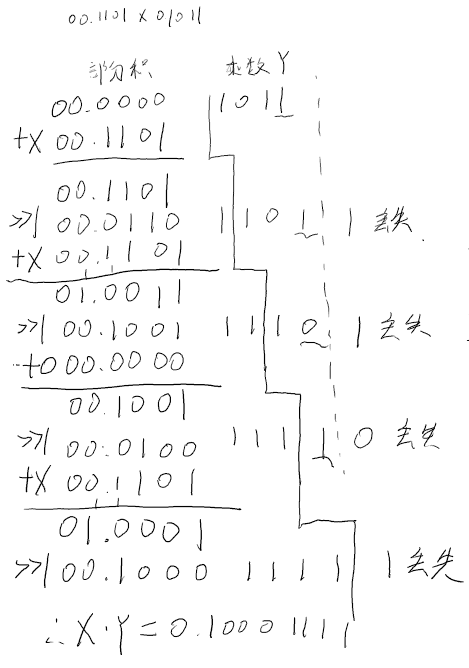

原码一位乘

不断右移

原码一位除 加减交替法

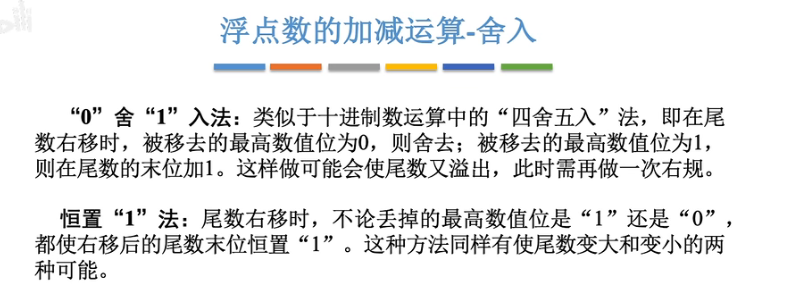

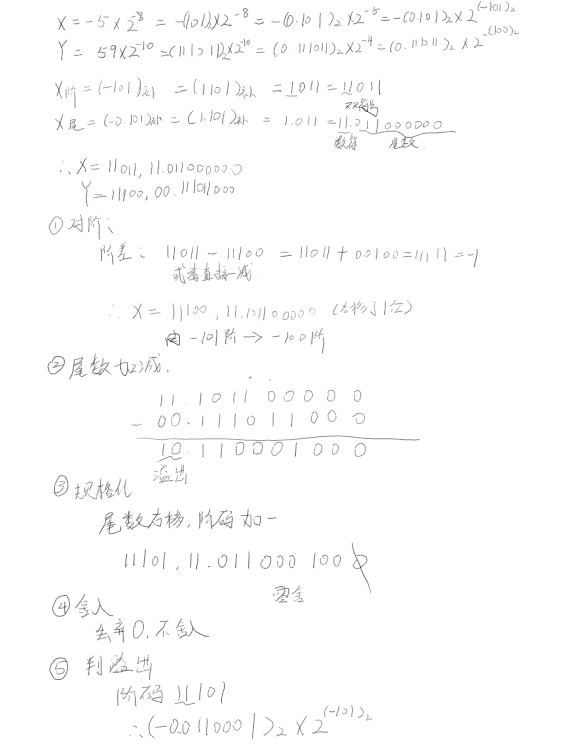

浮点数加减法

规格化:若用双符号位补码表示尾数 则最高两位应该为11或00

浮点数乘法

阶码为两者阶码的和

尾数直接相乘

规格化

判溢出

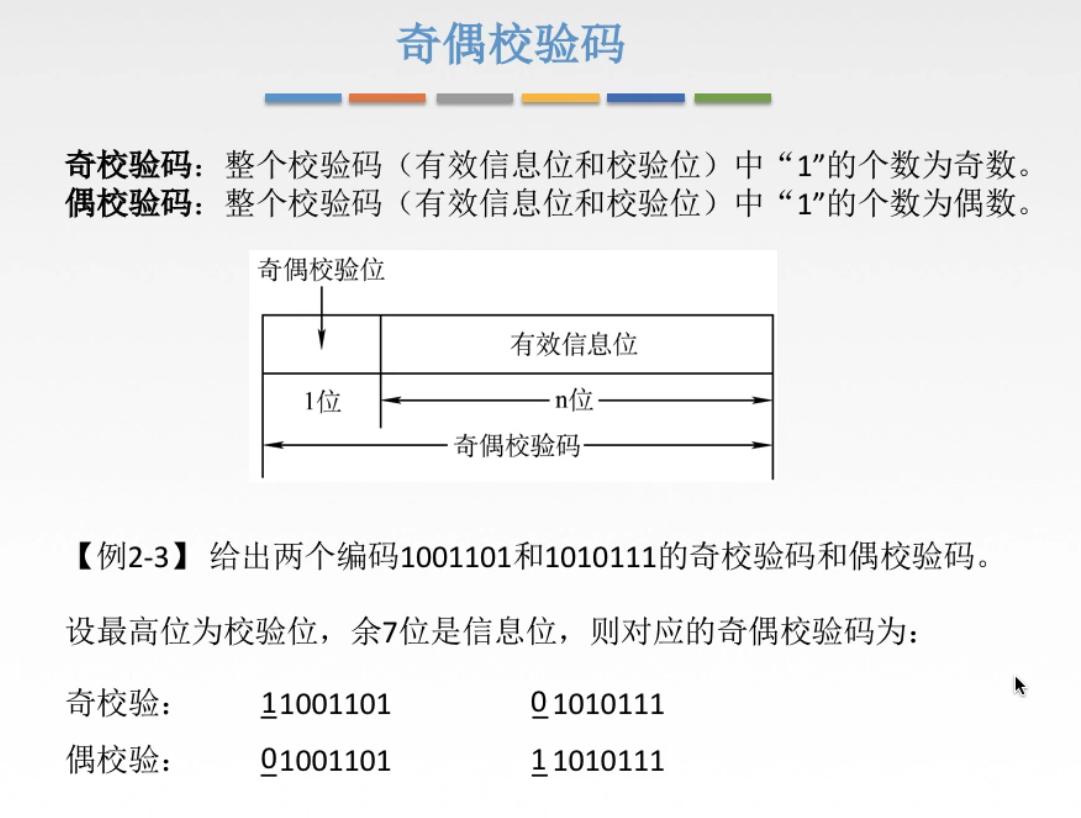

奇偶校验

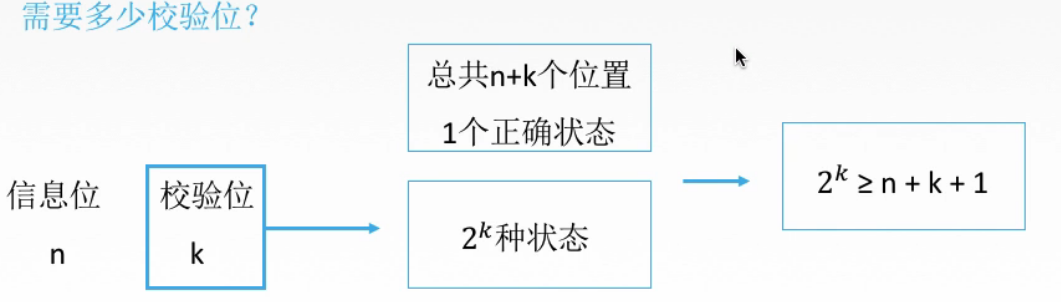

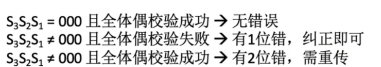

海明码

看明文对应位决定校验位的内容

如有三个纠错位就应该有三个纠错方程

纠错方程应该全为0

若多组不为0则看交集可知哪一位有错误

只可纠错一位 检错两位

最高位应有全体偶校验

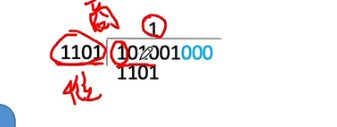

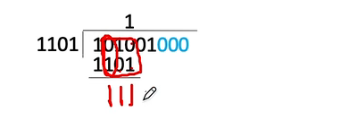

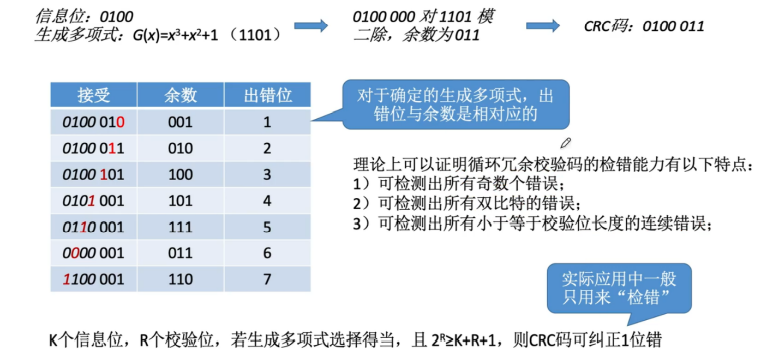

crc

规定生成多项式

将信息位左移生成多项式最高次幂后除以生成多项式(模2除)

模2除

高位为1则商1 为0则商0

剩下位数异或即可

每一层都如此

check

余数即为crc的校验位

信息位和余数拼接即为校验码

显然

正确的校验码一定整除生成多项式

SRAM和DRAM的区别 ROM与RAM的区别

SRAM的基本单元电路是由6个MOS管构成,

而DRAM的基本单元电路是由1个MOS管构成。

因此,SRAM的芯片引脚自然就多,功耗大,价格贵,速度快,散热大,所以集成度低¹。

相比之下,DRAM集成度高,容量能够做得很大⁵。

主要用途不同,SRAM因为其速度比较快一般用作Cache²³⁴。而DRAM因为相对比较便宜,所以比较适合作为主存²。

至于ROM与RAM的区别,在于ROM是只读存储器(Read Only Memory),数据写入后不能被修改;而RAM是随机存取存储器(Random Access Memory 动态存储器),可以随时读写数据。

源: 与必应的对话, 2023/3/2(1) DRAM与SRAM的比较_无言月梧桐的博客-CSDN博客. https://blog.csdn.net/WUYAN889/article/details/105484593 访问时间 2023/3/2.

(2) 一文读懂RAM、ROM、SRAM、DRAM、SDRAM等内存概念_Esdon6的博客-CSDN博客. https://blog.csdn.net/EastTao/article/details/99631355 访问时间 2023/3/2.

(3) SRAM和DRAM的优缺点对比_tlb用sram还是dram_Hydrion-Qlz的博客-CSDN博客. https://blog.csdn.net/qq_46311811/article/details/122355876 访问时间 2023/3/2.

(4) SRAM VS DRAM - 知乎. https://zhuanlan.zhihu.com/p/342809326 访问时间 2023/3/2.

(5) SRAM与DRAM有啥区别 - 知乎. https://zhuanlan.zhihu.com/p/358804777 访问时间 2023/3/2.

ram 刷新

一次刷新一行

集中刷新总时间是存取周期x行数

分散刷新总时间是(存取周期+读取周期)x行数

异步刷新时间间隔是2ms/行数

存储器的拓展

todo 笑死 也没看懂

多体交叉存储器

todo 没看懂

指令拓展

对应减去后乘法即可

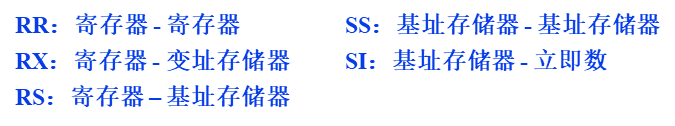

寻址方式

操作数在寄存器中为寄存器寻址

操作数地址在寄存器中为寄存器间接寻址

操作数在指令中称为立即数寻址

操作数地址(主存)在指令中为直接寻址

操作数地址为寄存器中内容与偏移量之和为基址寻址 变址寻址 相对寻址

CISC 与 RISC区别

CISC为变长指令集 主要为intel

RISC为定长指令集 主要为ARM

CISC的指令系统比较丰富,有专用指令来完成特定的功能,因此处理特殊任务效率较高。

RISC 设计者把主要精力放在那些经常使用的指令上,尽量使它们具有简单高效的特色。对不常用的功能,常通过组合指令来完成。

CISC硬件实现困难 软件实现简单 效率低 多个cpu周期

RISC硬件实现简单 软件实现困难 效率高 每条指令一个cpu周期

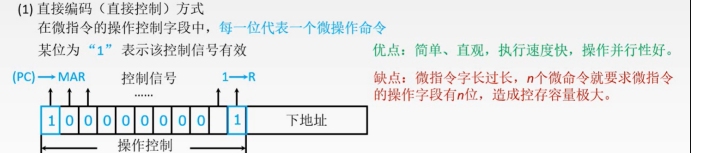

指令、微指令、微命令的概念,它们之间的关系

机器指令是计算机能够识别和执行的一条命令,它是提供给用户编程的最小单位。每条机器指令都能完成一项基本操作,例如数据传输、算术运算或逻辑运算。

微指令是微程序控制器中用来解释执行机器指令的一组命令。它是一组有特定功能的微命令的集合,通常用二进制编码表示。每条机器指令都由一段微指令编程的微程序来解释执行。

微命令是微程序控制器中用来控制计算机硬件操作的最小单位。它通常由一个操作码和若干个操作数组成,用来完成特定的硬件操作。

总之,在微程序控制器中,机器指令、微指令和微命令之间存在着密切的关系。每条机器指令都由一段由若干条微指令组成的微程序来解释执行,而每条微指令又包含了若干个具有特定功能的微命令。

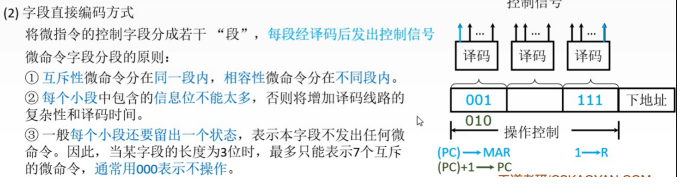

字段编译法每个控制字段位数的确定

有Ni个互斥型号

为 4 6 3 11 9 5 7 1 8 15

编码表示法

根据Ni个互斥型号求和

如Ni为4 则小于2^3次方 所以为3

所以 为 3 3 2 4 4 3 3 1 4 4 的和

完全水平型编码

4 6 3 11 9 5 7 1 8 15求和

微程序控制与硬布线控制的比较

微程序控制和硬布线控制是两种不同的微操作控制信号产生方式。在微程序控制器中,微操作控制信号从控制存储器读出;而在硬布线控制器中,微操作控制信号由组合逻辑电路即时产生²。

这两种方法各有优缺点。在微程序控制器中,指令的修改和扩充比较容易;而硬布线控制器的执行速度比较快²。此外,硬布线逻辑电路不规整,走线复杂而凌乱,一旦设计好,一般是无法修改的,添加和修改指令几乎是不可能的⁴。

源: 与必应的对话, 2023/3/2(1) 计算机组成原理知识梳理 - 知乎. https://zhuanlan.zhihu.com/p/37873947 访问时间 2023/3/2.

(2) 第六章 中央处理机(CPU)(第二讲)百度文库. https://wenku.baidu.com/view/3c29bdcc05087632311212a5.html 访问时间 2023/3/2.

(3) 第六章 中央处理机(CPU)(第二讲)百度文库. https://bing.com/search?q=微程序控制与硬布线控制的比较 访问时间 2023/3/2.

(4) 硬布线控制器和微程序控制器_百度文库. https://wenku.baidu.com/view/43b669e5366baf1ffc4ffe4733687e21ae45ff09.html 访问时间 2023/3/2.

(5) 中央处理器 —— 硬布线控制器和微程序控制器_微程序和硬布线_starter_zheng的博客-CSDN博客. https://blog.csdn.net/starter___/article/details/98736854 访问时间 2023/3/2.

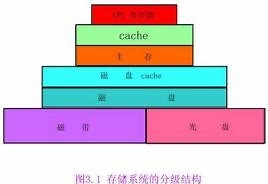

Cache存储器与虚拟存储器的比较(目的、连接通路、评价指标)

Cache存储器和虚拟存储器都是为了提高系统性能,但它们解决的问题不同。

Cache存储器解决的是速度问题,而虚拟存储器解决的是容量问题¹⁴。

Cache存储器完全由硬件实现,对所有程序员与操作系统透明

虚拟存储器由操作系统和硬件共同实现,是逻辑上的存储器,对系统程序员不透明,对应用程序员还是透明的¹²。

Cache是一个物理存储器,而虚拟存储器是一个逻辑存储器,其物理结构建立在主存-辅存的结构基础上。

源: 与必应的对话, 2023/3/2(1) 虚拟存储器和cache的比较 - 天凉好个秋秋 - 博客园. https://bing.com/search?q=Cache存储器与虚拟存储器的比较 访问时间 2023/3/2.

(2) 比较 Cache 和虚拟存储器,说明它们的相似点和不同。_小七月 搬砖记的博客-CSDN博客_比较cache与虚存的相同点和不同点. https://blog.csdn.net/weixin_40408952/article/details/105637748 访问时间 2023/3/2.

(3) 虚拟存储器和cache的异同_恒宝乐园的博客-CSDN博客_cache是虚拟存储器吗. https://blog.csdn.net/hengbao4/article/details/50128283 访问时间 2023/3/2.

(4) 虚拟存储器和cache的比较 - 天凉好个秋秋 - 博客园. https://www.cnblogs.com/juanzhi/p/12876058.html 访问时间 2023/3/2.

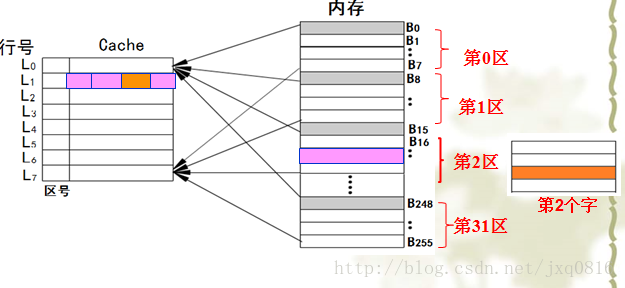

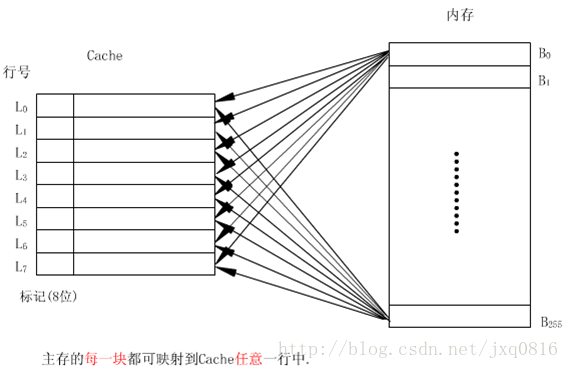

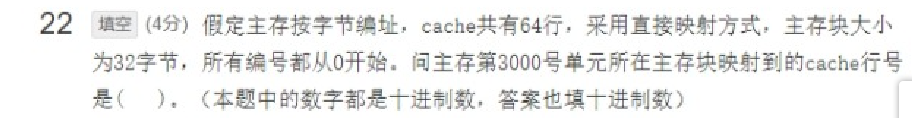

Cache/虚拟存储器的三种地址映像方式

Cache(高速缓存)的三种地址映像方式分别是直接映像方式、全相连映像方式和组相连映像方式¹。

直接映射(directmapping)

将一个主存块存储到唯一的一个Cache行。

多对一的映射关系,但一个主存块只能拷贝到cache的一个特定行位置上去。

cache的行号i和主存的块号j有如下函数关系:i=j mod m (m为cache中的总行数)

优点:硬件简单,容易实现

缺点:命中率低, Cache的存储空间利用率低

全相联映射(fullyassociative mapping)

可以将一个主存块存储到任意一个Cache行。

优点:命中率较高,Cache的存储空间利用率高

缺点:线路复杂,成本高,速度低

组相联映射(setassociative mapping)

可以将一个主存块存储到唯一的一个Cache组中任意一个行。

将cache分成u组,每组v行,主存块存放到哪个组是固定的,至于存到该组哪一行是灵活的,即有如下函数关系:cache总行数m=u×v 组号q=j mod u

组间采用直接映射,组内为全相联

硬件较简单,速度较快,命中率较高

主存和Cache不一致问题的解决

写回法:当CPU写cache命中时,只修改cache的内容,而不立即写入主存;只有当此行被换出时才写回主存。这种方法使cache真正在CPU-主存之间读写两方面都起到高速缓存的作用。对一个cache行的多次写命中都在cache中快速完成,只是需要替换时才写回速度较慢的主存,减少了访问主存的次数。实现这种方法时,每个cache行必须配置一个修改位,以反映此行是否被CPU修改过。当某行被换出时,根据此行的修改位是1还是0,来决定将该行内容写回主存还是简单丢弃。

全写法(写直达法):当写cache命中时,cache与主存同时发生写修改,因而较好地维护了cache与主存的内容的一致性。当写cache未命中时,只能直接向主存进行写入。全写法是写cache与写主存同步进行,优点是cache中每行无需设置一个修改位,以及相应的判断逻辑。缺点是,cache对CPU向主存的写操作无高速缓冲功能,降低了cache的功效。

写一次法(write--once):第一次写命中时写入主存,其他时候写回法

虚拟存储器相关

页表是将虚拟地址翻译成物理地址的重要组成部分。只有一级页表才需要总是在主存中,而二级页表可以在需要时创建,页面掉入或调出²。这就减少了主存的压力,只有最经常使用的二级页表才需要缓存在主存中²。

源: 与必应的对话, 2023/3/3(1) 多级页表内存_infralan的博客-CSDN博客_多级页表计算地址空间. https://blog.csdn.net/qq_43325061/article/details/119060604 访问时间 2023/3/3.

(2) 页表放在主存中,那么页表基址寄存器中存放的页表基址是虚拟基址还是主存中页表实际基址? - 知乎. https://bing.com/search?q=页表一定存放在主存中 访问时间 2023/3/3.

(3) 多级页表如何节约内存(转) - 简书. https://www.jianshu.com/p/83cca28be71d 访问时间 2023/3/3.

(4) 进程的页表存储在内存中还是磁盘里? - 知乎. https://www.zhihu.com/question/302312504 访问时间 2023/3/3.

页表的快表采取全相联查找,存在于cpu缓存中

计算机性能评价指标

IPC(instruction per clock);CPU每一时钟周期内所执行的指令数量;

MIPS:每秒处理的百万级的机器语言指令数;

CPI(Clock cycle Per Instruction):执行一条指令所需要的时钟周期数。

字长

CPI 与 MIPS 公式

CPI=(1/MIPS)/(1/f)

f为主频

时钟周期为1/f

0相关

0的原码补码都一样

寻址相关

32位等于4B

128mb/4B=32m个字

所以0-32m-1

按半字

错题

D

SRAM静态 更快

DRAM地址线为一半数量

ABC都错

ROM不需要刷新 也不能用作cache

SRAM静态

EPROM是rom

flash memory不刷新

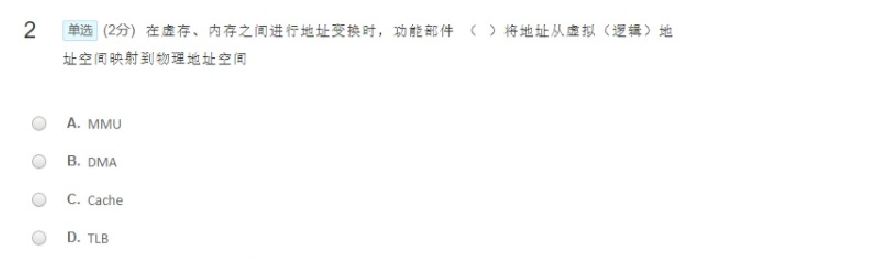

MMU(Memory Management Unit)内存管理单元

AC

ABD

BCD

(3000/32)%64

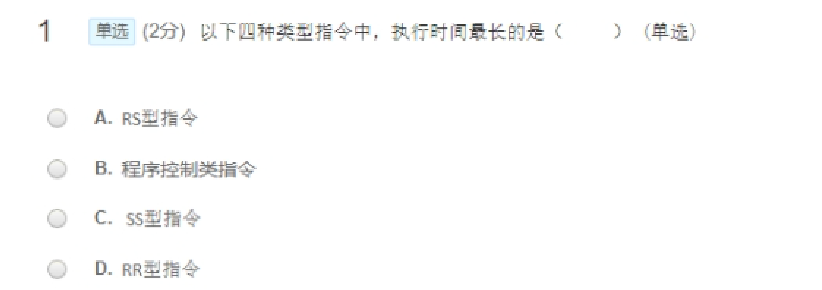

CPU访问速度从快到慢:寄存器,高速缓存,内存,硬盘,光盘,软盘。

所以选SS

A

浙公网安备 33010602011771号

浙公网安备 33010602011771号