转一篇DDR SDRAM 电源完整性分析

Project: MOTOROLA X??

Software:

CST PCB STUDIO (对电源完整性分析使用的是 CST PCB STUDIO 里的频域有限元法对电源平面进行建模)

Mentor HyperLynx PI

说明:

1: MTK 帮我们分析电源完整性是采用的 Sigrity(已被 Cadence 收购)。

2: MTK 做的电源完整性分析包括板级电源完整性和芯片级电源完整性。也就是说 MTK 做的 PI-阻抗分析是从芯片 On-Die 端看进去。

而由于我们缺乏芯片上的具体参数和模型,只能够做板级电源完整性,就是从电源引脚看进去的阻抗。

其实对于我们板级开发来说,做好板级电源完整性分析已经足够。至于芯片级电源完整性的好与坏,我们无能为力(那是芯片设计要处理的问题)。

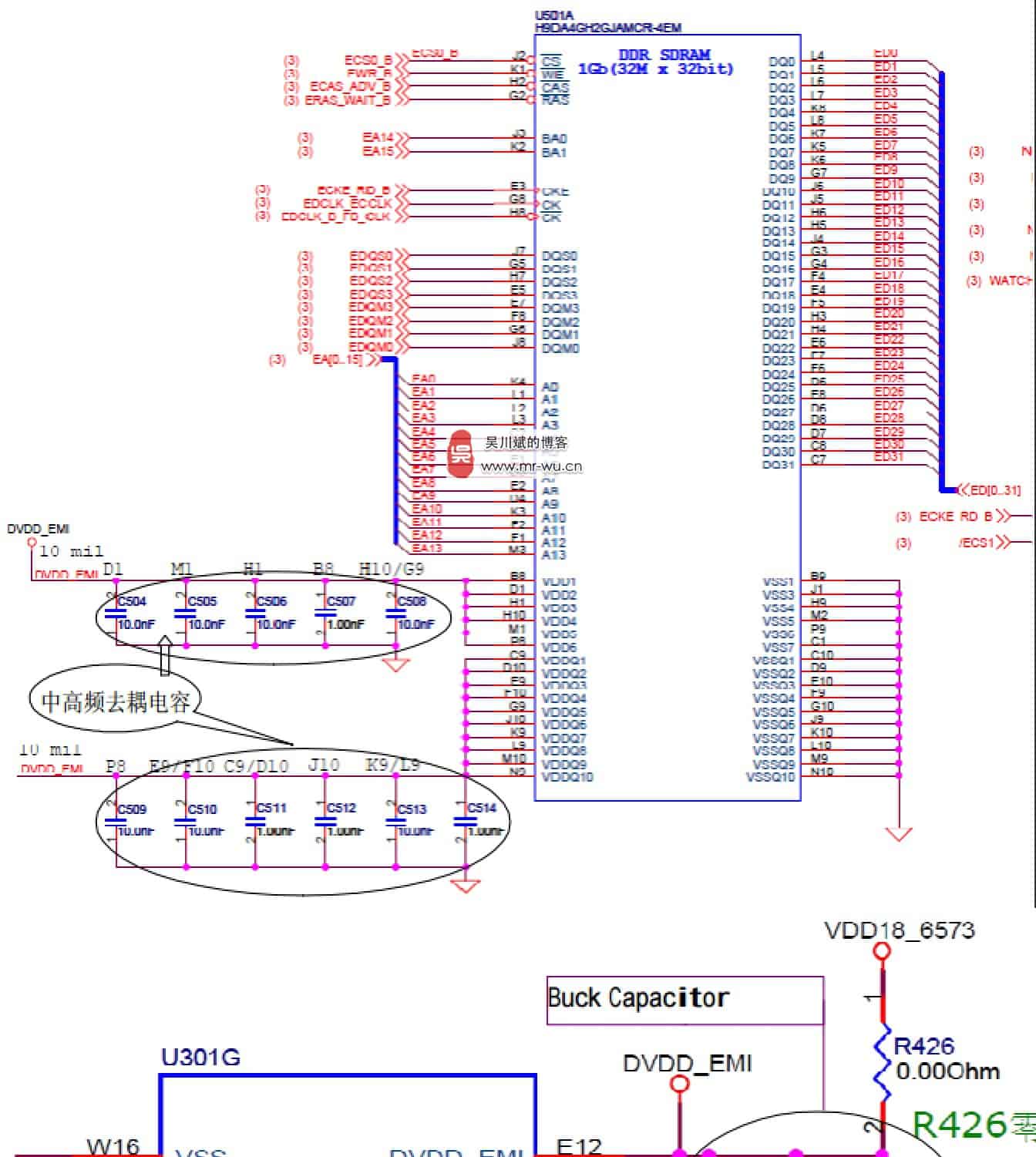

1). 电容 C504、C505、C506、C507、C508、C509、C5010、C511、C512、C513、C514 为去耦电容(中频去耦电容)。主要为电源平面(DVDD_EMI)提供低阻抗。

2). 电源平面本质上就是一个去耦电容(高频去耦电容,自谐振点SFR 位于 100Mhz 至 300Mhz 范围)。

3). 而体电容(Buck Capacitor,VRM 刚输出时电源引脚上的电容)为低频去耦电容。

Target Impedance:

Ztarget = (V*5%)/(I*50%)= 1.8V*5%/(0.37A*50%)=500momh(Worst Case)

Ztarget = (V*5%)/(I*20%or40%)=608momh 至 1.2 omh(都是可以接受的)

说明:

1. 目标阻抗比 MTK 给出的数值要小很多,是因为芯片的 WireBond 的寄生电感非常大,芯片上已有的片上去耦电容和片上电源平面也无法将阻抗拉低到板级的目标阻抗之下(片上去耦主要处理300Mhz 以上的 Transfer Impedance)。芯片上的电源完整性另有计算一套方法。

2. 去耦电容的阻抗(仅仅考虑去耦电容,电源平面不加以考虑)

上图的两根曲线,其中一根是将 C437 的 ESR=25mohm 和 ESR=2 mohm。仅仅影响低频。

3. 去耦电容和电源平面阻抗曲线的叠加

4. PDN 的阻抗(最终结果)

5. HyperLynx 分析 PDN 的阻抗(与 CST PCBS STUDIO 作比较)

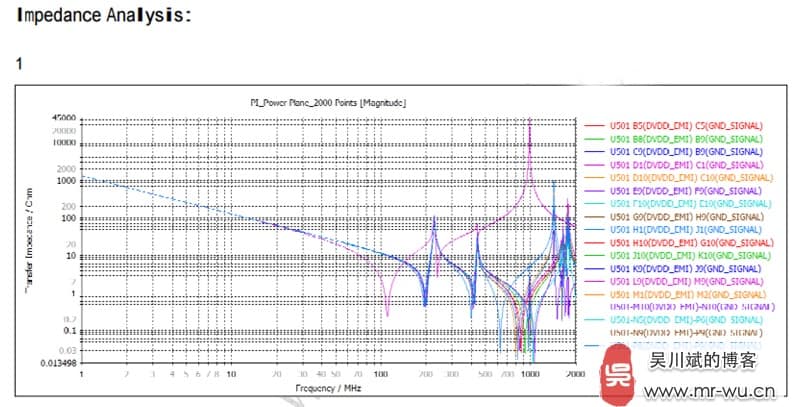

Results:

1. 由于 HyperLynx 在考虑去耦电容的 ESL 的时候,会综合考虑具体电路板的叠成等各种因素,而 CST PCB STUDIO 着需要根据具体的经验或者需要自己事先获悉具体的参数值,所以存在一定的不确定性。

2. CST PCB STUDIO 是基于频域有限元法。算法精度要比 HyperLynx 高

3. 二者的仿真结果的趋势总体保持一致,总体上满足目标阻抗。

浙公网安备 33010602011771号

浙公网安备 33010602011771号