Cadence Sigrity介绍

Cadence仿真利器,Cadence SI / PI Analysis

Sigrity提供了丰富的千兆比特信号与电源网络分析技术,包括面向系统、印刷电路板(PCB)和IC封装设计的独特的考虑电源影响的信号完整性分析功能。

Sigrity分析技术与Cadence Allegro和OrCAD设计工具的组合将会提供全面的前端到后端的综合流程,帮助系统和半导体公司提供高性能设备,应用千兆比特接口协议,例如DDR和PCI Express。

PowerSI-高效、精准的频域电源完整性及信号完整性分析工具

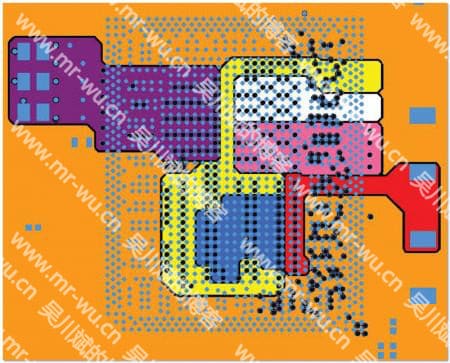

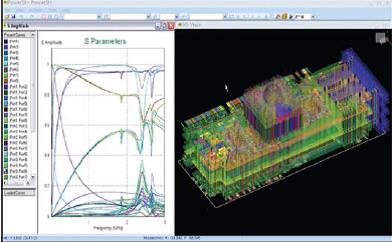

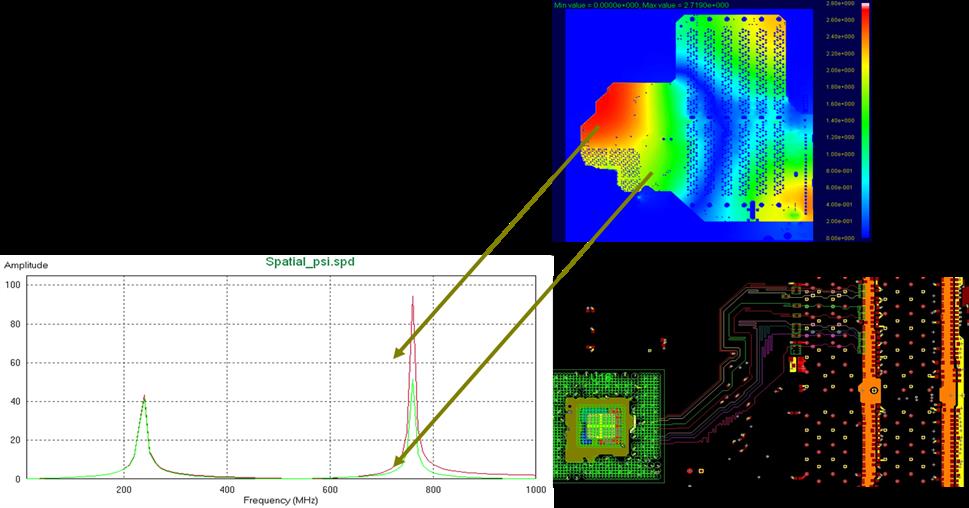

PowerSI主要用于分析IC封装和PCB设计在频域上的电源完整性和信号网络的电磁场分析,是基于有限元求解器、电路求解器和传输线求解器三合一的电路混合分析引擎,适用于10G以下的频域设计,可以提供电源和信号网络的模型参数(S/Y/Z)提取,分析信号布线引起的插入损耗和串扰特性,在空间模式下还能够分析电源的开/短路特性和谐振特性,对电源去耦电容布局位置的合理性进行评估,满足大多数的项目设计对电源完整性和参数提取的要求。

PowerSI利用独有的电磁混合仿真引擎能够高效准确地为设计人员提取信号或电源平面的网络参数(S/Y/Z),涵盖频段从DC至Ghz,并进行空间模式下的噪声分布及本征结构的谐振模式分析,在设计初期发现和定位设计中的各种风险及问题,给出准确直观的优化方向。最新的全波电磁分析引擎能够处理各种复杂的PCB/封装结构,在相同的仿真精度下,仿真速度比同类软件快10倍以上。

PowerSI可以为先进的集成电路(IC)封装及印刷电路板(PCB)提供快速、准确的全波电分析。

PowerSI对电子系统在频域中进行分析,非常适用于对集成电路的封装或印刷电路板进行整体电磁分析。

PowerSI使用了Sigrity公司独特的专利分析技术,在对平面上的分割、槽,多层电源/地结构,大量的通孔和走线等具体结构并在提取精确模型时使用了自适应的数值网格技术。

PowerSI的主要功能:

- 提取PCB板级和封装级电源网络与信号网络的阻抗(Z)参数及散射(S)参数,为精确分析电源和信号的性能提供依据。

- 分析板上任意位置的谐振特性,找出系统在实际工作时电源平面上的谐振及波动特性,为电源的覆铜方式及去耦电容的放置位置提供依据。

- 分析整板远场和近场的EMI/EMC性能,为解决板级的EMI/EMC问题提供依据。

PowerSI主要特点:

- 最大特色之一是,将电源网络和地网络当作非理想的情况来处理,考虑的是非理想的信号返回路径。

- 最大特色之二是,由于采用了混合仿真引擎(包含电路求解器、电磁场求解器和传输线求解器),因此仿真效率特别高,而且能够处理尺寸特别大、规模特别复杂的系统。

- 能够提取PCB板级和封装级电源网络与信号网络的阻抗(Z)参数及散射(S)参数,找出关键的谐振频率点分布,为精确分析电源和信号的性能提供依据。

- 能够分析板上任意位置的空间波动特性,为评估电源的覆铜方式及确定去耦电容的放置位置提供依据。

- 能够分析PCB的本征谐振模式,为分析PCB本身的结构特性提供依据。

- 能够分析整板远场和近场的EMI/EMC性能,为解决板级的EMI/EMC问题提供依据。

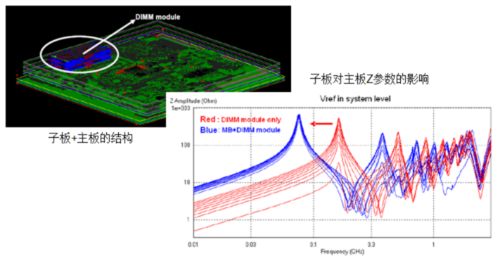

- 适用于布线前和布线后的 PI仿真,包含单板或多板。

- 评估和优化去耦电容的放置位置。

- 评估不同的电路模型对PI 性能的影响。

- 评估不同电路组成部分(平面,线,通孔)之间的电磁耦合。

- 分析敏感信号之间的隔离度强弱,为射频芯片的封装或高灵敏度的PCB设计提供指导。

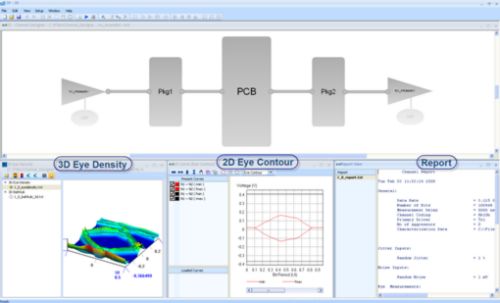

SystemSI-高效的串并行通道分析

面对更高速的10Gbps以上的高速通道Channel的通讯信号传输,大多数采用差分方式设计,这样可以持续更快速的传输大比特数据量,SystemSI的高速串行和并行模块,可以适应高速信号传输通道的标准分析流程,支持AMI算法建模接口,更便利创建发送端和接收端模型,同时内部的参数定义完全将芯片设计和业界高速传输标准(DDR3,4/HDMI/USB/PCI-E等)以流程化的设计方法提供给用户,最终满足用户对系统总体的误码率BER的预测,并判断抖动,噪声是都在指定的容限内,操作也是流程化的简单易用。

SystemSI的模块化设计允许用户方便的搭建任意拓扑,支持最新的IBIS/Spice/TouchStone/IBIS-AMI模型。SystemSI可以对高速串行通道进行眼图,误码率分析,对系统中的任意参数进行扫描,得到最优化配置,并且集成了PCI-E,SATA等工业标准,直接对仿真结果进行判别。SystemSI可以对整个DDR系统进行准确的SSO分析,集成JEDEC标准,自动为用户量测SI参数,并以此为基础,进行自动的时序分析。

用SystemSI评估端对端串行通道的性能可以快速的对设计方案进行取舍。对于多个串行通道的设计,可以通过高效的总线扫描功能自动化分析可行的方案。

SystemSI能够判断10Gbps以上的设计中串扰对抖动的影响。SystemSI可以支持奇模、偶模、最差和随机串扰分析。相邻的信号网络可以用同相、反相和随机的方式打开或关闭。在支持通道设计快速改进的同时,SystemSI还可以评估IC芯片信号处理和时钟数据恢复(CDR)的效果。

SystemSI主要用于处理高速数据通道,仿真时可以模拟出几百万bit的数据进行仿真,并能充分考虑从DC到10Gbps以上的串行通道数据传输设计,提供了很高精度的仿真,准确清晰的显示了误码率评估数据,在设计高速的串行通道时非常有用。

SystemSI主要功能:

- 仿真高速串行通道误码率(BER)

- 应用IC芯片的AMI发送端和接收端模型

- 仿真10Gbps以上设计中的抖动和噪声

- 评估IC芯片的信号处理和时钟数据恢复(CDR)的效果

- 用图表形式表示信道的特性

- 精确的仿真通道中的S参数模型

- 通过总线草庙高校的分析多个串行通道

- 利用通道仿真模板和通用的AMI模型来进行快速仿真

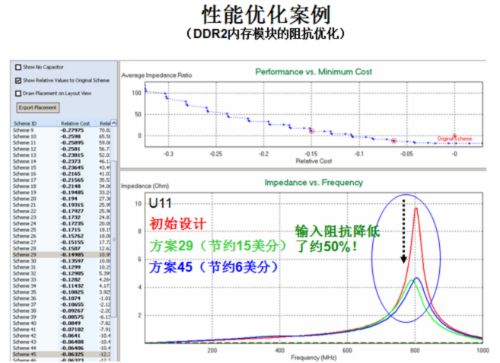

OptimizePI-自动化的成本性能优化平衡工具

OptimizePI是业界第一款自动化的性能与成本优化工具,允许用户直接选择最佳性价比,最佳性能等优化目标,OptimizePI将为用户从海量的组合方案中选出最符合优化目标的方案供用户选择,用户也可以进行What-i分析,动态评估PDN性能与成本的关系。最新的版OptimizePI也提供EMI电容的优化。

Optimize PI是针对PCB和封装的频域仿真工具,通过前仿真和后仿真实现电容方案的选型和优化,进而提高系统或器件的性能。它能够帮助设计者综合考虑PCB或封装的电源分配网络(PDS)去耦电容的性能和成本。通常可以节省15%到50%的成本,通过分析可以确保系统或器件的PDS实现最佳性能。Optimize PI基于Cadence的电磁场电路混合引擎并结合专有的优化算法,帮助用户快速得到最佳的电容波方案及布局方案。

Optimize PI主要特点:

- 自动选择和放置去耦电容

- 减小PCB 和IC 封装中去耦电容的过设计

- 减小新老产品设计中PDS的成本

- 制定出高效的去耦电容的设计规则

- 重新获得不需要的去耦电容所占据的设计区域

- 动态评估PDS 成本和性能

- 结合PCB和封装优化PDS性能

- 创建最低成本、最佳性能的去耦电容放置表

- 确定EMI电容的数量和位置

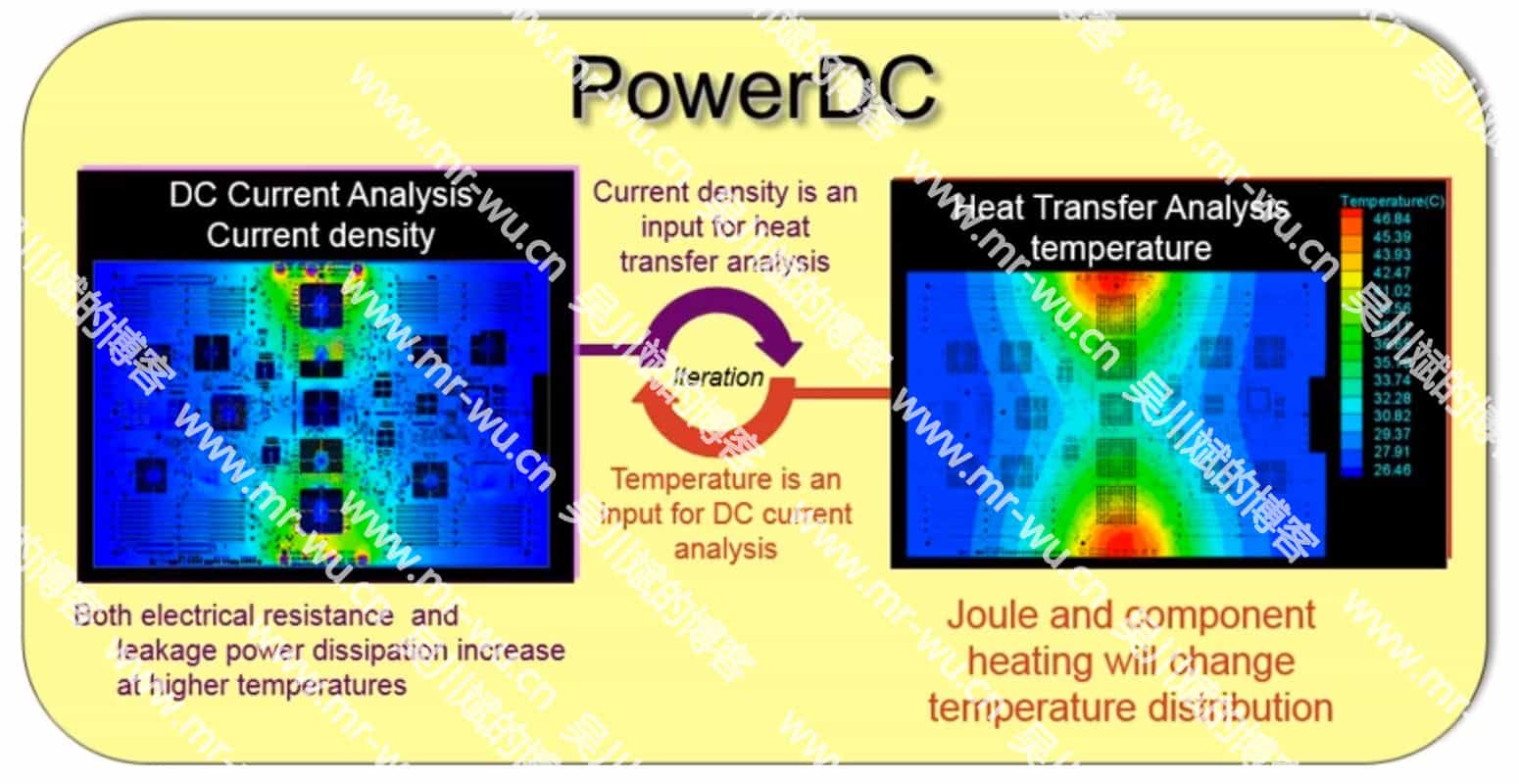

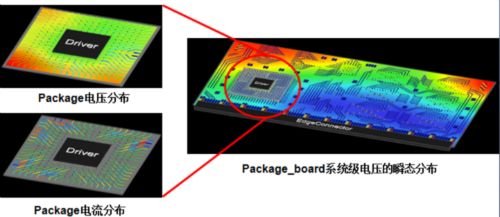

PowerDC-业界唯一的电热协同仿真工具

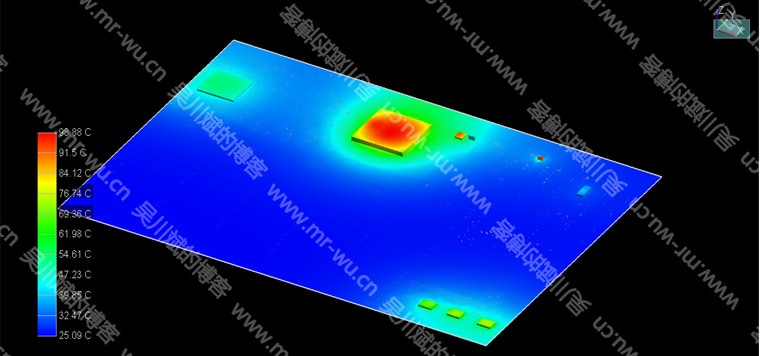

PowerDC是业界唯一一款电热协同仿真工具,能够给出在考虑电热相互影响的情况下,整板的直流电压降,电流密度分布,温度热量分布以及所有过孔通过电流的情况,并基于仿真结果给出最优的VRM感应线放置位置。PowerDC也可以为封装设计提取标准的JEDEC热阻模型。

PowerDC解决了当前PCB电路板上低压大电流和封装产品的IR-Drop直流压降分析、电压、电流及电流密度的分析和显示,同时集成了Thermal电热协同分析仿真工具,可以同时考虑器件功耗和电流传输带来的焦耳热,是真正意义上的PCB电热分析软件。

PowerDC提供业界唯一的电源模块感应线自动优化功能,通过该功能快速实现当前设计电源的最优化。

PowerDC流程化的自动规则检查功能,并结合可视化的选项与DRC规则检查,确保了各器件端到端的电压降裕量,进而确保电源网络的稳定供应。同时还可以快速检测定位电流密度超标、温度超标的区域进而降低产品的风险,目前在大多数低压大电流的板子上应用较多。

PowerDC主要特点:

- 帮助用户确定直流压降,电流密度问题

- 自动优化电压调节模块(VRM)感应线的位置

- 定位引起系统风险的电流热点

- 检测并罗列不易发现的不满足要求的过孔和布线瓶颈区域

- 通过电热混合仿真充分考虑电热之间的相互影响

- 帮助用户确定在不增加风险的情况下减少平面层设计的可行性

- 实现对PCB和封装并可结合芯片级的信息进行分析

- 通过一系列可选的内容显示控制实现报告的自动化,并通过其中的拓扑模块图实现压降的快速分析

Sigrity Speed2000-整板系统级全波瞬态分析工具

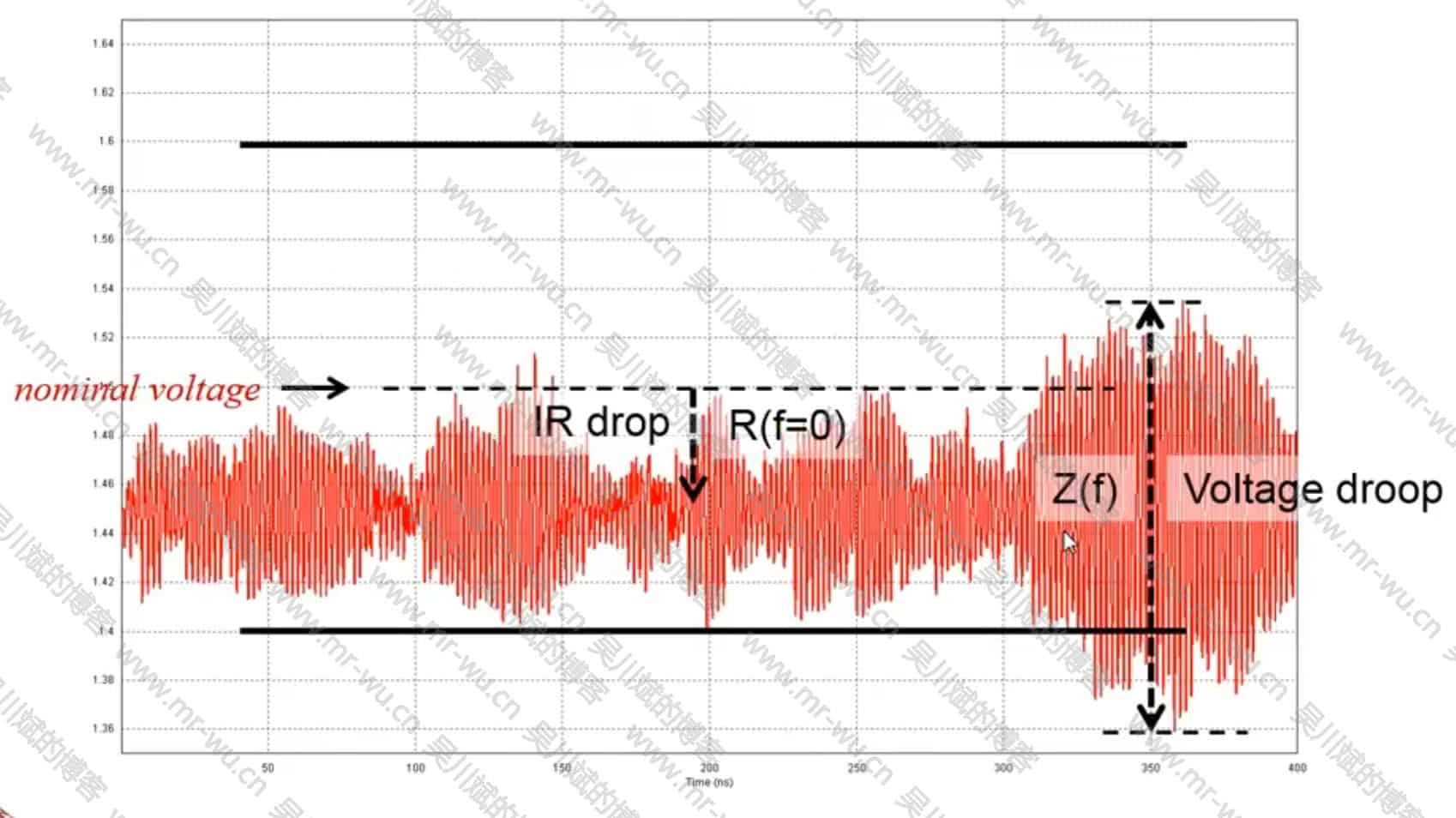

Speed2000是用于分析和设计高速PCB的通用时域工具。软件采用FDTD仿真技术进行多层电源地间的三维电磁场仿真。Speed2000真实地再现实际系统中的电源地网络,考虑封装和印刷电路板中的各种电磁效应,包括电源地之间的波动(同步开关噪声),过孔和走线之间的耦合,以及电路和封装间的交互作用。Speed2000不仅可以显示电压和电流随时间的变化,而且可以显示电压和电流在空间的变化,以此直观地告诉设计者,噪声是怎样产生的,如何传递的,以及噪声是否在容限范围之内,对于一般高速电路的总线和地址线仿真,频率在5Gbps以下基本上可以满足要求,仿真精准度也不错,但当速率继续提升至5Gbps以上乃至超过10Gbps,就需要采用三维模型提取,考虑接插件的封装,过孔,绑定线等效应,在System SI中进行高速通道系统的联合仿真。

Speed2000完整支持最新的IBIS/EBD/Spice/TouchStone等模型,仿真时为用户考虑各种实际的非理想因素,如平面破碎,高密度过孔等,并将信号完整性与电源完整性同时考虑,模拟出真实的SSO,得到基于实际工作状况下所有信号线的时域波形,电源/地平面实时的纹波抖动和空间分布,以及对应的近场和远场的EMI辐射情况。

Speed2000主要特点:

- 最大特色之一是,将电源网络和地网络当作非理想的情况来处理,考虑的是非理想的信号返回路径;

- 最大特色之二是,支持最新的 IBIS5.0模型以及最新的Touchstone2.0模型;

- 唯一不经过任何中间过程,可以直接做全系统级分析的时域仿真工具;

- 专业的时域仿真工具,专注于IC封装级和PCB板级的SI、PI 和 EMI/EMC仿真;

- 适用于布线前和布线后的SI/PI仿真,包含单板或多板;

- 适用于多路并行通道的SSN/SSO仿真,可进行全芯片的自动IBIS映射;

- 适用于高速串行通道的电源/地噪声分析,以及高速信号的眼图和抖动等;

- 适用于含晶体管(Transistor Level)模型的时域仿真;

- 适用于封装级和板级的 EMC/EMI近场和远场仿真;

- 适用于观测系统中任意电路、任意位置处的电压或电流波形;

- 适用于仿真有噪声干扰下关键器件或关键位置的电压电流响应;

- 适用于评估去耦电容的效应对系统电源或信号质量的影响;

Cadence Sigrity PowerDC 解决高速电路电源完整性DC电源分析的利器

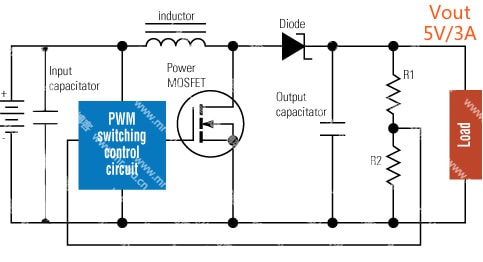

Cadence Sigrity电源完整性仿真工具箱中的PowerDC,正如其名称组成所述(Power+DC),主要应用于DC电源在PCB板上的电源完整性问题仿真,包括:整板电源IR-Drop、电流分布密度和热点分布等。

进入高速PCB设计领域,信号完整性问题已经让我们之前对于只要电路互联逻辑正确,元器件引脚间不短路不断路,PCB电路即可成功运行的认识完全颠覆。现在,电源完整性问题则再次毁掉画板君的三观。

在那个纯真的年代,那个妹子只要跟你拉上小手,就会厮守终生的年代,没有买房买车城市落户的要求,也没有苛刻要求的丈母娘的那个年代,电子数字电路也是那么的纯真,原理图上的电源就是那个纯粹的电源,我们仅仅关注电源电路或电源模块自身是否如何电路需求,而不会费神去担忧PCB板级的DC电源系统问题。

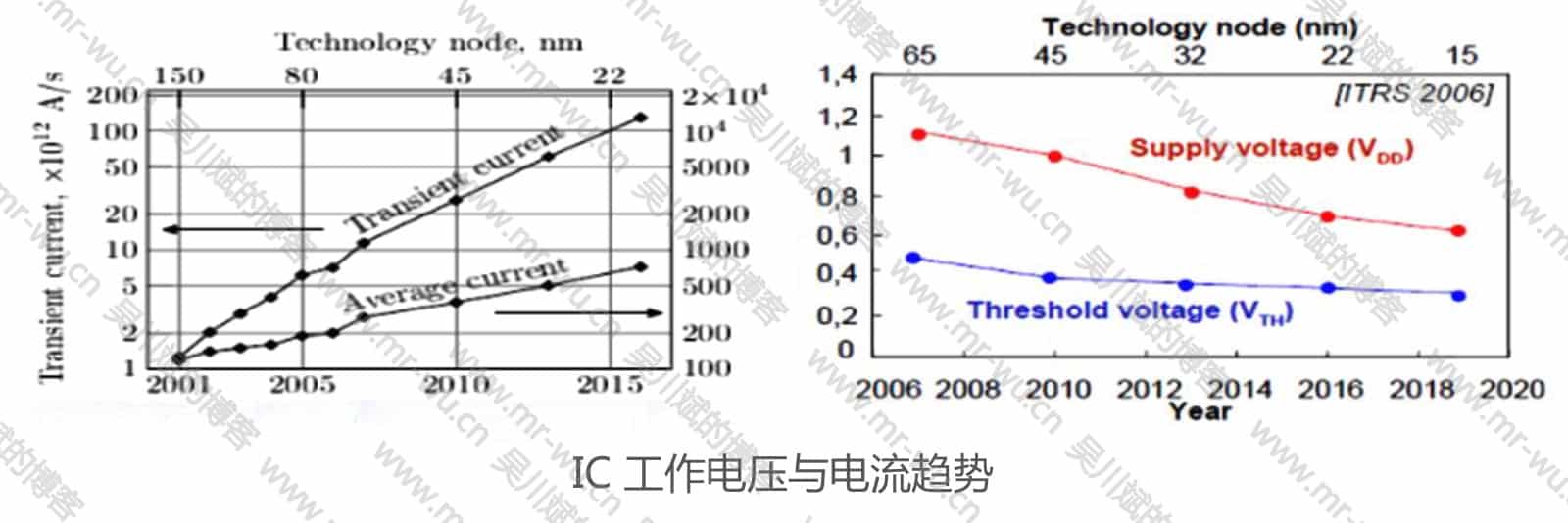

当今,随着电子产品市场需求的日趋旺盛,人们对电子产品的性能和功能要求也越来越高,这便推高了电子产品工艺的急剧增长,IC制程越来越小,所集成的晶体管越来越多,信号翻转速度越来越快,而核心电压却越来越低、消耗的电流越来越大,CPU 核心电压、IO电压、DRAM电压等、DC电源分割种类也越来越多样性,这些种种因素使得电源完整性问题越来越突出,电子产品设计过程充满了挑战。

在进行PCB设计时对DC电源进行前仿真和后仿真对于PCB设计是否成功影响非常重要,所以,吴川斌的博客将在接下来发布系列博文,详细介绍Sigrity PowerDC的仿真应用。

大概涉及的内容如下:

- Sigrity PowerDC 简介

- Sigrity PowerDC 界面介绍

- IR-Drop的基本概念

- 电流密度

- VRM模型

- Sigrity PowerDC 仿真实战

PowerDC直流分析综述

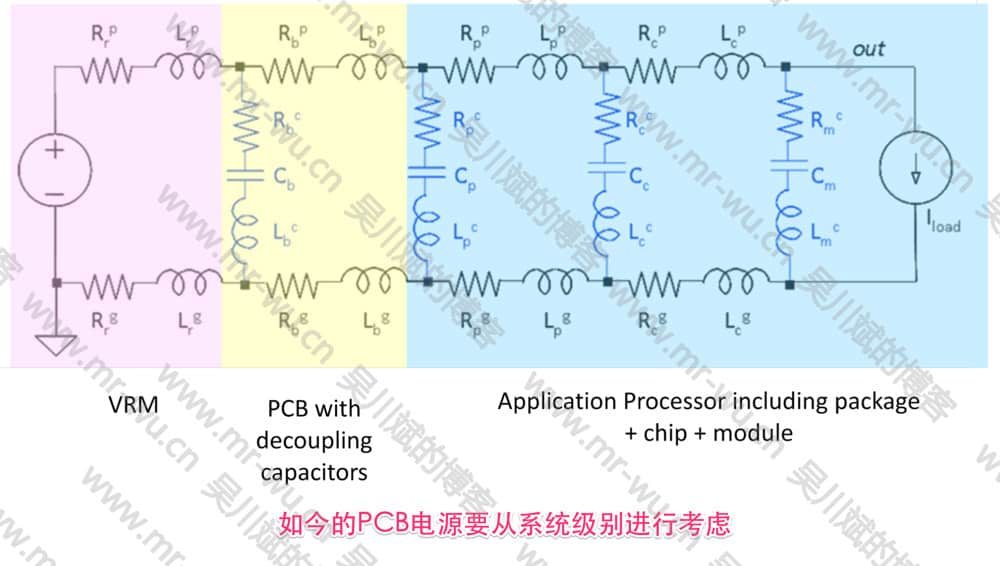

当前的系统设计核心供电电压越来越低,而总的工作电流和布线密度则越来越大,从而导致直流问题日益突出。

Sigrity产品系列中的PowerDC工具提供了完整的电源直流分析解决方案。电路板上电源阻抗对于DC电流来说相当重要,若电流直流设计不良,将导致PCB上器件的逻辑误动作,甚至会使得整个PCB烧毁,造成安全事故。电源品质的问题日益突出,所以在电源直流的分析是相当重要的。在真实环境中,不同的温度情况下,导电系数不尽相同,所以仿真时将温度考虑进来,仿真结果将更接近于真实地现象。

目前,常见的直流分析主要包括:

- IR-Drop问题使得电源无法为IC提供足够的电压

— 导致IC工作不正常

- 电源孤岛瓶颈造成电流密度过高

— 导致介质击穿、电路板故障、甚至起火造成安全事故

- 连接电源分割平面的过孔via上的电路过大

— 导致过孔故障,造成电源开路

- 过大的电流密度造成温升过热问题

— 极端情况下造成电路板损坏

— 电路板长时间温度过高会造成元器件过热,加速老化

IR Drop分析的重要性

IR Drop其含义为直流工作时由直流电阻造成的电压降,而此时的压降可直接由 I * R 的乘积得到因而得名。

各种设计中的不利因素使DC IR Drop问题加剧

- 核心供电电压持续减小:1.2V供电变得司空见惯;

- 器件的工作电流持续增大,使 IR Drop也有不断增大的趋势;

- 层数变少和高密度布线使电源网络的布线空间受到压缩和限制;

- 过孔周围的反焊盘使原来完整的电源平面变得支离破碎;

- 越来越复杂的PCB结构使非常有经验的工程师也难以靠手工完成 IR Drop的计算

IR Drop是一个系统级的问题

- 分析中有时需要考虑封装以及多个子板的整个系统级的PDN网络;

- 需要优化系统中每个器件的电压容限,确保他们都能正常工作;

- 有些高端系统的 VRM还带有电压反馈,反馈线的设计需要科学布局才能发挥最大效果

电阻分析的重要性

- 直流压降(IR Drop)直接与电源分配网络(PDN)上的总电阻成正比;

- 厚平面与实心的过孔有助于减小电阻值;

- 适当的电阻有助于减小谐振

电阻与信号完整性(SI)

- I/O网络的电阻是传输线产生直流损耗的根源;

- 短而宽的走线可以减小电阻

电流密度分析的重要性

当今的PCB项目设计,板子上不同电压的分类越来越多,12V、5V、3.3V、2.5V、1.5V等等,为了降低PCB成本,我们不可能针对每个电压等级创建一个对应的完整电源平面,通常的做法是进行电源平面分割。

分割的电源平面,再加上大量的通孔via设计,会使的电源平面出现瓶颈区域,而如今的IC需求的电流越来越大,当大电流通过一个狭窄区域的时候,通常会产生较大的电流密度,从而导致PCB板局部温度的升高。

电源平面上最大的电流密度区域通常称之为电流热点 (Hot Spot),这些电流热点有可能导致严重的热可靠性问题。

设计人员应尽量使板上的电流密度分布均匀,尤其要避免在关键的IC芯片附近和高速的信号走线附近出现电流热点。

电/热协同分析

- 高电流密度是电路板上热量的另一个来源

- 电/热协同仿真准确地确定了热量水平

— 考虑到热量在电路板中的传导方式

–还包括电路板上其他热源的影响

— 还包括电路板所处的环境文档

- 铜的导电率每10摄氏度变化4%

PowerDC的主要功能

- 布局布线前或布局后的PCB及IC封装DC分析;

- 彩色显示PCB各层的电压分布、平面电流分布和过孔电流分布;

- 可仿真Lumped to Lumped,Lumped to Multiple,Multiple toLumped以及Multiple to Multiple等各种形式的pin-to-pin电阻;

- 还可仿真多端口的阻抗网络,并生成DC情况下相应的S-param模型和SPICE等效模型;

- 多子板/多封装的IR Drop分析;

- 流程化仿真,指导用户快速准确的完成整个仿真,而且用户可以定制自 己特定的Workflow;

- 高效的有限元(FEM)算法无需用户设定Mesh即可得到平面上精细而平滑的每一个位置上的电压、电流值;

- 内置的Constraint management使仿真支持复杂设计的设计规则检查(DRC);

- 生成所有的电压、电流结果表格,并与预先设定的Constraints作比较;

- 将DRC Marker反标回Allegro Layout文件。

PowerDC的典型应用

优化 PDN网络中的关键指标

- 决定PDN层的铜厚

- 找到PDN层能满足IR Drop需求最小的宽度

- 进行快速的 “what if” 分析以比较不同设计的区别

- 发现 PDN网络中的设计隐患

- 找到系统中所有器件过压和欠压的条件

- 指出布线中会引起额外压降的 neck down区域

- 定位布线中会引起热可靠性问题的电流分布的 “hot spots”区域

- 现超出设计指标的 via, bump和ball电流

- 优化 VRM Sense Line的设置

- 对多器件的系统智能选择 VRM sense line的位置 • 安全的增大VRM的输出电压进行最可靠的补偿

- 输出其他系统分析需要的结果

- 创建DC等效电阻模型

- 进行包括 PCB, IC封装和on-chip模型在内的系统级IR Drop分析 • 输出热仿真工具可用的平面和过孔的电流分布文件

- 定量的计算路径中的loop电阻以进行对比分析和correlation研究

PowerDC的优势与特色

业界第一个可以进行电源地平面 IR Drop DRC检查的工具,用户对象包括 layout工程师,system 工程师和SI/PI工程师。

可协助Layout设计人员发现PCB板中不易发现的很多设计隐患,如:器件的过压/欠 压,电流分布的Hot Spot,超标的 via、bump和ball电流,平面中的neck-down和 dynamic plane cut 区域等。而这些隐患常常会导致器件不能工作甚至发生局部过热 烧毁等后果。

内置的Workflow可确保用户可以在较短的时间内就能掌握PowerDC的正确使用流程。 最新的DRC反标功能使Layout工程师可以在后台调用PowerDC,并及时在PCB版图 中将出现的DRC错误加以改进。

全新的FEM仿真引擎在仿真精度和效率上有了很大的提升。其精细的三角形网格剖分 比其他工具采用的矩形网格在计算结果和显示精度上要先进很多,另外特有的快速算 法使工具即使在仿真大型PCB时也仅需数分钟的时间。

一般的CAD工具只能保证电源/地网络的连通,但是却无法得知连接的好坏;而高端的 SI/PI工具通常更适合于AC瞬态仿真。

PowerDC拥有Apple, Cisco, Dell, EMC和IBM等50多家知名客户,使用PowerDC来分析PCB和IC封装中的直流问题已成为业界的共识。

总之:

随着智能手机、物联网、可穿戴设备应用的发展,PCB将会朝着更加高密度、工作定压更低、工作电流更大的方向发展,PCB设计过程都满了挑战,电源的DC问题将会对PCB的设计成败造成更加深远的而影响。

幸好,我们有Cadence的Sigrity PowerDC 仿真工具,是的我们在进行PCB设计前和PCB设计完成后都可以进行相应的PCB系统级DC电源仿真,找出电源、过热故障分析。

所以,接下来,老wu邀请您,一起手儿拉着手儿,一起开启Cadence Sigrity PowerDC的学习之旅。

Cadence 发布 Sigrity 2017 版本,除了效能提升之外,各相关程序新增功能如下:

- PowerDC – PowerTree 电源回路的拓扑结构

- Speed2000 – 新增 ESD 仿真的流程

- PowerSI – Special void 设定自动化

- 3DEM – Partial Inductance 及 SPICE 模型的提取

- SystemSI – 新增 PCI-E Gen4 和 P8+ OpenPOWER Compliance Kit

- XtractIM – XtractIM EPA 的 HTML 报告可与 APD 作交互查询

- T2B – 支持 IBIS 6.1 和 Random Pattern

Cadence Sigrity 2017 新功能介绍

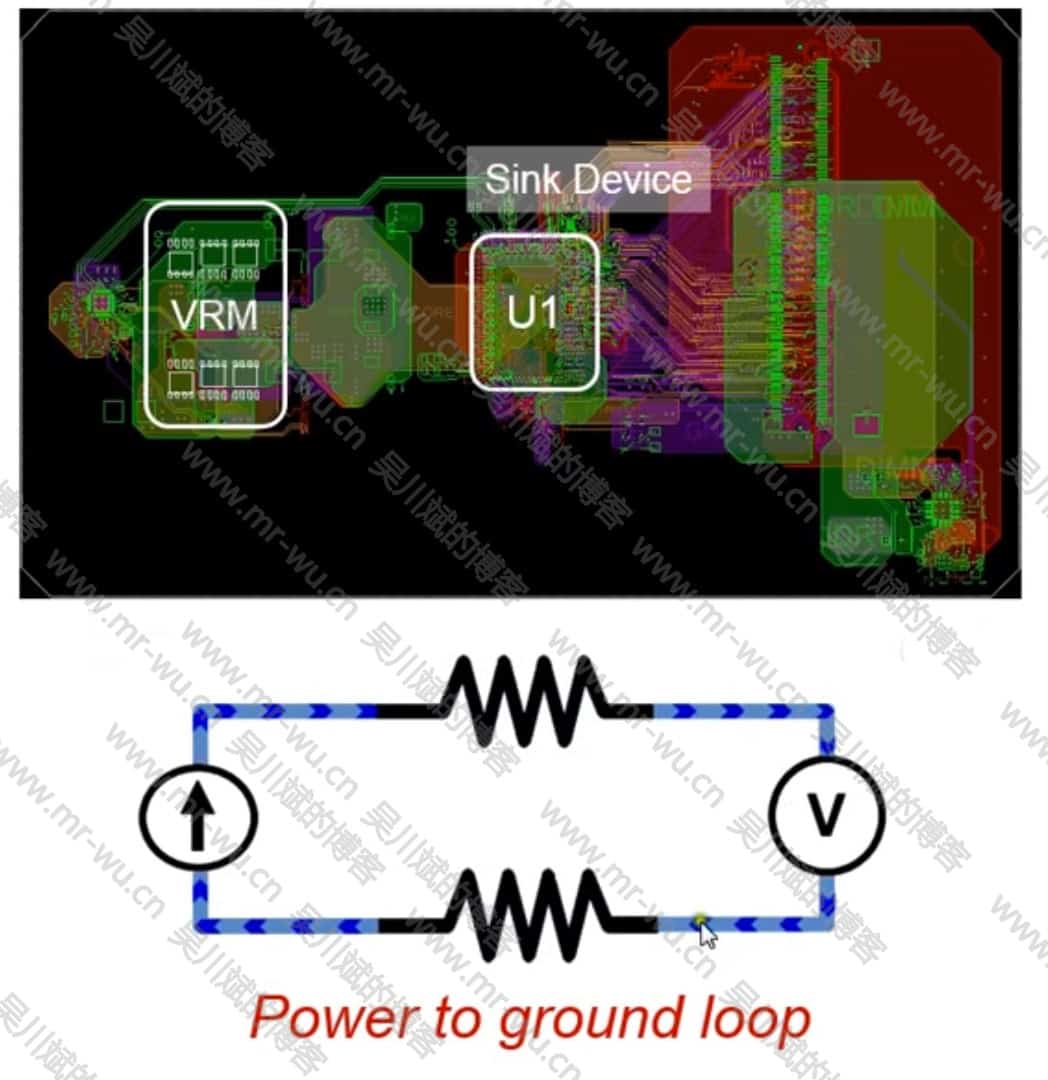

PowerTree

Power Tree 是一种由电路图或 PCB layout 抽出可视觉化的电源回路的拓扑结构资料的工具。除了产生 Power Tree 外,里面所有的元件属性都可透过手动添加或利用 AMM Model 来带出。它可以协助使用者很容易地进行早期电路功耗的评估及后续的自动化环境及条件的设置。 PowerTree可以单独执行,或是与整合到 PowerDC、OptimizePI 和 Allegro Sigrity PI。

PowerTree 为 DC 分析目的提供以下功能:

- 产生一个直观的由 VRM 到 Sink 端的电源拓扑结构

- 由电路图 /PCB 布局中提取元件属性

- 易于修改的元件资料

- 自动识别所有电源网络以进行分析

- 轻松查找/追踪电路图中的 ECO 变更

- 执行 pre-Layout 的直流分析

- 与 AMM model Library 沟通以便使用模型数据

- 可储存/载入重复使用 PowerTree 档案

Speed2000

新增 ESD Simulation 的工作流程

在 Sigrity2017 中,Speed2000 新增静电分析功能,用来检查放电问题对设计的影响。 ESD 可以定义为两个带电物体之间的静电流,有可能因为接触、短路或因介电质的损坏而触发。

例如:

- 通过与敏感设备的人类接触,人体触摸对引发放电现象往往会超过 4,000V。

- USB 缆线因具备供电能力,因此在端口接触瞬间亦会引发放电现象。

因来自触摸电子设备或系统的人体的静电放电可以产生数千伏特电压和几安培电流,这个现象可以容易导致 IC 内部电路损坏。以下是可能由 ESD 引起的损坏状况:

- 设备或系统完全故障

- 未预测的设备或系统行为

- 电磁辐射的干扰

增强对 Allegro 图档的支持

支持 PCB 背钻结构。

支持当 brd 文件时转换成 .spd 格式时对背钻孔结构的解析和仿真。

支持 Tabs routing 布线设计转换成 .spd 格式和仿真。

PowerSI

Special void 设定自动化

Void 的大小唯有极小于欲仿真的信号波长方可忽略以便加快仿真速度,因此需要有经验的工程师进行设定避免仿真偏差。新增的自动化功能可以根据仿真的频率自动设定 special void,简化设定难度并加快仿真速度。

改善低频的准确性

以往在提取参数时,如果线路中有串并联被动元件,PowerSI 会一起考虑进来。但是 PCB 分布的众多解耦合电容会使电源平面在低频会有很多共振点,曲线变化很大导致分别由低频仿真器与高频仿真器个别运算的结果结合的曲线 fitting 比较困难。因此比较好的作法是先提取未挂载被动元件的线路参数,之后再与被动元件的参数结合在一起。

支持 Allegro 档案中的背钻结构

PowerSI 可以直接支持 Allegro 档案设定的背钻结构,无须在PowerSI里面额外设定。

3DEM

支持多接脚被动元件的 SPICE model

Partial Inductance 及 SPICE 模型的提取

支持 quasi-static solver提取的 Partial Inductance,包含电源、信号甚至接地的走线并输出成 RLC SPICE 模型或矩阵形式的电感值的文档。

PowerDC

Thermal Flow Enhancements

热分析流程增强:

- 强化存档/载入分析结果的功能,以支持 2D / 3D 应力分布

- 添加热传递系数值到签核报告中

- 改进散热器编辑过程,避免在编辑模型后发生重复点击确定按钮

- 强化电源和温度分布图形档案

完整的Cadence Sigrity 2017新特性请参考这份PDF文档

https://pan.baidu.com/s/1gfgicXd

Sigrity 2016 带来了若干功能的更新:

- Upgraded serial link analysis flow

- Optimized design flows

- Upgraded 3D interconnect modeling

- Upgraded serial link analysis flow to accelerate the time to pass compliance tests

- New IBIS-AMI model building technology takes industry-proven equalization algorithms and provides a wizard-based graphical interface to rapidly facilitate creation of IBIS-AMI models. Available in two tiers, one that enables creation of models strictly for Sigrity tools, and another that creates models suitable for any IBIS-AMI compliant simulator.

- New cut-and-stitch model extraction technology allows for segmenting long serial links into sections that should be modeled using 3D full-wave and sections that can be modeled using hybrid extraction technology. The resultant model is extracted 10X faster than a strictly 3D full-wave extraction with 95% accuracy.

- New USB 3.1 (Gen 2) compliance kit to confirm that the 10Gbps interface requirements are met.

- Optimized design flow between PCB designer and power integrity engineer

- New cross-probing between DC analysis report file and Allegro® editing canvas

- Batch DC analysis available directly from the Allegro editing canvas

- Review previously generated DC analysis report files from the Allegro editing canvas

- Optimized design flow between IC package designer and characterization engineer

- Batch electrical performance assessment (EPA) available directly from the IC package designer’s editing canvas

- Batch package model creation using hybrid solver techb.kj

- nology directly from the IC package designer’s editing canvas

- Review previously generated EPA report data from the IC package designer’s editing canvas

- Upgraded 3D interconnect modeling to enable rapid modeling of low-cost PCB and IC packages

- New rapid and accurate capacitance extraction technology

- Quickly produce RLCG interconnect models for designs with few (or no) power and ground planes/shapes using new 3D quasi-static extraction technology

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具