LDO工作原理

1. 前言

目前市场上无论什么电子产品,只要涉及到电就必须用到电源,电源的分类有很多种,比如开关电源、逆变电源、交流电源等等。在移动端消费类电子产品中,常用的有DCDC电源和LDO电源两种,DCDC的优点是效率高,但是噪声大;LDO正相反,它是效率低,噪声小。

"LDO仿真文件" 已更新到公众号后台

这两种电源具体在什么场景下使用不能一概而论,通常而言,对于噪声不太敏感的数字电路多可以优先考虑DCDC,而对于模拟电路,由于对噪声比较敏感,可以优先考虑LDO。

目前由于技术的进步,DCDC的噪声已经可以减小很多了,但是相比于LDO还是稍逊一筹,今天我们来讨论下LDO的基本工作原理,仿真一个简单的LDO模型,介绍一下LDO使用过程中的相关注意事项。

2. LDO分类

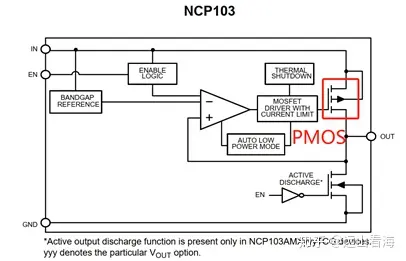

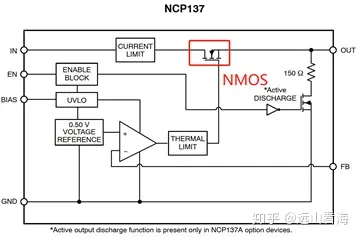

常见的LDO是由P管构成的,由于LDO效率比较低,因此一般不会走大电流。针对某些大电流低压差需求的场合,NMOS LDO应运而生。下图是PMOS和NMOS LDO的系统框图对比。我们暂且忽略系统的传递函数,把目光集中到LDO调节稳定的工作过程,下面我们就着重来介绍下PMOS LDO的基本工作原理。

NMOS LDO原理请见下面链接

3. PMOS LDO基本原理

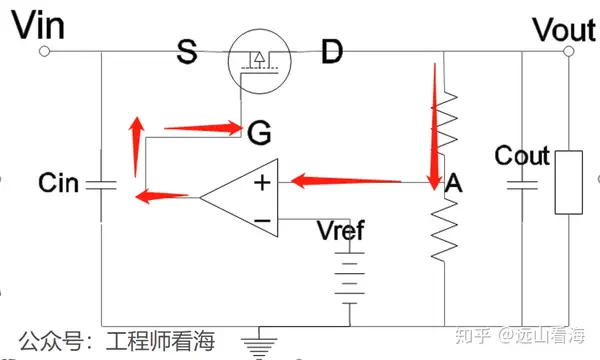

下面是一个PMOS LDO最基本结构框图。我们可以看到LDO主要由PMOS、运放、反馈电阻和基准参考电压构成。LDO主要工作流程是将输出电压通过分压电阻分压,Va和基准参考电压做比较,通过运放输出Vg来调节输出,反馈回路已用红色轨迹标识出,具体原理分两个方面详细介绍。

A.反馈回路

当Vout由于负载变化或其他原因电压下降时,两个串联分压电阻两端的电压也会下降,进而A点电压下降,A点的电位和Vref电位相比较,误差放大器会减小它的输出,使得G电位下降,Vs电压不变,进而使得|Vgs|的压差增加(我们用Vgs和Vds的绝对值描述PMOS更直观),输出电流Isd会增加,输出电流Isd增加就会使得Vout上升,完成一次反馈控制,使得Vout又回到正常电位,。

总结过程如下:

Vout↓——>Va↓——>Vg↓——Iout↑——>Vout↑

B. PMOS驱动的反馈

上面的描述中有两个地方格外介绍下,其一是,当A小于Vref时,G点的电位就会减小,通俗点理解,运算放大器总是倾向于使得+-输入端的电压相等,因此,当A小于Vref时,运放就会减小输出,以后我会用最浅显的语言专门介绍运放“虚短虚断”概念的由来和应用。

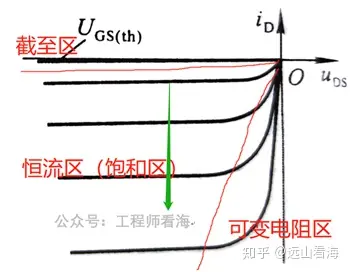

另一点是,G电位下降后为什么Iout就上升呢?这就涉及到PMOS工作状态,下图是PMOS的输出特性曲线,或者叫做伏安特性曲线,是PMOS本身的一个特性,根据G、D、S电压不同,MOS会工作在不同的区域,即可变电阻区,饱和区(恒流区),截至区。LDO中的MOS是工作在恒流区的。

顺着下图绿色箭头指示方向|Vgs|逐渐上升,|Id|跟着|Vgs|上升而上升,而这段区域内不管Vds怎么变换Id基本不变,换句话说,恒流区内,Id只受Vgs控制,因此基于MOS的放大器有时也被叫做跨导放大器。这就是PMOS LDO工作原理的核心部分。

为方便描述,我们将两个图片放到一起讲。

继续上文:若Vout异常降低,Vin不变,则Vout-Vin=Vd-Vs=Vds,|Vds|上升(Vds<0),在输出特性曲线中体现为,由状态工作点C转移到D。紧接着反馈回路开始发挥作用,由于Vout下降,则Va降低,运放会使得Vg下降,Vg-Vs=Vg-Vin=Vgs,|Vgs|也上升(Vgs<0),在|Vgs|驱动下Iout会慢慢上升,在输出特性曲线恒流区内体现为MOS从状态工作点D向状态工作点E,当Iout=Id随着Vgs上升时,Vds慢慢减小,最终Vout又上升回来,完成了一次完整的反馈控制。

4. LDO模型简单仿真

仿真文件已上传公众号

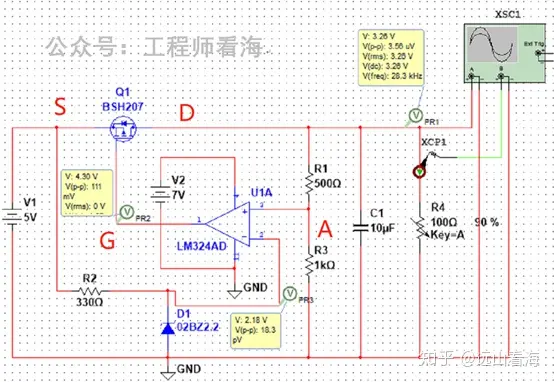

下图是使用multisim仿真的电路,LDO为5V转3.3V,当输出变化时,会通过A点反馈至MOS的G极,进而调节输出。

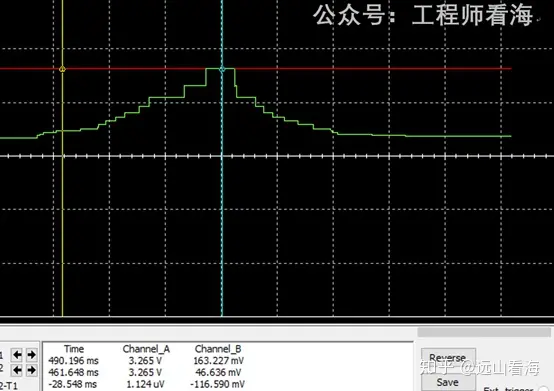

下图是LDO输出的电压和电流波形,红色是电压,绿色是电流。

下一节我们讨论NMOS LDO基本工作原理以及LDO其他参数的意义,欢迎关注我的公众号:工程师看海

相关阅读: