数字电路硬件设计系列(十七)之上电时序控制电路

1 简介

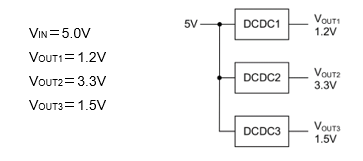

上电时序,也叫做Power-up Sequence,是指电源时序关系。下面就是一系列电源的上电的先后关系:

2 方案介绍

2.1 电容实现延时

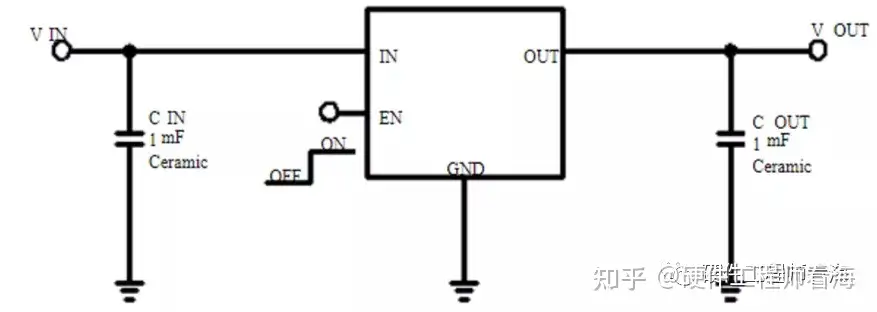

采用不同的电容来控制上电延时时间的长短,具体的电路见下图:

这种上电时序控制的方式,电路结构简单,但是延时时间难以精确的控制。在FPGA的电源时序控制中,应用十分广泛。

2.2 芯片控制延时

我们采用的LM3880芯片进行电源时序控制,这种控制的方式比较简单。LM3880 简单电源时序控制器提供了最简单的方法来控 制多个独立电压轨的上电时序和下电时序。通过错开启 动序列,可以避免可能影响系统可靠性的锁存情况或大 浪涌电流。

2.2.1 上电/下单控制

上电与下单的延时时间由EN管脚进行控制,默认是2ms,上电/下电的时序图见下:

-

上电序列

-

下电时序

2.2.2 延时时间计算

如需对 VCC 电压轨提供额外的延迟序列,在 EN 引脚上连接一个电容,见下图:

在使用内部上拉电流源为外部电容 (CEN) 充电的情况下,可通过下面公式来计算使能引脚延迟:

第一个计时器将在上升阈值开始计数,但始终会在第一个输出标志 释放之前 EN 引脚取消置位时复位。

3 建议

-

电源建议

VCC 引脚应尽可能靠近输入电源 (2.7–5.5V)。不需要使用输入电容,但建议在 VCC 引脚上存在噪声时使用输入电 容。可以使用 0.1μF 陶瓷电容器来旁路该噪声。

-

布局建议

-

应在标志输出引脚和正输入电源(通常为 VCC)之间连接上拉电阻。也可以使用独立的标志电源。这些电阻应 尽可能靠近简单电源时序控制器和标志电源。建议使用最短的迹线进行连接。上拉电阻器的典型值是 100kΩ。

-

对于非常严格的时序要求,应使用最短且长度相等的连线将标志输出连接到所需的输入。这将减少线路上标志 输出之间的任何传播延迟和时序误差。

电源时序规格①: 电源时序规格及控制框图 - 电源设计电子电路基础电源技术信息网站_罗姆电源设计R课堂 (rohm.com.cn)

电源时序规格①: 电源时序规格及控制框图

关键要点:

・在时序①中,实现了将3个系统的电源按顺序导通、并按相反顺序关断的时序。 ・在实际设计之前,通过功能块来考虑实现目标工作所需的配置。 ・时序①是使用3个电源IC、4个Power Good功能和3个Discharge功能实现的。

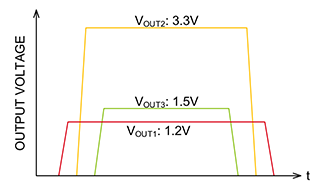

首先,确认要实现的电源时序规格,并在设计实际电路之前通过控制模块来探讨其配置。本文会使用两个电源时序规格示例,先从第一个示例“电源时序 ①”开始。 电源时序规格① 规格①是控制3个系统的电源的时序。输入输出电压的规格和电源配置如下:

在本设计中,是由3个电源IC构成的。电源IC假定为开关稳压器(DC/DC转换器)或线性稳压器(LDO)。作为电源IC的功能,需要可以控制输出的ON和OFF的使能引脚。

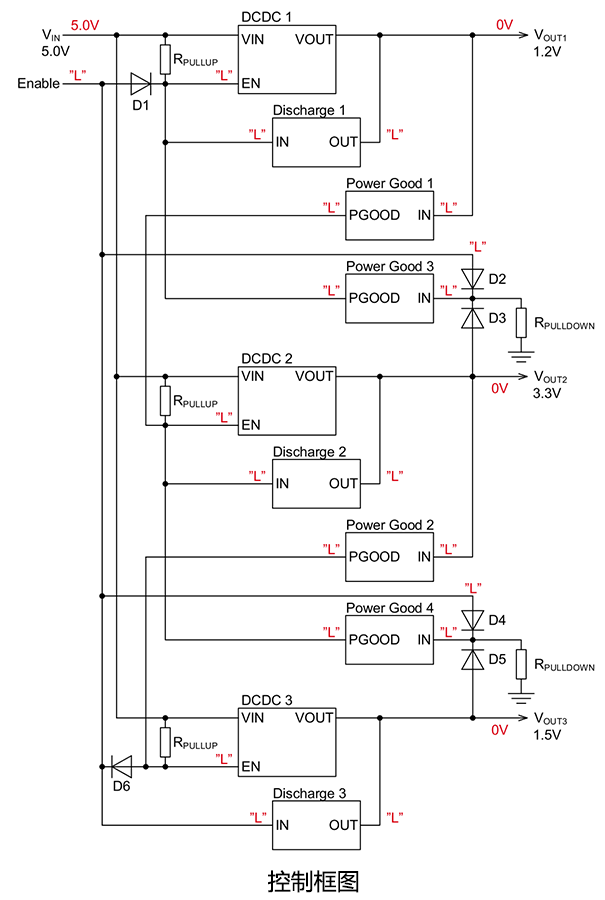

控制框图① 下面是实现了时序规格①的控制框图。

要实现时序规格①,除了3个电源IC之外,还需要4个Power Good功能、4个Discharge功能、以及电阻和二极管,从控制框图中可以看到它们。由于框图是为了显示功能和工作而绘制的,因此省略了实际电路中所需的各IC和电路的外置部件。下面介绍各功能和作用。 ・DCDC 1、DCDC 2和DCDC 3 是独立的电源IC,它们的输出由使能(EN)引脚控制。 ・Power Good 1和2用来在电源导通时监测DCDC的输出电压,当达到目标电压时,向接下来要启动的DCDC输出“High”(以下简称“H”)信号。 ・Power Good 3和4用来在关断电源时监测DCDC的输出电压,当达到目标电压时,向接下来要关断的DCDC输出“Low”(以下简称“L”)信号。 ・Discharge模块通过在关断电源时快速释放DCDC输出电容器中的充电电荷来降低输出电压,使电源时序正常工作。 在该框图中,DCDC模块的EN和VOUT之间、Power Good模块的IN和PGOOD之间、以及Discharge模块的IN和OUT之间被设计为正逻辑。也就是说,在“H”时,DCDC处于使能状态,Power Good处于达到目标电压状态,Discharge处于输出为ON的状态。此外,Power Good模块的PGOOD引脚(输出)和Discharge模块的OUT引脚采用集电极开路或漏极开路形式。

很多负载对电源有上电时序和电压转换速率(压摆率)的要求,比如负载需要多路电源时,这些电源要有先后的上电、下电的顺序,同时也要满足一定的上、下电斜率要求。

关闭电源后,受负载电路大电容影响,电源电压下降会缓慢。如果在负载电容没有释放完电的情况下立刻上电,可能会导致系统不能正常启动。

屏幕可能出现花屏,相机打开异常,或者系统直接死机。

因此有的产品说明中有介绍,比如路由器:断电后等待10秒再重新上电。

一些老式电视机,关机后电源指示灯会过几秒才熄灭,就是没有快速放电电路导致。

为了避免反复开关负载引起电源异常,那么一般就要增加快速放电电路。一个非常简单的放电电路就是加一个对地开关MOS,当需要放电时,就打开MOS,不需要放电时,就断开MOS。

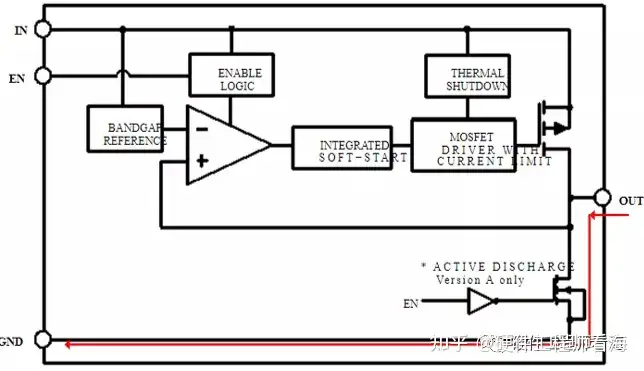

下图中的LDO内部就集成了快放电功能。

该LDO的快放电功能受控于EN引脚,当EN引脚为高时,LDO输出Vout,当EN引脚为低电平时,LDO关闭输出,快放电通路打开,负载电容上的电压通过放电MOS被释放。

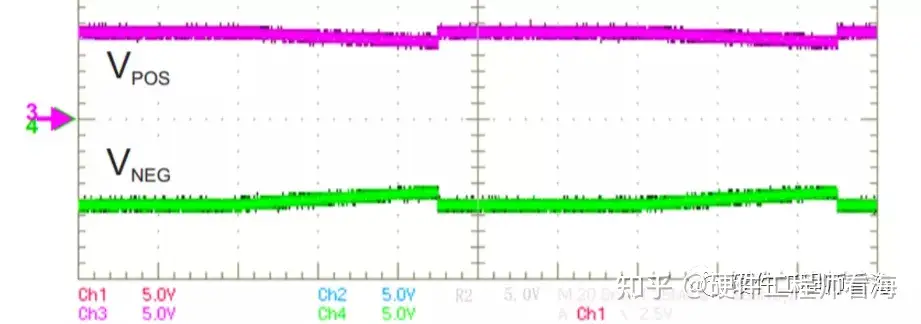

下图粉色(正电)和绿色(负电)电源是屏幕的供电,增加快放电功能后的时序波形可以看出下电非常干净利索。

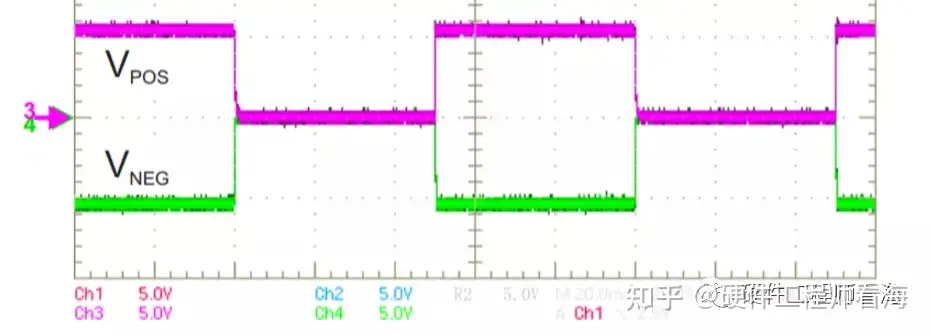

而下图Vpos和Vneg下电非常缓慢,拖泥带水,非常容易出现闪屏的现象。

以上就是电源快速放电功能的简单介绍

有时候,我们会想当然地为印刷电路板上的电路上电,殊不知这可能造成破坏以及有损或无损闩锁状况。这些问题可能并不突出,直到量产开始,器件和设计的容差接受检验时才被发现,但为时已晚,项目和产品的时间及交货将会受到极大影响,成本大幅攀升。而为了解决这一阶段中发现的错误,需要进行大量修改,包括PCB布局变更、设计更改和额外的异常现象等。

随着集成电路(IC)时代的到来,许多功能模块被集成到一个IC中,因而需要利用多个电源为这些模块供电。这些电源的电压有时候相同,但更多时候是不同的。市场上的片上系统(SoC)IC越来越多,这就产生了对电源进行时序控制和管理的需求。

某些IC明确要求定义恰当的上电序列。在使用多个电源的IC中,如转换器(包括模数转换器ADC和数模转换器DAC)、数字信号处理器(DSP)、音频/视频、射频及许多其它混合信号IC中,这一要求相当常见。本质上,包含某种带数字引擎的模拟输入/输出的IC都属于这一类,可能需要特定的电源时序控制。这些IC可能有独立的模拟电源和数字电源,某些甚至还有数字输入/输出电源。

本文将讨论设计工程师在新设计中必须考虑的某些更微妙的电源问题,特别是当IC需要多个不同的电源时。目前,一些较常用的电源电压是:+1.8 V、+2.0 V、+2.5 V、+3.3 V、+5 V、−5 V、+12 V和−12 V。

(P.S. 本文的讨论可能只是有限展示小A家的几款ADC,也欢迎各位小伙伴在下方评论区里留言分享你的观点。另外,下面所展示的数据手册都含有“绝对最大额定值”(AMR)部分,它说明为避免造成破坏,对引脚或器件可以施加的最大电压、电流或温度。)

PULSAR ADC示例——绝对最大额定值

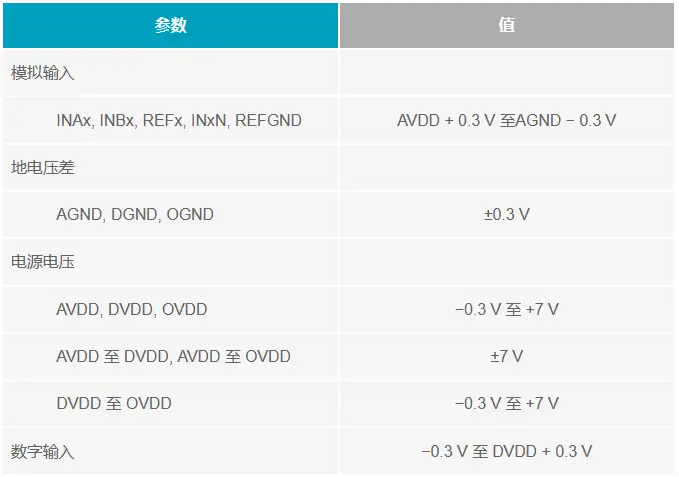

AD7654PulSAR 16位ADC是采用三个(或更多)独立电源的混合信号ADC的范例。这些ADC需要数字电源(DVDD)、模拟电源(AVDD)和数字输入/输出电源(OVDD)。它们是ADC,用于将模拟信号转换成数字代码,因此需要一个模拟内核来处理传入的模拟输入。数字内核负责处理位判断过程和控制逻辑。I/O内核用于设置数字输出的电平,以便与主机逻辑接口(电平转换)。表1摘自AD7654 (Rev. B)数据手册的“绝对最大额定值”部分。

表1. AD7654的绝对最大额定值(Rev. B)

注意,表1中所有三个电源的范围都是−0.3 V至+7 V。相对于DVDD和OVDD,AVDD的范围是+7 V至−7 V,这就确认了AVDD和DVDD无论哪一个先上电都是可行的。此外,AVDD和OVDD无论哪一个先上电也是可行的。然而,DVDD与OVDD之间存在限制。技术规格规定,OVDD最多只能比DVDD高0.3 V,因此DVDD必须在OVDD之前或与之同时上电。如果OVDD先上电(假设5 V),则DVDD在上电时比OVDD低5V,这不符合“绝对最大额定值”要求,可能会损坏器件。

模拟输入INAx、INBx、REFx、INxN和REFGND的限制是:这些输入不得超过AVDD + 0.3 V或AGND − 0.3 V。这说明,如果模拟信号或基准电压源先于AVDD存在,则模拟内核很可能会上电到闩锁状态。这通常是一种无损状况,但流经AVDD的电流很容易逐步升至标称电流的10倍,导致ADC变得相当热。这种情况下,内部静电放电(ESD)二极管变为正偏,进而使模拟电源上电。为解决这个问题,输入和/或基准电压源在ADC上电时应处于未上电或未连接状态。

同样,数字输入电压范围为−0.3 V至DVDD + 0.3 V。这说明,数字输入必须小于DVDD + 0.3 V。因此,在上电时,DVDD必须先于微处理器/逻辑接口电路或与之同时上电。与上述模拟内核情况相似,这些引脚上的ESD二极管也可能变为正偏,使数字内核上电到未知状态。

下面来看下采用更低电源(2.5 V)的AD7621。表2摘自AD7621(Rev. 0)数据手册的“绝对最大额定值”部分。

表2. AD7621的绝对最大额定值(Rev. 0)

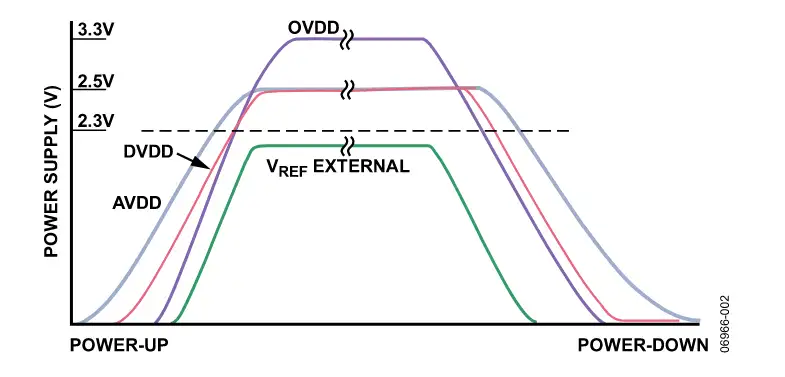

同样,OVDD与DVDD之间存在限制。“绝对最大额定值”规定:OVDD必须小于或等于DVDD + 0.3 V,而DVDD则必须小于2.3 V。一旦DVDD在上电期间达到2.3 V,该限制便不再适用。如果不遵守该限制,AD7621(和AD7623)可能会受损(见图1)。

图1. 可能的上电/关断序列—AD7621 (Rev. 0)

因此,一般上电序列可能是这样的:AVDD、DVDD、OVDD、VREF。但是,每个应用都不一样,需要具体分析。注意,器件关断与器件上电同样重要,切记遵守同样的规格要求。图1所示为AD7621的典型上电/关断序列。

Σ-Δ型ADC示例

AD7794 Σ-Δ型24位ADC是另一个很好的例子。表3摘自AD7794(Rev. D)s数据手册的“绝对最大额定值”部分。

表3. AD7794的绝对最大额定值(Rev. D)

该ADC的问题与基准电压有关,它必须小于AVDD + 0.3 V。因此,AVDD必须先于基准电压或与之同时上电。

电源时序控制器

一般而言,电源时序控制器件的工作原理是:当第一个调节器的输出电压达到预设阈值时,就会开始一段时间延迟,延迟结束后才会使能后续调节器上电。关断期间的程序与此相似。时序控制器也可以用于控制电源良好信号等逻辑信号的时序,例如:对器件或微处理器施加一个复位信号,或者简单地指示所有电源均有效。

【小A说】

如今大部分要求高速和低功耗的电路PCB上都需要多个电源,例如:+1.8 V、+2.0 V、+2.5 V、+3.3 V、+5 V、−5 V、+12 V和−12 V。为PCB上的这些电源供电并不是一件轻而易举的事情。必须仔细分析,设计一个正确可靠的上电和关断序列。采用分立设计变得越来越困难,解决之道就是采用电源时序控制IC,只要改变一下代码就能改变上电顺序,而不用变更PCB布局布线。也欢迎各位小伙伴在下方评论区和小A分享一下电源时序控制的操作方式~