FPGAer:CRC校验的FPGA实现

模2加法运算:1+1=0、0+1=1、0+0=0。模2减法运算:1-1=0、0-1=1、1-0=1、0-0=0。

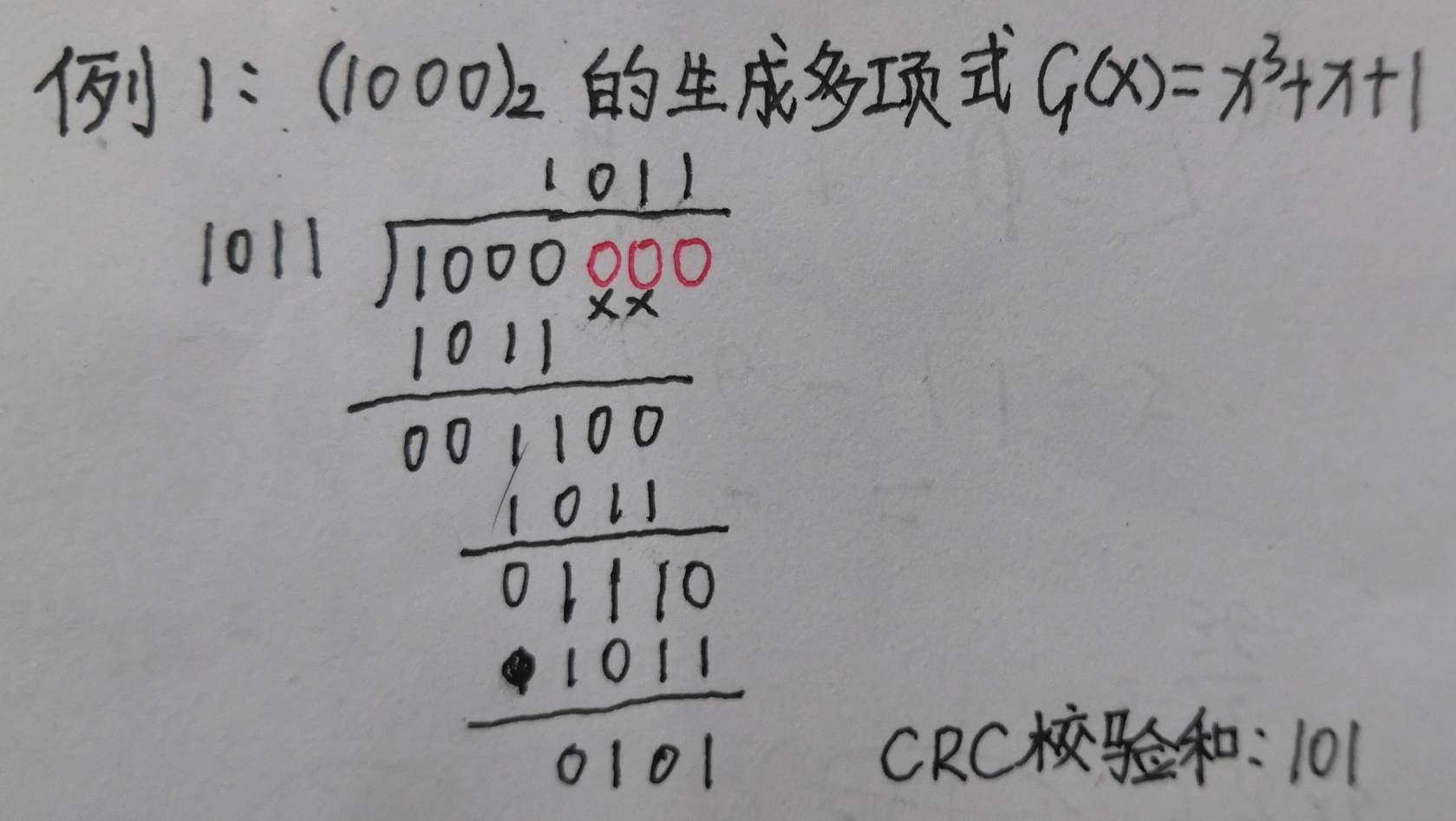

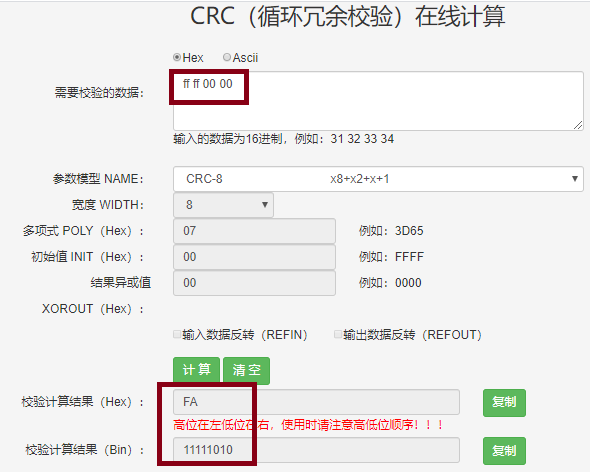

举个例子:

ff ff 00 00(16)的生成多项式:

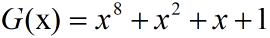

检验电路:

RTL代码:

module shizhan(

input sys_clk,

input sys_rst_n,

input data,

input data_valid,

input crc_start,

output reg [7:0]crc_out,

output reg [5:0]num,

output reg crc_valid

);

reg [7:0]crc;

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

crc<=8'b0;

else if(crc_start)

crc<=8'b0;

else if(data_valid)begin

crc[0]<=crc[7]^data;

crc[1]<=crc[0]^crc[7]^data;

crc[2]<=crc[1]^crc[7]^data;

crc[3]<=crc[2];

crc[4]<=crc[3];

crc[5]<=crc[4];

crc[6]<=crc[5];

crc[7]<=crc[6];

end

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

num<=6'b0;

else if(crc_start)

num<=6'b0;

else if(num==6'd32)

num<=6'b0;

else if(data_valid)

num<=num+1'b1;

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)begin

crc_valid<=1'b0;

crc_out<=1'b0;

end

else if(num==32)begin

crc_valid<=1'b1;

crc_out<=crc;

end

endmodule

仿真代码:

`timescale 1ns/1ns

module shizhan_tb;

reg sys_clk;

reg sys_rst_n;

reg data;

reg data_valid;

reg crc_start;

wire [7:0]crc_out;

wire [5:0]num;

wire crc_valid;

shizhan u_shizhan(

.sys_clk (sys_clk),

.sys_rst_n (sys_rst_n),

.data (data),

.data_valid (data_valid),

.crc_start (crc_start),

.crc_out (crc_out),

.num (num),

.crc_valid (crc_valid)

);

initial begin

sys_clk<=1'b1;

sys_rst_n<=1'b0;

data_valid<=1'b0;

data<=1'b1;

crc_start<=1'b0;

#10 sys_rst_n<=1'b1;

#50 data_valid<=1'b1;

#320 data<=1'b0; //ffff0000一共有32位,即11111111 11111111 00000000 00000000,所以经历了16*20ns=320ns的高电平,接着320ns的低电平。

#320 data_valid<=1'b0;

#50 $stop;

end

always #10 sys_clk<=~sys_clk;

endmodule

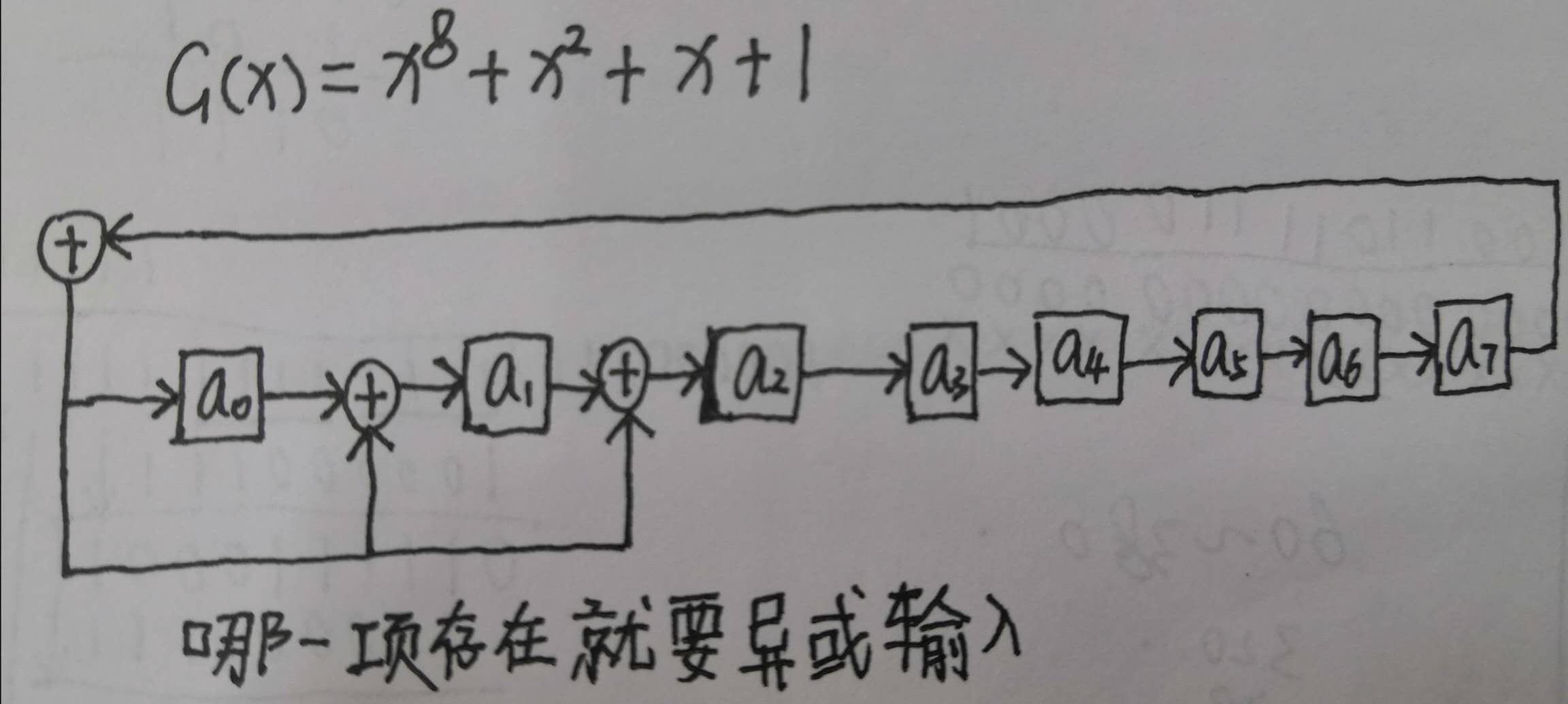

检验正确:

浙公网安备 33010602011771号

浙公网安备 33010602011771号