基于Verilog HDL的异步FIFO设计与实现

基于Verilog HDL的异步FIFO设计与实现

在现代IC设计中,特别是在模块与外围芯片的通信设计中,多时钟域的情况不可避免。当数据从一个时钟域传递到另一个域,并且目标时钟域与源时钟域不相关时,这些域中的动作是不相关的,从而消除了同步操作的可能性,并使系统重复地进入亚稳定状态[1]。在有大量的数据需要进行跨时钟域传输且对数据传输速度要求比较高的场合,异步FIFO是一种简单、快捷的解决方案。

异步FIFO用一种时钟写入数据,而用另外一种时钟读出数据。读写指针的变化动作由不同的时钟产生。因此,对FIFO空或满的判断是跨时钟域的。如何根据异步的指针信号产生正确的空、满标志,是异步FIFO设计成败的关键。本文提出一种新颖的异步FIFO设计方案,它通过先比较读写地址并结合象限检测法产生异步的空/满标志,再把异步的空/满标志同步到相应的时钟域。通过仿真验证,该方法是稳定有效的。

1异步信号传输问题的分析

在一个ASIC或FPGA库中,每种触发器都有时序要求。对于使用上升沿触发的触发器来说,建立时间(Setup Time)是在时钟上升沿到来之前,触发器数据保持稳定的最小时间;而保持时间(Hold Time)是在时钟上升沿到来之后,触发器数据还应该保持的最小时间[2]。如图1所示,在时钟上升沿前后的这个窗口内数据应该保持不变,否则会使触发器工作在一个不确定的状态,即亚稳态。当触发器处于亚稳态,且处于亚稳态的时间超过了一个时钟周期时,这种不确定的状态将会影响到下一级的触发器,最终导致连锁反应,从而使整个系统功能失常。当一个信号跨越某个时钟域时,对新时钟域的电路来说它就是一个异步信号。由于异步信号之间的时序是毫无关系的,因此必然存在Setup Time/Hold Time冲突。为了避免亚稳态问题,采用如图2所示的双锁存器法[3],即在一个信号进入另一个时钟域前,将该信号用两个锁存器连续锁存两次,最后得到的采样结果就可以消除亚稳态。

消除亚稳态只是保证了信号电平的稳定,要在不同时钟域中准确传输数据还需要一个接口电路。异步FIFO就是一种不同时钟域之间传递多位数据的常用方法。

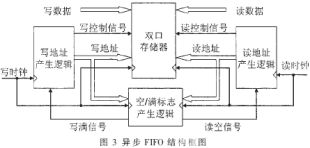

异步FIFO是一种先进先出电路,用在需要实时数据接口的部分,用来存储、缓冲在两个异步时钟之间的数据传输。主要由双口存储器、读地址产生逻辑、写地址产生逻辑、空/满标志产生逻辑四部分构成。图3是一种常用的异步FIFO设计方案,其中,读地址(rptr)和空标志(rempty)由读时钟 (rclk)产生,而写地址(wptr)和满标志(wfull)由写时钟(wclk)产生。把写地址与读地址相互比较以产生空/满标志。由于读写地址的变化由不同的时钟产生,所以对FIFO空或满的判断是跨时钟域的。如何避免异步传输带来的亚稳态以及正确地产生空/满标志是设计异步FIFO的难点。

2.1 读写地址产生逻辑

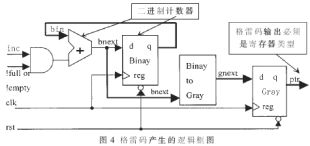

读写地址线一般有多位,如果在不同的时钟域内直接同步二进制码的地址指针,则有可能产生亚稳态。例如,读指针从011变化到100时,所有位都要变化,读指针的每一位在读时钟的作用下,跳变不一致,即产生毛刺。如果写时钟恰好在读指针的变化时刻采样,得到的采样信号可能是000~111中的任何一个,从而导致空/满信号判断错误。由实践可知,同步多个异步输入信号出现亚稳态的概率远远大于同步一个异步信号的概率[3]。解决这一问题的有效方法是采用格雷码。格雷码的主要特点是相邻的两个编码之间只有一位变化。图4是格雷码产生的逻辑框图。在读使能或写使能信号有效、并且空/满标志无效的情况下,读写指针开始累加,进行FIFO读或写操作。二进制码与格雷码的转换是一个“异或”运算:gnext=(bnext>>1)^bnext。格雷码gnext 经寄存器输出格雷码指针ptr。这种方法采用了两组寄存器,虽然面积较大,但是有助于提高系统的工作频率。

2.2 空/满标志产生逻辑

正确地产生空/满标志是设计任何类型FIFO的关键点。空/满标志产生的原则是:写满而不溢出,能读空而不多读。传统的异步FIFO把读写地址信号同步后再进行同步比较以产生空满标志,由于读写地址的每一位都需要两级同步电路,大量使用寄存器必然要占用很大的面积。这种方法不适合设计大容量的FIFO。当读、写指针相等也就是指向同一个内存位置时,FIFO可能处于满或空两种状态,必须区分FIFO是处于空状态还是满状态。传统的做法是把读、写地址寄存器扩展一位,最高位设为状态位,其余低位作为地址位。当读写指针的地址位和状态位全部吻合时,FIFO处于空状态;当读写指针的地址位相同而状态位相反时,FIFO处于满状态。传统的异步FIFO工作频率低、面积大。下面将介绍一种产生空/满标志的新方法。

通过异步比较读写指针ptr以及读写指针的最高两位 进行判断,产生两个异步的空/满标志信号(aempty/afull)送入读写模块进行同步,最后向外部输出两个同步的空/满信号(rempty/wfull)。空/满信号的产生过程:如图5所示,对于深度是2n的异步FIFO,按照其读指针rptr[n:0]和写指针wptr[n:0]最高两位的不同取值,可把地址空间分为四个像限[4]。当写指针比读指针落后一个像限时,意味着写指针即将从后面追上读指针,FIFO处于“可能将满”状态,在图6所示的空满信号产生逻辑框图中声明一个 direction信号并把它置为1;当读写指针完全相等并且direction为1时,则FIFO处于满状态并且把满信号afull置为0(低电平有效);当读指针比写指针落后一个像限时,意味着读指针即将追上写指针,FIFO处于“可能将空”状态,或者当写操作复位信号wrst有效时,再进行读操作,则FIFO也处于“可能将空”状态,此时把direction信号置为0;当读写指针完全相等并且direction为0时,则FIFO处于空状态,空标志信号aempty置为0。

读写地址异步相比较产生低电平有效的空/满标志,其中异步满信号(afull)要同步到写时钟域 (wclk),异步空信号(aempty)要同步到读时钟域(rclk),以消除亚稳态的影响,并向外界输出同步的空/满信号。下面以满信号 (wfull)为例说明同步信号的产生过程:满信号afull是因为写地址追上了读地址并比读地址多循环一次所产生,此时不能再向FIFO中写入数据,否则会造成FIFO写溢出。由于写地址(wptr)的变化产生FIFO满标志afull,即afull的下降沿与wptr同属于写时钟域。当读地址增加时,表明已经从FIFO中读走了一个数据,afull由有效的低电平变为无效的高电平,即afull的上升沿与rptr同属于读时钟域。可见,afull由高变低与写时钟(wclk)同步,而由低变高则与读时钟(rclk)同步。由于满标志afull只影响FIFO的写入,故将其同步到写时钟域。如图6所示,采用双锁存器法将afull过渡到写时钟域,最后得到的满信号wfull就属于写时钟域。同理可以得到空标志信号rempty。用Verilog代码实现如下:

wire dirset=~((wptr[n]^rptr[n-1]) & ~(wptr[n-1]^rptr[n]));

wire dirrst=~((~(wptr[n]^rptr[n-1]) & (wptr[n-1]^rptr[n])) |~wrst);

always @(posedge high or negedge dirset or negedge dirrst)

if (!dirrst) direction <= 1′b0;

else if (!dirset) direction <= 1′b1;

else direction <= high;

assign aempty=~((wptr==rptr) && !direction);

assign afull=~((wptr==rptr) && direction);

always @(posedge rclk or negedge aempty)

if (!aempty) {rempty,rempty2} <= 2′b11;

else {rempty,rempty2} <= {rempty2,~aempty};

always @(posedge wclk or negedge afull)

if (!afull) {wfull,wfull2} <= 2′b11;

else {wfull,wfull2} <= {wfull2,~afull };

异步比较法的关键是用异步比较结果的信号的下降沿作为最终比较结果的复位信号,而其上升沿则用传统的双锁存器法进行同步[5]。最终得到的信号的上升沿与下降沿都属于同一个时钟域。与传统的先将地址信号同步再进行同步比较的方法相比,异步比较法避免了使用大量的同步寄存器,而效率则更高,实现也更简单。

2.3 保守的空/满标志

设计中FIFO空/满标志的设置是保守的,即FIFO空/满标志的置位是立即有效的,而其失效则是在一段时间之后。例如一旦读指针追上写指针,就会立即声明一个低电平有效的异步空信号aempty。此信号会立即把图6所示的set触发器置位,使触发器输出为1,即向外部输出同步的空信号rempty,并且保证了FIFO一旦为空,读指针就不增加,避免了FIFO的读溢出。当写地址增加时,表明FIFO已经非空,空标志aempty由低变高,此时 可以进行安全的读操作。aempty信号的失效与写时钟同步。空信号rempty是在读时钟域中同步aempty信号得到的。由于同步器使用了两个触发器,因此空信号rempty的失效要经过至少两个时钟周期的延迟。所以,空信号的声明是及时的,而空信号的失效是保守的。也就是说,虽然FIFO已经非空了,但是空信号rempty要经过几个周期的延迟才能变为无效。满信号也有类似的情况。

虽然空/满标志的设置是保守的,但这并不影响FIFO功能的正确性,经验证保守的空/满标志能够满足FIFO的设计要求。

3 仿真验证和综合

根据以上分析,以深度为16、数据宽度为8位的异步FIFO为例,用VerilogHDL编写了各个模块,并采用Synopsys公司的仿真工具VCS进行了仿真验证。设写时钟(wclk)周期为100MHz,读时钟(rclk)周期为 133MHz,FIFO写、读时序仿真结果分别如图7、图8所示。当FIFO写满时,满标志wfull马上由0变1,禁止写数据并且写地址也不再增加,FIFO只读不写;当FIFO读空时,空标志rempty马上由0变1,禁止读数据并且读地址也不再增加,FIFO只写不读。空/满信号的变化情况满足设计要求。

仿真验证通过后,采用Synopsys公司的Design Compiler工具进行综合。把采用异步比较法设计的FIFO与传统的先将地址信号同步再进行比较设计的FIFO相比较,在中芯国际0.35μm库上 DC综合结果如表1所示。可见相对于传统的异步FIFO,改进后的异步FIFO电路速度快、面积小,从而降低了功耗,提高了系统的稳定性。

为了解决数据在不同时钟域间传递所产生的亚稳态问题,本文讨论了一种新颖的异步FIFO设计方案。采用VerilogHDL以及由顶向下的模块设计方法实现了这种方案。经验证该方案能安全地实现数据跨时钟域的传递,并且性能比传统方案有了明显的改善。

参考文

posted on 2010-07-16 01:24 fpga_hjh 阅读(11943) 评论(2) 编辑 收藏 举报