转载 问题讨论:串入串出移位寄存器的可靠性?

迷 惑了吗?不迷惑?如果你知道是怎么回事了,就可以不用浪费时间继续看了.

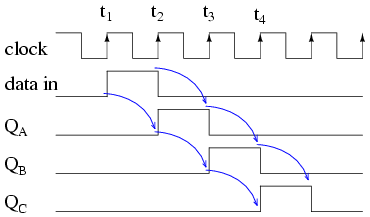

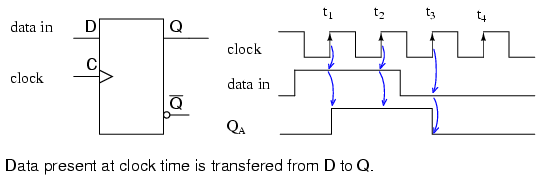

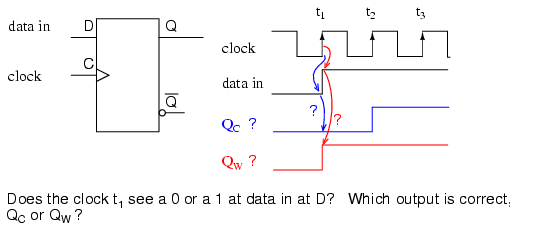

那 看看第2个图,移位寄存器的时序吧,第二个D触发器是否出现了上图所示的亚稳态?

事 实上,这个设计得到了大部分工程师的肯定,也有少两的学者认为它可靠性差.

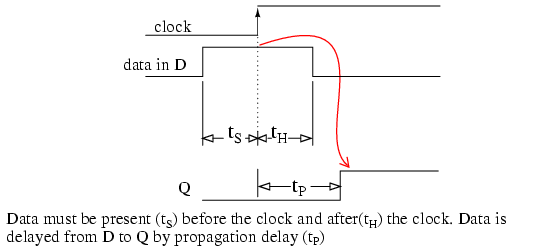

TS是建立时间,TH是保持时间,TP是传播时间,通常,同一工艺的D触发器TP>TH.

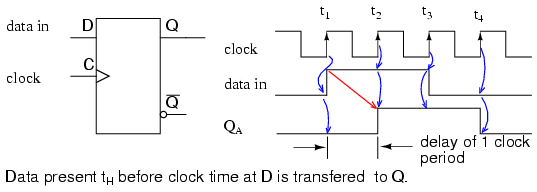

所 以,当D触发器的输入来自上一级(同一时钟)D触发器输入的时候,只要时钟半周>TS,TP>TH.

所以第一个图所示的串入串出移位寄存器就能正常工作.前题是,使用同一个时钟.

但 是大家可以想象,如果串入串出移位寄存器的D触发器所使用的时钟信号有些相位偏差的时候,且这些偏差TD大到一定程度的时候,TD>TP-TH的时 候,不稳定的情况又出现了.

浙公网安备 33010602011771号

浙公网安备 33010602011771号