8.时钟初始化

8.时钟初始化

ARM系统时钟初始化:

这就需要知道什么是时钟脉冲信号,什么是时钟频率,什么是时钟源。

-

时钟脉冲信号:

时钟脉冲信号:按一定的电压幅度,一定的时间间隔连续发出的脉冲信号。时钟脉冲信号是时序逻辑的基础,它用于决定逻辑单元中的状态何时更新。数字芯片中众多的晶体管都工作在开关状态,它们的导通和关断动作无不是按照时钟信号的节奏进行的

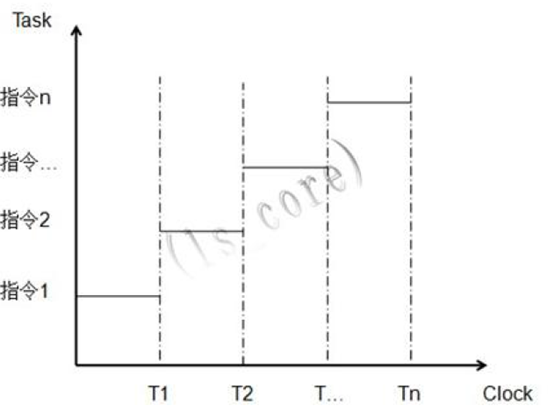

时钟脉冲图解:

1.2时钟脉冲频率:

时钟脉冲频率:就是在单位时间,如1秒,内产生的时钟脉冲个数。

1.3信号产生:

如何产生时钟信号:1.晶振2.锁相环PLL

1.3.1信号产生-晶振:

晶振全称晶体振荡器,是用石英晶体经精密切割磨削并镀上电极焊上引线做成。这种晶体有一个很重要的特性,如果给他通电,他就会产生机械振荡,他们有一个很重要的特点,其振荡频率与他们的形状,材料,切割方向等密切相关。由于石英晶体化学性能非常稳定,热膨胀系数非常小,其振荡频率也非常稳定,由于控制几何尺寸可以做到很精密,因此,其谐振频率也很准确。

晶体振荡器时钟的优点包括结构简单和噪声低,以及可为客户提供精确的定制频率等方面;但另一方面,它的缺点也比较明显,例如其频率仅由晶体决定,通常是特定晶体被制成客户所需的振荡器,导致生产成本高、交货周期较长,不利于客户加快产品上市时间,而且难以获得非标准的频率。

1.3.2信号产生-锁相环:

PLL(锁相环)合成器是一种更为复杂的系统时钟源。通用PLL合成器需要一个外部晶

体并包含一个能够对晶体的特定频率加倍或分频的集成锁相环(PLL)电路。

对这两种方式的对比:

典型的系统时钟振荡器源通常采用石英晶振,而更复杂的系统时钟振荡器源则是由PLL合成器提供。

1. 对于特定的时钟频率,采用PLL合成器可使用较便宜以及较低频率晶振来代替昂贵的高频晶振;

2. 对于需要多个时钟频率的系统,采用PLL合成器通过分频即可实现,而此时采用晶振模块则需要多个不同频率的晶振。

因此相对于晶体振荡器模块,通过PLL合成器提供精确时钟具有成本更低、占板面积更小等一系列优点。

学习一种处理器的时钟的通用的方法:

-

晶振的频率

-

时钟体系有多少PLL。

-

这些PLL产生多少时钟。

-

产生的时钟是用来做什么的。

![]()

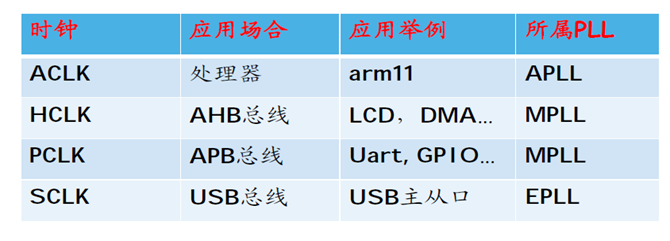

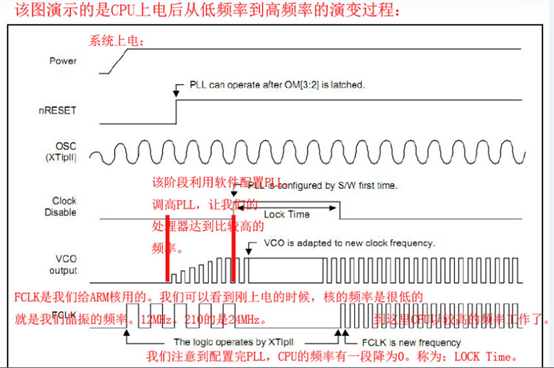

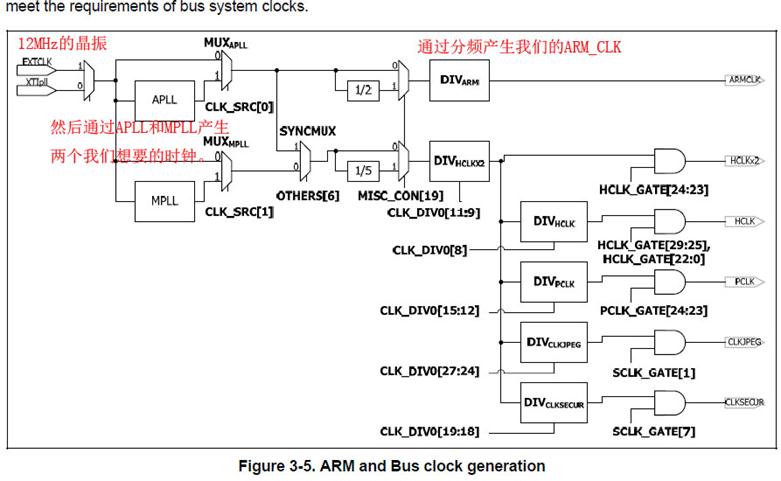

S3C6410可以使用外部晶振( XXTIpll )(默认为12MHZ)和外部时钟( XEXTCLK )两种方式输入时钟信号。它由跳线OM[0]决定。S3C6410 默认的工作主频为12MHz(晶振频率),S3C6410有三个PLL,分别为APLL、MPLL和EPLL。其中APLL产生ACLK,给arm core使用。MPLL产生HCLK和PCLK。EPLL产生特殊的时钟,比如为USB提供48MHz时钟。

![]()

2410的时钟:

![]()

6410:

![]()

![]()

时钟初始化软件的工作:

-

设置LOCK TIME

-

设置分频系数

-

设置CPU为异步工作模式

-

设置FLCK

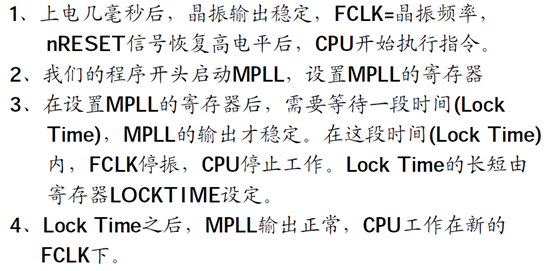

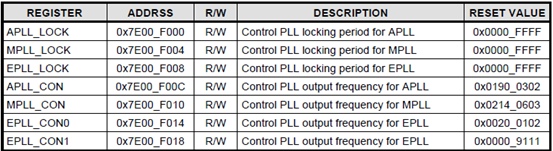

1、设置LOCK TIME

![]()

设置lock time是分别设置上面的APLL、MPLL、EPLL_LOCK的值。他们已经有了默认的值:0x0000_FFFF。对于默认值。当我们没有更好的方案。就默认。不去设置。

-

设置分频系数:

![]()

![]()

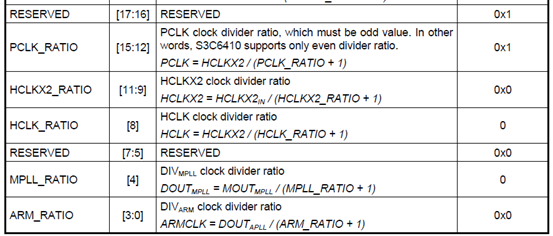

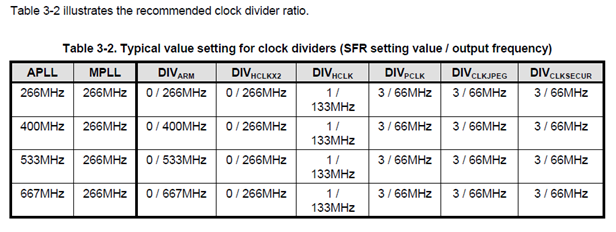

上面是四个CLK的计算公式:

ARMCLK=APLLOUT/(DIVARM+1)=533/(0+1)=533MHZ

HCLKx2=MPLLOUT/(DIVhclkx2+1)=533/(1+1)=266MHZ

HCLK=HCLKx2/(DIVhclk+1)=266/(1+1)=133MHZ

PCLK=HCLKx2/(DIVpclk+1)=266/(3+1)=66MHZ

上面就是四个时钟的产生的过程。

但是上面的那些因素的取值是:

![]()

这里我们参考uboot的设置:

![]()

![]()

ARMCLK=APLLOUT/(DIVARM+1)=533/(0+1)=533MHZ

HCLKx2=MPLLOUT/(DIVhclkx2+1)=533/(1+1)=266MHZ

HCLK=HCLKx2/(DIVhclk+1)=266/(1+1)=133MHZ

PCLK=HCLKx2/(DIVpclk+1)=266/(3+1)=66MHZ

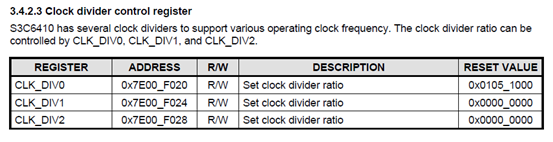

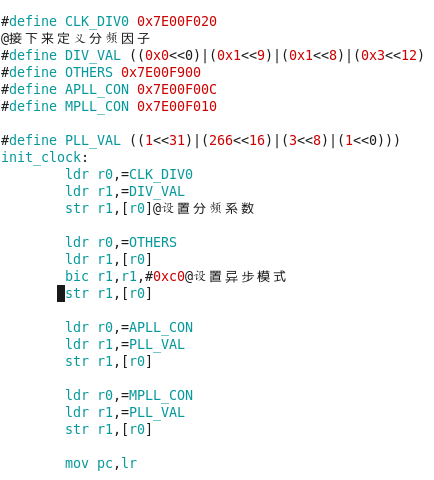

算好了值:接下来就是设置寄存器了。前面讲到的分频因子都是通过寄存器CLK_DIV0来定义的。

![]()

设置分频系数:

![]()

-

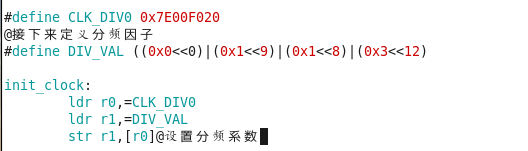

设置处理器,工作在异步模式:

我们在前面知道,要让cpu工作在异步模式,我们是去设置我们的cp15.但是在我们的6410中,存在一个寄存器,可以设置cpu工作在异步模式:

![]()

第7位就是设置同步或异步模式的,设置为0,就是异步模式:

![]()

从上面知道,我们把第六位也设置为了0,这是因为:

![]()

我们从上图知道OTHERS[6]=0的时候,才是使用MPLL,所以,我们把6,7都设置为0.

-

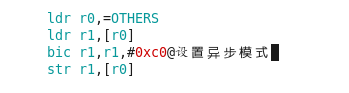

设置FCLK:

设置FCLK的频率,实际上就是等于设置我们的APLL和MPLL的输出频率:

![]()

上面有公式和参考值。我们的是12MHz,533MHz。

通过MPLL和APLL两个寄存器来设置:

![]()

![]()

![]()

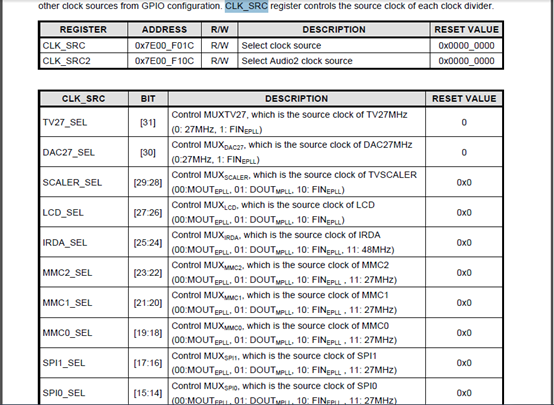

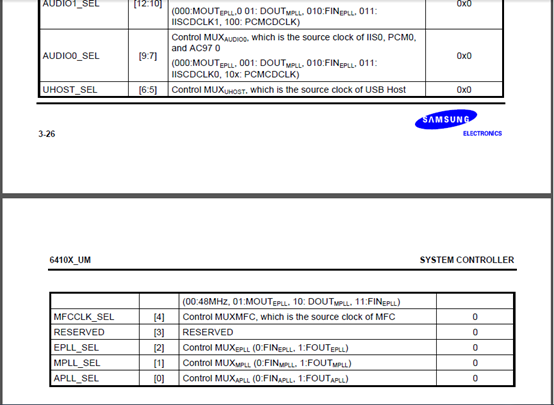

最后设置我们的时钟的源是来之APLL和MPLL,就是对应的位是1,才是使用该源设置:

![]()

![]()

![]()

我们是要通过MPLL和APLL和EPLL的源来设置时钟的。可是系统上电的时候,对应的位是0 的。所以我们需要把他设置为1.

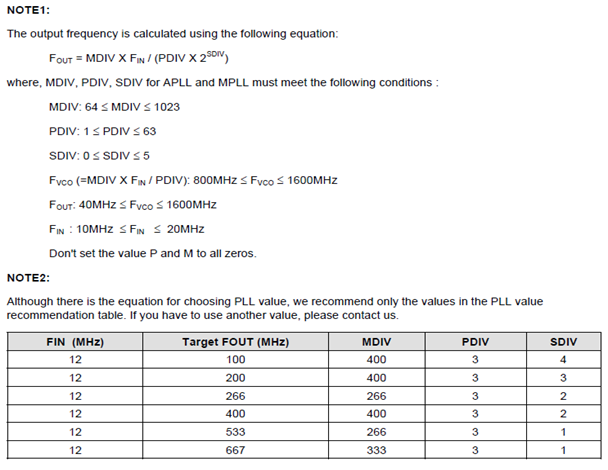

最后的代码:

![]()

浙公网安备 33010602011771号

浙公网安备 33010602011771号