【嵌入式面经专题】4-IIC协议

1. 概述

I2C(Inter-Integrated Circuit BUS) 集成电路总线,该总线由NXP(原PHILIPS)公司设计,多用于主控制器和从器件间的主从通信,在小数据量场合使用,传输距离短,任意时刻只能有一个主机等特性。

2. 物理层

只要求两条总线线路,一条是串行数据线SDA,一条是串行时钟线SCL。(IIC是半双工,而不是全双工)。

每个连接到总线的器件都可以通过唯一的地址和其它器件通信,主机/从机角色和地址可配置,主机可以作为主机发送器和主机接收器。

IIC是真正的多主机总线,(区别于SPI在每次通信前都需要把主机定死,而IIC可以在通讯过程中,改变主机),如果两个或更多的主机同时请求总线,可以通过冲突检测和仲裁防止总线数据被破坏。

传输速率在标准模式下可以达到100kb/s,快速模式下可以达到400kb/s。

连接到总线的IC数量只是受到总线的最大负载电容400pf限制。

3. 协议层

一、主机数据传输态

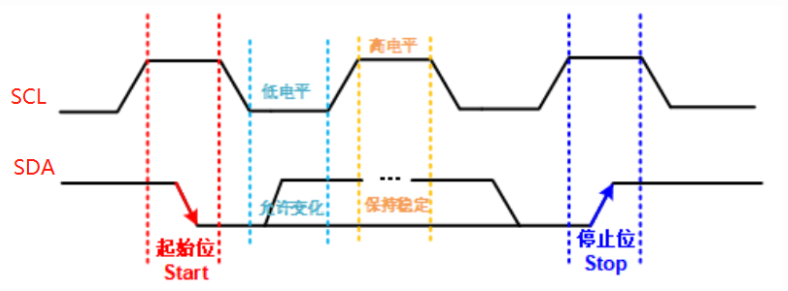

①开始条件:SCL高电平,SDA由高变低

②停止条件:SCL高电平,SDA由低变高

③数据发送状态:SDA电平保持稳定条件下,SCL变为高电平(此时进行“采样”)。

总结上面3点为一句话:

SCL为高电平时,SDA线若保持稳定,那么SDA上是在传输数据bit;若SDA发生跳变,则用来表示一个会话的开始或结束。

二、总线空闲态:SDA为高电平

疑问:

SDA为高电平有下面两种情况:

- 总线空闲态(SCL处于低电平)

- SDA高电平有效数据态(SCL处于高电平)

那么如何区分这两种情况呢?假如SDA为高电平有效数据态的时候,被当做空闲态被其他IC拉低该怎么办呢?

答:

I2C总体来将,就是SDA总线下降沿表示通讯开始(总线被占用),然后在时钟信号下传输信息,然后再将SDA总线上升沿表示通信结束(总线被释放)。

也就是说,如果数据通讯期间(直到当前产生结束信号),I2C总线会屏蔽掉其他Slave的拉低信号,(哪怕此时SDA表示为高电平,可被“误认为”是空闲状态)。

可以将I2C设想成这样一种场景——服务员为顾客点餐。

当有多个顾客要进行点餐的时候,服务员选择走到哪一个顾客桌边,在一段时间之内,就不能为其他顾客点餐了,直到这位顾客点餐完毕,都一直为这位顾客服务,而根本不理会其他顾客。

其中【服务员选择走到哪一个顾客桌边】就是I2C的仲裁机制:

当I2C总线上挂多个设备时,当各个设备SDA输出逻辑相同时,总线上的逻辑固定;当输出逻辑不相同时,输出逻辑为0的设备会抢到总线控制权,其它设备释放总线,发起stop信号。

三、从机应答信号:

应答信号: Master每发送完8bit数据后等待Slave的ACK。即在第9个clock,若“从IC”(Slave)发ACK,SDA会被拉低。

若没有ACK,SDA会被置高,这会引起Master发生RESTART或STOP流程。

四、 I2C 时序:

写:(一种普遍的版本,对于具体的外设有所不同)

1.主机发送开始条件

2.发送从机地址(7位 )+ 写(0)

3.从机会产生一个应答信号(一个CLK下,把SDA拉低)

4.主机得到应答信号,发送8位数据。

5.从机会产生一个应答信号

6.重复 4.5 过程,直到主机发送停止条件

读:(一种普遍的版本,对于具体的外设有所不同)

1.主机发送开始条件

2.发送从机地址(7位)+读(1)

3.从机会产生一个应答信号(一个CLK下,SDA拉低)

4.从机给主机发送8位数据

5.主机给从机发送应答

6.从机得到应答,接着发送8位数据。

7.重复5.6过程,直到主机不发送应答信号和产生停止信号

参考文章:

1. 《通信协议-I2C 》:https://www.cnblogs.com/zyly/p/17094178.html

2. 【I2C】I2C总线详解——硬件结构/时序/挂死解决方法:https://zhuanlan.zhihu.com/p/614031572

浙公网安备 33010602011771号

浙公网安备 33010602011771号