嵌入式相关记录

最近需要参与嵌入式开发,因此开始学习嵌入式相关知识,此处记录一些专业知识。以下记录以DSP相关内容为主,大部分内容来自网络。

名词解释

单片机(MCU)

MCU是微控制器单元(Microcontroller Unit)的简称,是一种集成了微处理器核心、存储器和输入/输出接口等功能模块的单芯片微型计算机系统。

MCU是一种集成电路芯片,它将中央处理器CPU、存储器(包括RAM和ROM)、计数器、I/O接口等集成在一块硅片上,形成一个完整的微型计算机系统。它主要用于控制和管理各种电子设备的功能,如家电、汽车电子、工业自动化设备等。

寄存器

寄存器确实是实际存在的硬件模块,通常集成在处理器内部或外设中。每个寄存器都有一个对应的地址值,通过这个地址,程序可以直接访问和操作寄存器,从而实现对硬件的控制和数据处理。

通过地址映射,我们可以通过直接再程序中操作对应地址的bit以达到控制寄存器的目的。

-

硬件实现:寄存器是由触发器等电路元件构成的,具有极快的读写速度,能够在一个时钟周期内完成数据的存取。

-

地址映射:每个寄存器在内存地址空间中都有一个特定的地址。通过使用这个地址,程序可以直接读取或写入寄存器的值。例如,使用特定的汇编指令或C语言中的指针来操作寄存器。

-

控制目的:寄存器用于控制各种硬件功能,例如:

- 设置外设的工作模式(如定时器、ADC、DAC等)。

- 读取外设的状态信息(如数据准备好、错误标志等)。

- 控制数据流(如选择输入/输出通道)。

优先级

嵌入式系统优先级主要分为抢占优先级和子优先级,它们共同决定了中断的响应和处理顺序。

抢占优先级

- 定义:抢占优先级是指中断之间嵌套关系的属性。当一个高抢占优先级的中断发生时,它可以中断当前正在执行的低抢占优先级的中断或任务,从而确保紧急或重要的事件能够得到优先处理。

- 特点:抢占优先级高意味着该中断可以抢占其他优先级更低的中断资源,以最快速度响应外部事件。

子优先级

- 定义:子优先级也被称为响应优先级或副优先级,是在相同抢占优先级的中断之间起作用的属性。当多个中断具有相同的抢占优先级时,子优先级用来决定这些中断的处理顺序。

- 特点:子优先级高的中断将先于子优先级低的中断被处理,这允许系统在处理中断时进一步细化处理的优先顺序,使得系统能够更加精确地响应多个同时发生的事件。

中断向量表

中断向量表是一个存储所有中断服务程序入口地址的表格,每个中断源都有一个对应的入口地址。当多个中断同时发生且优先级相同时,处理器会按照中断向量表中的顺序依次检查并响应这些中断。

EALLOW; // 关闭写保护 PieVectTable.XINT1 = &My_Ctrl; // 将中断处理函数绑定到中断向量号上 EDIS; // 开启写保护

中断

中断即CPU在处理程序时,由于发送了某些突然事件(外部或内部),引起CPU中止当前事件,转而去执行其他任务(中断处理程序),处理完毕后继续执行当前程序,这一过程即为中断。

中断分为三级:外设级、PIE级、CPU级

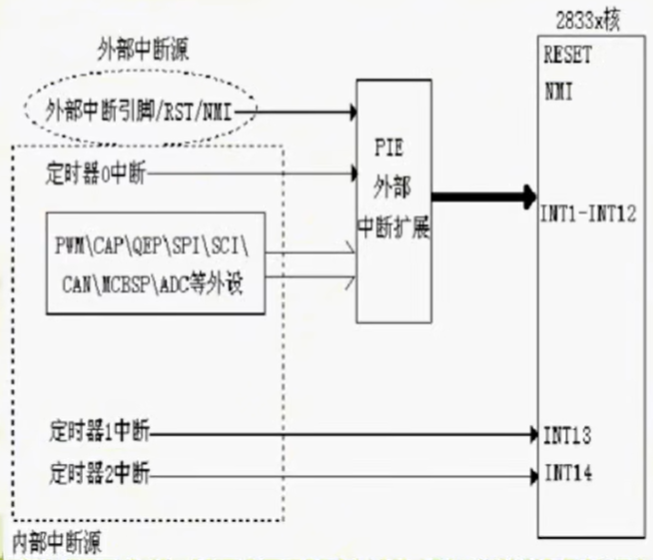

以F28335为例,其内部有16个中断线,其中包括2个不可屏蔽中断(Reset和NMI)与14个可屏蔽中断,其中2个中断线与两个定时器中断相连(为实时操作系统预留),12个中断线由PIE控制与外设相连,因此可分配多个(超过12个)外部中断设备到PIE,如下图:

PIE & IER

PIE(Peripheral Interrupt Expansion,外设中断扩展)是一个用于管理和处理外设中断的硬件模块。PIE 系统将外设中断分为多个组,每个组中的中断是相关联的,并且每个组有一个寄存器来控制这些中断的使能状态。通常,TI DSP 系统支持最多 8 组外设中断(PIE 组 1 至组 8)。

IER 全局中断使能寄存器,控制系统是否响应特定的外设组的中断。它的每一位对应一个 PIE 组 的全局使能。启用 IER 寄存器中的某一位后,相应的 PIE 组(如组 1、组 2 等)中的中断会被允许响应。例如,如果你设置 IER |= M_INT3;,那么系统会响应 PIE 组 3 的中断。

PIE 的中断管理通常依赖于一系列寄存器。以下是 PIE 相关的一些重要寄存器及其作用:

-

PIEIER (Peripheral Interrupt Enable Register):

- 该寄存器用于使能外设中断。

- 每个位对应一个外设的中断使能,当对应的位为 1 时,表示该外设的中断被使能。

- 例如,

PIEIER1.bit.INTx表示第 1 组外设的中断使能。

-

PIEIFR (Peripheral Interrupt Flag Register):

- 用于标识外设是否触发了中断请求。

- 每个位对应一个外设的中断请求标志,若为 1,表示该外设触发了中断请求。

- 需注意,该寄存器一般不能用程序设定,由硬件控制。

-

PIEACK (Peripheral Interrupt Acknowledge Register):

- 当 CPU 处理完中断后,必须通过该寄存器来 清除中断标志,并告诉 PIE 中断已经被处理。

- 每个中断组都需要通过

PIEACK来响应,清除对应的中断标志。

-

PIECTRL (Peripheral Interrupt Controller Register):

- 用于配置中断的优先级和处理逻辑。它可以控制不同外设的中断是如何被 CPU 处理的。

-

PIEIV (PIE Interrupt Vector Register):

- 该寄存器用于确定每个外设中断的中断向量,即处理程序的位置。它可以告诉 CPU 该跳转到哪个中断服务例程(ISR)。

示例如下:

假设你有一个 PIE 组 1,其中有 8 个外设中断源:

-

启用 PIE 组 1 的中断:

IER |= M_INT1;会使能 PIE 组 1 的中断,使得处理器可以响应该组的中断请求。

-

启用 PIE 组 1 中的第 3 个外设中断源:

PIEIER1.bit.INT3 = 1;会使能 PIE 组 1 的第 3 个外设中断源(例如 Timer 3)。

-

确认外设中断:

- 如果外设中断发生,

PIEACK(PIE 确认寄存器)需要清除相应的中断标志。一般来说,所有外设中断的确认是通过PieCtrlRegs.PIEACK.all = 0xFFFF;来进行的。

- 如果外设中断发生,

XINF

XINTF(External Interface)是德州仪器(TI)TMS320F28335 DSP中的一个外设,用于与外部存储器或外设进行通信。它提供了一种灵活的接口,可以连接各种类型的外部设备,如SRAM、NOR Flash、NAND Flash、EEPROM等

每个 XINTF 区域的读写访问时序都可以分成三个阶段,建立(Lead)、有效 (Active)、跟踪(Trail),每个阶段的时间都可以配置,以满足不同速度外部设备的时序要求。对 XZCS0 区域进行写操作时,XZCS0信号首先拉低,写选通信号 XWE0 随之拉低,数据送到数据总线XD上;进行读操作时,XZCS0 信号首先拉低,读选通信号 XRD 随之拉低,将数据从数据总线 XD 锁存到 DSP 中。片选信号XZCS0在读写访问时序的三个阶段中均为低电平,但读选通信号XRD与写选通信号XWE0仅在有效(Active)阶段时为低电平。

软件XINF配置参考如下:

SysCtrlRegs.PCLKCR3.bit.XINTFENCLK = 1; InitXintf16Gpio(); // XINTF 配置寄存器(XINTCNF2) EALLOW; XintfRegs.XINTCNF2.bit.XTIMCLK = 1; //XTIMCLK = 1/2 SYSCLKOUT // No write buffering XintfRegs.XINTCNF2.bit.WRBUFF = 0; //无写缓冲器 // XCLKOUT is enabled XintfRegs.XINTCNF2.bit.CLKOFF = 0; //使能XCLKOUT 所有的 XINTF 的操作都由 XCLKOUT 的上升沿开始 // XCLKOUT = XTIMCLK/2 XintfRegs.XINTCNF2.bit.CLKMODE = 1; //XCLKOUT = 1/2 XTIMCLK // 每个区域都有自己的时序寄存器,通过配置该寄存器可以改变本区域的访问时序 XintfRegs.XTIMING0.bit.XWRLEAD = 3; //写访问建立时间等待周期个数,以XTIMCLK时钟周期为基本单位 XintfRegs.XTIMING0.bit.XWRACTIVE = 7; //写访问有效时间等待周期个数,以XTIMCLK时钟周期为基本单位 XintfRegs.XTIMING0.bit.XWRTRAIL = 3; //写访问跟踪时间等待周期个数,以XTIMCLK时钟周期为基本单位 // Zone read timing XintfRegs.XTIMING0.bit.XRDLEAD = 3; //读访问,同上 XintfRegs.XTIMING0.bit.XRDACTIVE = 7; XintfRegs.XTIMING0.bit.XRDTRAIL = 3; // don't double all Zone read/write lead/active/trail timing // 该位指定寄存器XRDLEAD等实际值与寄存器设定值的比值 XintfRegs.XTIMING0.bit.X2TIMING = 0;//0-1:1;1-2:1 // Zone will not sample XREADY signal XintfRegs.XTIMING0.bit.USEREADY = 0; //忽略XREADY信号 XintfRegs.XTIMING0.bit.READYMODE = 0; //XREADY信号采样方式,仅在USEREADY = 1时有效 // Size must be either: // 0,1 = x32 or // 1,1 = x16 other values are reserved XintfRegs.XTIMING0.bit.XSIZE = 3; //数据总线宽度设定 1-32,3-16

上述代码中,对读写访问的时序大小设置需注意,0为1个XTIMCLK时钟周期。所有的 XINTF 的操作只能在 XCLKOUT 上升沿进行,具体时序可参考下图。

可看到当XCLKOUT=XTIMCLK/2,即二分频时,由于跟踪时序结束时XCLKOUT为下降沿,XINTF无法直接进入建立时序,因此存在一段校准周期

NMI

NMI(Non-Maskable Interrupt,非屏蔽中断)是一种特殊类型的中断,具有 不能被屏蔽(禁用)或 忽略 的特性。它是一种比普通中断具有更高优先级的中断,即使系统处于中断关闭的状态,NMI 也能够打断当前的操作并立即执行。

RCC

RCC(Reset and Clock Control)是STM32微控制器中用于复位和时钟控制的模块,负责管理系统时钟的生成和分配,以及控制外设的复位和时钟开启/关闭。

主要功能包括:

- 时钟源选择:RCC可以选择不同的时钟源,如内部振荡器、外部晶振等,以满足系统不同工作状态的需求。

- 时钟配置:RCC可以配置主时钟、外设时钟等,通过设置分频因子来调整时钟频率,以适应不同外设的工作频率需求。

- 复位控制:RCC负责系统的复位操作,确保系统从确定的状态开始运行,可以通过外部复位引脚或内部软件命令触发系统复位。

- 时钟使能/禁用:RCC可以动态地开启或关闭外设的时钟,以节省功耗。

GPIO

GPIO是通用输入输出端口,是嵌入式系统中非常重要的基本硬件资源之一。

它可以被配置为输入或输出模式,用于读取外部设备的信号或控制外部设备的工作状态。

在输入模式下,GPIO可以采集外部器件的信息,如传感器、开关等的状态。

在输出模式下,GPIO可以控制外部器件的工作,如LED灯、继电器等。

GPIO(General Purpose Input/Output)的上拉和下拉是指通过外部电阻或内部电路来控制GPIO引脚的电平状态。

-

上拉:当GPIO引脚悬空时,通过一个电阻连接到电源(Vcc),使得引脚默认为高电平。这种方式可以确保在没有外部信号驱动时,引脚保持高电平状态。

-

下拉:当GPIO引脚悬空时,通过一个电阻连接到地(GND),使得引脚默认为低电平。这种方式可以确保在没有外部信号驱动时,引脚保持低电平状态。

SPI

SPI,全称为串行外设接口(Serial Peripheral Interface),是一种同步串行数据连接标准。SPI是Motorola公司提出的一种同步串行接口技术,允许单片机与各种外围设备以串行方式进行通信和交换信息。

SPI系统通常由4条线组成:串行时钟线(SCK)、主机输入/从机输出数据线(MISO)、主机输出/从机输入数据线(MOSI)和低电平有效的从机选择线(NSS)。

SPI是一个环形总线结构,数据在主和从之间串行地传输,高位在前。

DMA

DMA(Direct Memory Access)控制器是一种在系统内部转移数据的独特外设,可以将其视为一种能够通过一组专用总线将内部和外部存储器与每个具有DMA能力的外设连接起来的控制器。

DMA是直接内存访问的缩写,它允许某些设备直接访问系统内存,而无需经过CPU的干预。当设备需要传输数据时,它会向DMA控制器发送请求。DMA控制器接收到请求后,会向CPU发出一个中断信号。CPU收到中断信号后,会暂停当前的工作,并将总线控制权交给DMA控制器。DMA控制器接管总线后,开始直接从源地址读取数据并写入目标地址,直到数据传输完成。数据传输完成后,DMA控制器会释放总线控制权,并将其交还给CPU。

PWM

PWM(Pulse Width Modulation,脉冲宽度调制)是一种模拟控制方式,通过调节方波的占空比来对模拟信号进行编码。

PWM是一种基于采样控制理论的技术,通过调整方波的高电平时间与周期的比例(即占空比),来模拟输出不同的电压或电流值。这种方式可以用于能量转换、功率控制和信号传输等多个领域。

在PWM中,载波信号的频率保持不变,而其占空比(高电平时间与周期的比例)根据调制信号的振幅变化而变化。当调制信号的振幅发生变化时,PWM波形的占空比也相应变化,从而实现对输出信号的控制。

ePWM

ePWM是用于生成PWM信号的硬件模块,它的作用是控制信号的占空比。

ePWM 的时基模块 (TB)主要负责控制 PWM 信号的周期性工作。时基模块相当于是 ePWM 的“时钟”,它控制着 PWM 信号的生成频率和周期,并且根据设定的参数自动生成周期性变化的输出信号。

ePWM 时基模块通常由以下几个部分组成:

-

周期寄存器(PRD):这是一个决定 PWM 信号周期的寄存器。时基模块会从 0 计数到这个周期值,然后再从 0 重新开始计数。周期寄存器的值决定了 PWM 信号的频率。比如,如果周期寄存器设置为 1000,那么时基模块会在每 1000 个时钟周期后重置,形成一个 PWM 信号周期。

-

计数器(CNT):计数器是一个用于跟踪当前 PWM 周期进度的寄存器。它从 0 开始计数,直到达到周期寄存器的值,计数器重置为 0,重新开始计数。

-

比较寄存器(CMP):比较寄存器用来设置 PWM 信号的占空比。它会与计数器的当前值进行比较,当计数器的值小于比较寄存器的值时,PWM 输出为高电平,当计数器的值大于比较寄存器的值时,PWM 输出为低电平。比较寄存器决定了高电平和低电平的时间比例,也就是占空比。

-

时钟源(Clock Source):时基模块的计时是基于时钟源的。时基模块可以选择使用内部时钟、外部时钟或其他来源作为其计时基础。

ePWM的计数比较模块 (CC)负责控制PWM信号的生成,包括确定PWM信号的周期和占空比。计数比较模块通过比较一个计数器的值和一些配置的比较值来生成PWM输出信号的高低电平。

计数比较模块的基本作用是:将计数器的当前值与一个或多个比较值进行比较,然后根据比较结果生成PWM信号的高电平和低电平。具体的操作步骤如下:

-

计数器计数:ePWM模块的计数器开始从0计数,直到达到设定的周期值。每当计数器的值增加时,ePWM会不断比较计数器的值和预设的比较值。

-

比较值:ePWM允许我们设置一个或多个比较寄存器,这些寄存器包含了我们设置的比较值。常见的比较寄存器包括:

- CMPA:第一个比较寄存器

- CMPB:第二个比较寄存器

- CMP(高低比较):在某些高级模式下,可以设置多个比较寄存器来控制更复杂的PWM输出。

-

信号生成:计数器的当前值与比较寄存器的值进行比较,生成PWM输出:

- 当计数器的值小于比较寄存器的值时,PWM信号输出高电平(逻辑1)。

- 当计数器的值大于比较寄存器的值时,PWM信号输出低电平(逻辑0)。

-

占空比控制:通过设置比较值(CMPA),我们可以控制PWM信号的占空比(即高电平的持续时间与周期的比例)。例如,如果比较值为周期的一半,那么PWM信号的占空比就是50%。

-

对称和非对称模式:ePWM模块支持多种模式来生成不同的PWM波形:

- 非对称模式:PWM信号的高电平和低电平时间不对称,比较寄存器只控制一个方向(例如高电平时长)。

- 对称模式:PWM信号的高电平和低电平时间对称。通过设置CMPA和CMPB的比较寄存器,可以控制PWM信号在周期内的高低电平分布。

在ePWM的计数比较模块中,最重要的寄存器包括:

-

CMPA(比较寄存器A):这是第一个比较寄存器,用来设置PWM的占空比。如果计数器的值小于CMPA的值,PWM信号为高电平;否则为低电平。

-

CMPB(比较寄存器B):这是第二个比较寄存器,通常用于生成对称PWM信号,或者用于双向PWM控制。

-

TBCTR(时基计数器):时基计数器保存当前的计数值,用于生成PWM信号周期。

-

TBPRD(时基周期寄存器):这个寄存器存储PWM信号的周期值,计数器从0开始计数,直到TBPRD的值。

-

EPwmXRegs(ePWM寄存器集):这些寄存器用于控制PWM模块的各个方面,例如占空比、周期、对齐方式等。

ePWM的动作限定模块(AQ)主要负责在特定的时刻根据设定的条件,控制PWM信号输出的高电平、低电平,或是触发事件(例如输出一个特定的状态信号)。这个模块使得PWM输出可以更加灵活地控制,能够应对一些复杂的应用需求。

ePWM模块的动作限定控制寄存器主要包括:

- AQCTLA(Action-Qualifier Control Register A):控制PWM信号的上升沿和下降沿行为。比如当计数器达到某个值时,可以设置输出为高电平,或者设置输出为低电平。

- AQCTLB(Action-Qualifier Control Register B):与AQCTLA类似,但它主要用于控制对称PWM模式(两路PWM信号),提供对两个通道的PWM信号的边沿控制。

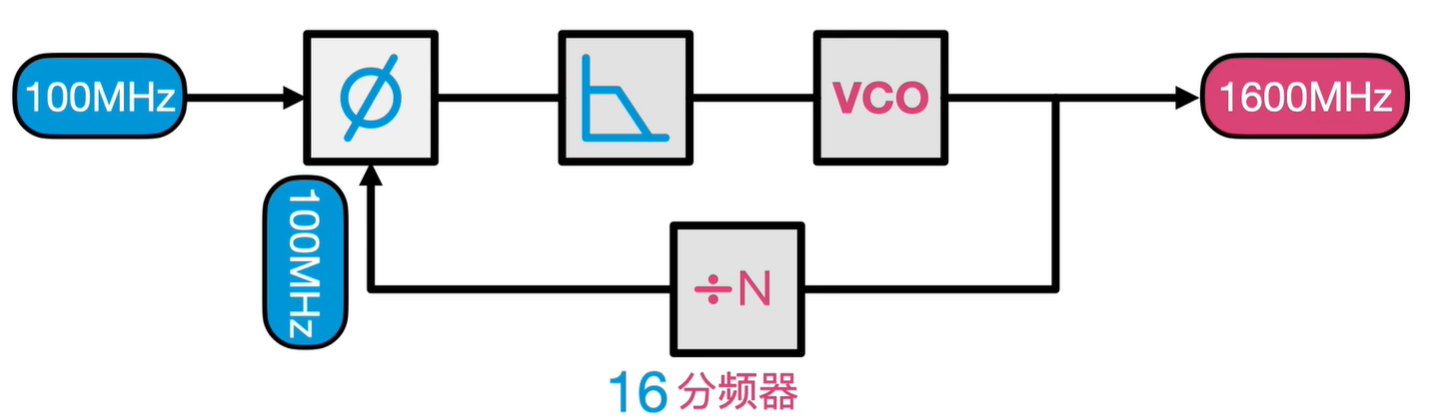

锁相环

锁相环(Phase-Locked Loop, PLL) 是一种用于同步信号相位的控制系统。它在电子学和通信系统中非常重要,广泛应用于频率合成、时钟生成、信号同步等场景。

锁相环一般用于倍频,即将低频率晶振频率加倍到高频率供芯片使用,其可以提供稳定平滑的频率信号。

一个典型的锁相环系统由以下三个主要部分组成:

-

鉴相器(Phase Detector, PD):

- 比较输入信号和本地振荡信号的相位差,并输出相位差信号。

- 如果输入信号的相位超前或滞后,本地振荡器的频率将被调整,以尽量消除这种相位差,使得两个信号保持相位同步。

-

环路滤波器(Loop Filter):

- 过滤掉鉴相器输出的高频成分,保留相位误差信号的直流或低频部分。

- 控制系统的动态响应特性,使其能够平滑和稳定地调整频率。

-

压控振荡器(Voltage-Controlled Oscillator, VCO):

- 接收环路滤波器的输出电压信号,并根据该电压调整自身的振荡频率。

- 目标是让 VCO 的输出频率跟随输入信号频率,并实现相位锁定。

- 初始状态:当输入信号进入锁相环时,鉴相器比较输入信号和 VCO 输出信号的相位。

- 反馈调整:鉴相器输出的相位误差信号经过环路滤波器,传递给 VCO 以调整输出频率。

- 相位锁定:随着反馈过程的进行,VCO 的输出频率逐渐逼近并锁定到输入信号的频率上,使得两者的相位差趋于恒定。此时,系统达到锁相状态。

想象你在游泳池游泳,每当听到教练的哨声你就潜水再浮出水面,这样你和哨声的节奏保持一致。如果哨声加快或减慢,你也会跟着调整节奏。锁相环就像这样自动调整自己的节奏(频率),去追随并锁定输入信号的频率和相位,从而保持同步。

RMS

均方根(RMS,Root Mean Square)是一种数学统计值,用于表示一组数值的平均大小。它通常用于电气和信号处理领域来描述交流信号(如电压和电流)的有效值。RMS 是通过以下方式计算的:

- 取平方:对每个数据点的值进行平方。

- 取均值:对所有平方后的数值求平均。

- 开平方:对所得平均值开平方根,得到 RMS 值。

其公式为:

其中,N 表示数据点的数量,xi 表示每个数据点的值。

在电力系统中,RMS 值常用于表示交流电的“有效值”,这是因为交流电是随时间变化的,瞬时电流或电压不恒定。而 RMS 值表示一个等效的直流电值,能传递相同的能量。例如,家庭电压常说是 220V 交流电,实际上这个 220V 是 RMS 值,而其峰值电压会更高。例如:

- 电流或电压的 RMS 值:RMS 值可以帮助测量器件的实际功耗。

- 信号的 RMS 值:在音频和其他波形信号中,RMS 可用于衡量信号的“强度”或“幅度”。

因此,RMS 是一个实际应用广泛的指标,用于反映随时间变化的数据或波形的平均“有效”大小。

LPF

Low-Pass Filter低通滤波器,低通滤波器允许低频信号通过,同时衰减高频信号。例如,在电压信号处理中,LPF 可用于去除高频噪声,保留信号的有效信息。

HPF

High-Pass Filter高通滤波器,

高通滤波器的主要作用是去除信号中的低频分量,仅保留高频分量。例如:

- 在电力系统中,用于去除信号中的直流分量,检测快速变化的电流或电压。

- 在音频信号处理中,HPF 可滤除低频噪声。

- 在传感器数据处理中,HPF 可以滤除一些不必要的低频噪声,保留快速变化的信息。

USART

USART(Universal Synchronous/Asynchronous Receiver/Transmitter)是一种通用的串行通信接口,用于在微控制器和外部设备之间进行数据传输。

USART是一种全双工、异步或同步串行通信协议,广泛应用于嵌入式系统中,用于实现微控制器与其他设备之间的数据传输。它支持数据的发送和接收,并具有多种配置选项,如波特率设置、数据位长度、停止位长度等。

RAM & FLASH

随机存取存储器(RAM),具有较快的存取速度,是易失性存储器,断电后数据会丢失。

闪存(Flash Memory),读取速度不如RAM快,是非易失性存储器,断电后数据仍然保存。

RAM和FLASH都可以作为启动介质,RAM启动因其高速和临时性特点,适合快速原型开发和调试;而FLASH启动则因其非易失性和稳定性,更适合产品化应用。

DSP中,RAM启动后程序从地址0x0000 0000开始执行;FLASH启动后程序从0x0008 0000开始执行。

不连接仿真器情况下,需注意GPIO72和GPIO84引脚电平,两者拉高后可对0x0000 0D00寄存器值的高两位进行修改,具体参考DSP手册。

Bootloader

引导加载程序(Bootloader),它是系统加电后运行的第一段软件代码。Bootloader的主要作用是将操作系统从存储设备(如硬盘、SSD或闪存)加载到内存中,并将控制权交给操作系统,以便其接管系统的运行。

工程文件架构

-

cmd:此文件夹包含链接命令文件(*.cmd),用于描述系统实际的硬件资源和段的定位。这些文件告诉链接器如何计算地址和分配空间。例如,MEMORY命令定义了系统的存储区域,SECTIONS命令描述了各段如何放置在这些区域内。

-

Debug:这个文件夹是系统自动生成的,用于存放编译后产生的文件。包括可执行代码文件(.out文件)和其他调试信息。

-

include:该文件夹包含头文件(*.h),通常由TI公司提供,用于定义DSP芯片的寄存器数据结构。头文件可以进行宏定义、变量和函数声明。开发者也可以自己创建头文件并添加到此文件夹中。

-

lib:此文件夹存放库文件(*.lib),如C语言实时运行支持库文件(rts.lib)和芯片支持库文件(csl.lib)。库文件用于建立C运行环境以及实现片内外设的操作。例如,rts.lib包含ISO运行支持库,而csl.lib则方便对DSP器件的片内外设进行操作。

-

common文件夹:这个文件夹通常用于存放与DSP资源有关的库函数、头文件等通用文件。它包含了一些与DSP芯片相关的宏定义、预编译头文件以及运算库文件等。这些文件是工程项目的基础,方便开发者快速进行DSP资源的控制和代码的编写,提高开发效率。

- targetConfig文件夹:这个文件夹用于存放与仿真器有关的目标配置文件,其后缀为.ccxml。这些文件定义了使用的下载器型号、目标芯片型号等信息。在CCS软件中,通过这些配置文件可以设置仿真器的参数,以确保仿真器与开发板正确连接并进行程序调试或烧写操作。

- source文件夹:用于存放源文件,这些源文件通常是以.c或.asm为后缀的文件,包含了实现DSP系统指定功能的主要代码部分

C程序相关

以下内容与TMS320F28x相关

关键字

interrupt

该关键字修饰函数,表明函数是一个中断服务程序。当特定的硬件或软件中断发生时,CPU会跳转到这个函数执行相应的处理。

register

该关键字用于声明局部变量,并提示编译器尽可能将这些变量存储在CPU寄存器中,以提高访问速度。

需注意,cregister是特定于某些DSP编译器(如TI的C28x编译器)的扩展关键字,用于直接访问和控制CPU的控制寄存器。在DSP开发中使用cregister而不是标准的register关键字,主要是为了利用DSP编译器提供的特定扩展功能,以便更直接、高效地访问和控制CPU的控制寄存器。

寄存器

GpioCtrlRegs

对Gpio进行操作时,一般先开启Gpio时钟(InitSysCtrl函数一般会使能),再对MUX进行功能设置,再对DIR方向设置,再对PUD进行上拉设置。示例如下:

GpioCtrlRegs.GPBMUX2.bit.GPIO48 = 0; //GPBMUX2控制GPIO Bank B(即GPIO48到GPIO63) GpioCtrlRegs.GPBDIR.bit.GPIO48 = 1; //方向输出 GpioCtrlRegs.GPBPUD.bit.GPIO48 = 0; //上拉开启设置

中断注意

为确保进入中断函数后,中断函数不会被其他中断函数截断(确保优先级),同时不会重入(自己截断自己),则应该在中断函数开始添加以下内容。以下以epwm对应中断函数为例:

volatile Uint16 TempPIEIER = PieCtrlRegs.PIEIER3.all; //读取PIE Group 3的中断使能 | PIE Group 3内为EPWMn_INT_ISR中断 IER |= M_INT3; //IER中断使能寄存器,此处启用PIE组3的中断(CPU级) IER &= ~M_INT3; // 此处禁用除组3外的其他中断(CPU级) PieCtrlRegs.PIEIER3.all &= MG31; // 禁止pie组三中断 -> PieCtrlRegs.PIEIER3.all=0 此处确保组三不会在执行期间再次触发(PIE级) PieCtrlRegs.PIEACK.all = 0xFFFF; // Enable PIE interrupts PIEACK是PIE中断确认寄存器,用于清除和确认所有PIE中断。此处相当于启用PIE系统的所有外设中断。(PIE级) EINT;

链接器相关

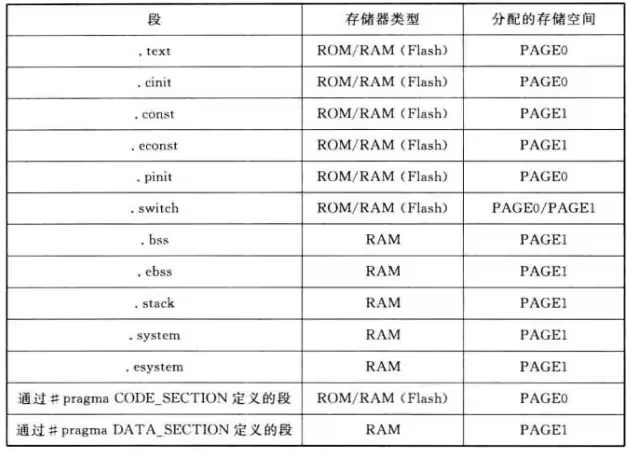

程序和数据段会被组织成不同的块或段,每个段都有特定的目的,主要分为已初始化段和未初始化段。

已初始化段

.text C语言编译后生成的二进制指令代码段。我们编写的main主函数,子函数或子程序,中断服务程序,都会产生指令代码,都属于这个段;

.cinit 存放初始化的全局和静态变量;

.const 字符串常量和const定义的全局和静态变量;

.econst 字符串常量和far const定义的全局和静态变量;

.pinit 全局变量的构造函数(C++语言)程序列表,在新标准中有时用.init_array段表示;

.switch 存放switch语句产生的常数表格;

.vectors 中断向量段,也就是中断服务程序的入口地址段。

未初始化段

.bss 为全局变量和局部变量保留的空间,在程序上电时.cinit空间中的数据复制出来并存储到.bss空间中;

.ebss 为使用大寄存器模式时的全局变量和静态变量预留的空间,在程序上电时,cinit空间中的数据复制出来并存储在.ebss中;

.stack 堆栈空间,主要用于函数传递变量或为局部变量分配空间;

.sysmem 为动态存储分配保留的空间(malloc),如果有宏函数,此空间被占用;

.esysmen 为动态存储分配保留的空间(far malloc),如果有far函数,此空间会被占用。

此外,还可以用# pragma自定义段(CODE-SECTION用来定义代码段,而DATA SECTION用来定义数据段):

# pragma CODE SECTION(symbol, "section name"); # pragma DATA SECTION(symbol,"section name").

链接器相关

链接器对块的处理有两个功能:其一,将COFF目标文件中的块用来建立程序块和数据块,并将这些块组合成可以被DSP芯片执行的COFF输出模块;其二,链接器为输出块指定存储位置。

链接器提供两个命令实现上述功能:MEMORY和SECTIONS。MEMORY命令定义目标系统的存储器,程序员可以定义每一块存储器并指定起始地址和长度;SECTIONS命令用来定义输入块的组合和输出块在存储器中的存放位置。若不用MEMORY和SECTIONS命令,链接器采用缺省的分配算法。推荐使用这两个命令,但要注意这两个命令在CMD文件(链接器命令文件)中使用。

个人理解:MEMORY命令定义的是目标硬件上的实际物理存储器区域。它不是创建虚拟的存储空间或类似于指针的概念;而是直接映射到嵌入式设备中真实存在的ROM、RAM等存储器资源。可以说MEMORY和SECTIONS命令帮助开发者精确地控制程序的内存布局,使得程序能够有效地利用嵌入式系统的有限资源,这一切都是基于对物理存储器的真实映射和安排,CMD文件为链接器提供了详细的指令,指导其如何将编译后的目标文件组合成最终的可执行文件,并且对这些文件中的各个段进行布局和定位。

常见预处理指令

CODE_SECTION

在嵌入式编程中,使用 #pragma CODE_SECTION 可以有效地控制代码的存放位置,优化程序性能。例如,在实时应用中,可能希望将时间敏感的代码放在 RAM 中,以减少延迟。使用此指令后,编译器在生成可执行文件时会根据这个指示将 Main_Ctrl 函数放在 RAM 中执行。代码如下所示:

#pragma CODE_SECTION(Main_Ctrl,"ramfuncs");

相关知识点记录

DSP每个地址下对应的数据是16bit,而ARM对应数据是8bit。

芯片引脚通常具有多功能性,可以根据配置在不同的模式下工作。在嵌入式系统和微控制器中,很多引脚会被设计为多用途,既能作为通用输入输出(GPIO),也能在特定模式下提供其他功能,比如通信接口、定时器、模拟功能等。

参考文章:

https://zhuanlan.zhihu.com/p/62282752?utm_id=0

https://www.chinaaet.com/article/46612

浙公网安备 33010602011771号

浙公网安备 33010602011771号