一、间隔定时器结构

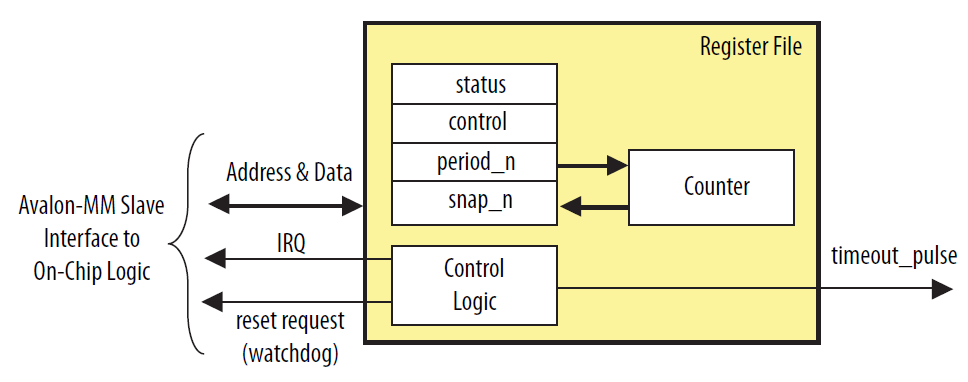

间隔定时器的结构框图:

该间隔定时器有如下两个特点:

- Avalon-MM接口,提供对6个16位寄存器的访问;

- 有一个脉冲输出接口(可选),可用作周期性脉冲发生器;

该间隔定时器的所有寄存器都是16位的,可兼容16-bit和32-bit处理器。某些寄存器只存在于特定的配置中,例如,当该间隔定时器配置为固定周期,那么period寄存器就不存在。

以下序列描述了间隔定时器的基本行为:

- Avalon-MM主设备可通过 control 寄存器实现以下行为:

- 启动和停止定时器;

- 使能或禁用IRQ;

- 指定count-down once或者continuous count-down模式;

- 处理器可通过读取 status 寄存器来获取当前定时器的行为;

- 处理器可通过向 period 寄存器写入特定的值来指定定时器的周期;

- 当内部的计数器计数到0时,会立即从 *period* 寄存器中重新加载计数值;

- 处理器可通过如下方式读取当前内部计数器的计数值:首先对 *snap* 寄存器执行写操作,然后再对 snap 寄存器执行读操作,就可以获得当前内部计数器的计数值;

- 当计数到0时,会触发以下一个或多个事件:

- 若使能了IRQ,则会生成一个IRQ;

- 脉冲发生器输出接口(可选)会输出一个时钟周期的有效值;

- 看门狗输出会使系统复位。

二、间隔定时器寄存器描述

Interval Timer寄存器描述:

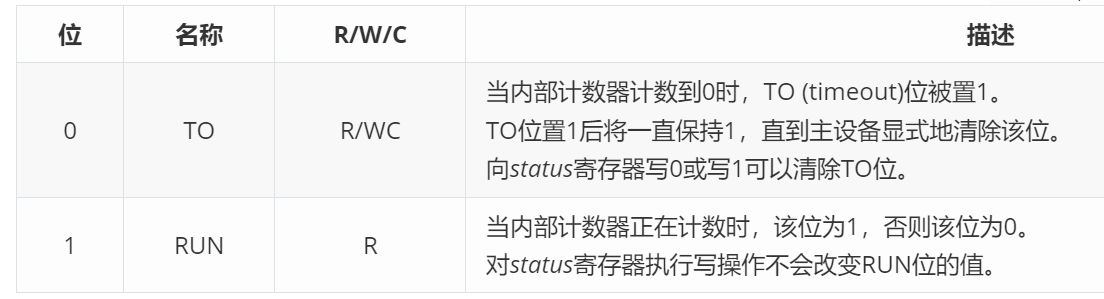

status寄存器有2个域:

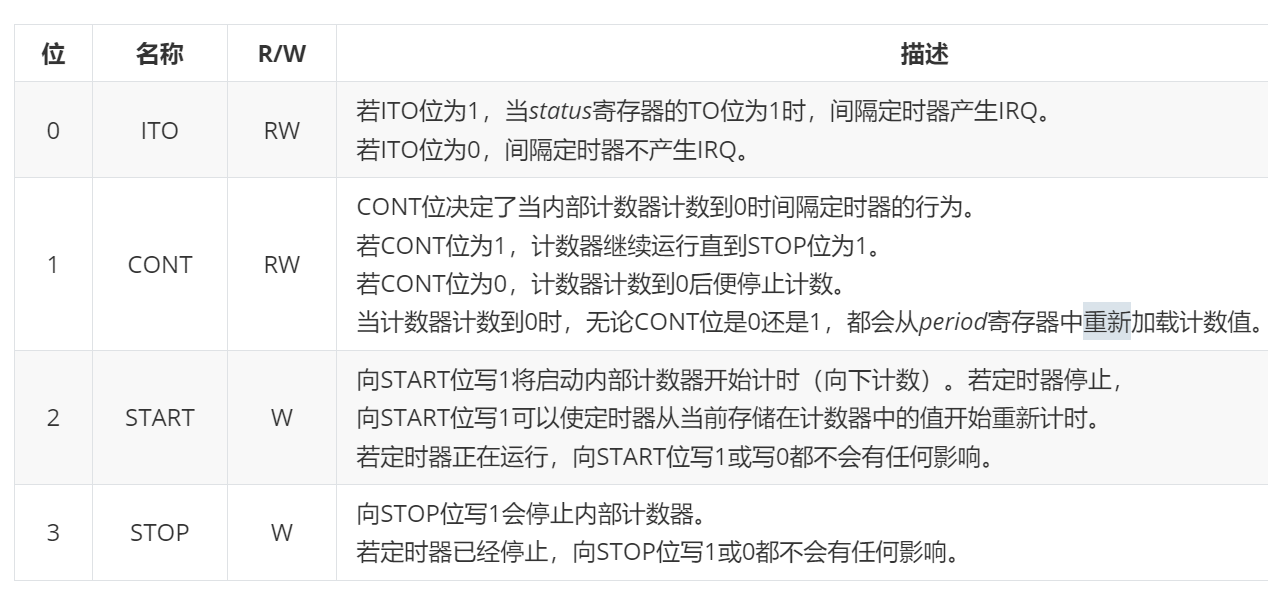

control寄存器有4个域:

period 寄存器

periodl 和 periodh 寄存器共同存放了计数器的初始计数值。当下列情况之一发生时,内部计数器就会加载 periodl 和 periodh 寄存器中的值:

-

对 periodl 或 periodh 寄存器执行写操作;

-

内部计数器计数到0。

snap 寄存器

主设备可以通过对 snapl 或 snaph 寄存器执行写操作(写数据被忽略)来读取当前内部计数器的值。执行写操作后,内部计数器的值便会存放在 snapl 和 snaph 寄存器中。无论内部计数器是否正在计数,对 snapl 或 snaph 寄存器执行写操作都可以获取内部计数器的值,并且此操作不会影响内部计数器的行为。

三、间隔定时器的中断

当内部计数器计数到0,并且 control 寄存器的 ITO 位为1时,间隔定时器会产生中断IRQ。可通过以下两种方式对IRQ进行应答:

-

清除 status 寄存器的 TO 位;

-

通过清除 control

四、间隔定时器

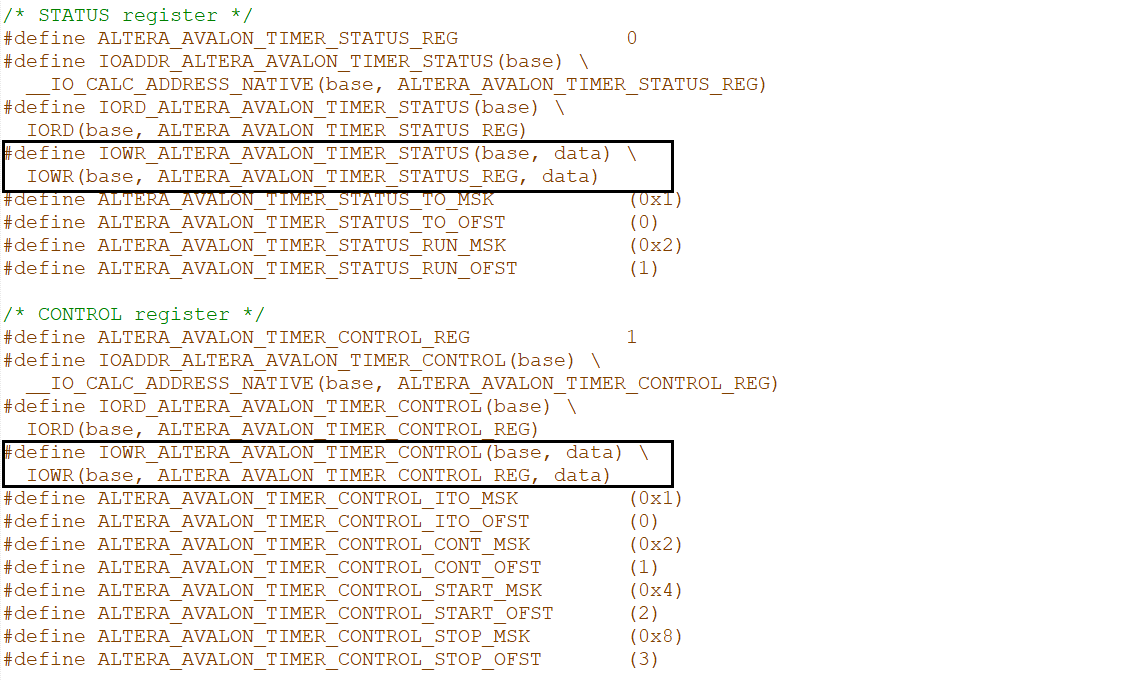

定时器寄存器文件位于Quartus Prime软件安装路径下的...\intelFPGA\22.1std\ip\altera\sopc_builder_ip\altera_avalon_timer\inc文件夹中。

主要用了定时器的状态寄存器和控制寄存器中的两个函数:

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步