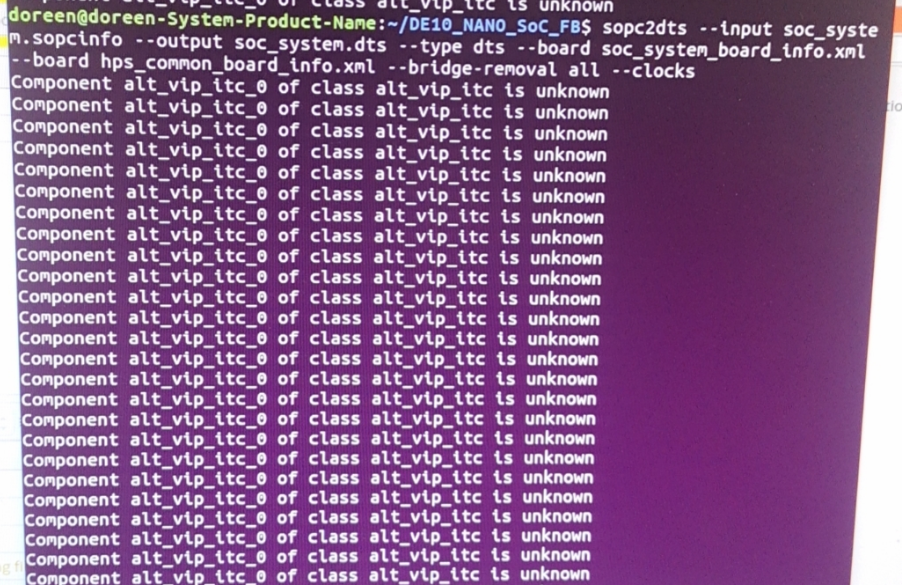

当使用DE10_NANO_SOC_FB工程产生dts时提示 Component alt_vip_itc_0 of class alt_vip_itc is unknown:

如果此时生成了dtb, 可以忽略这个提示。

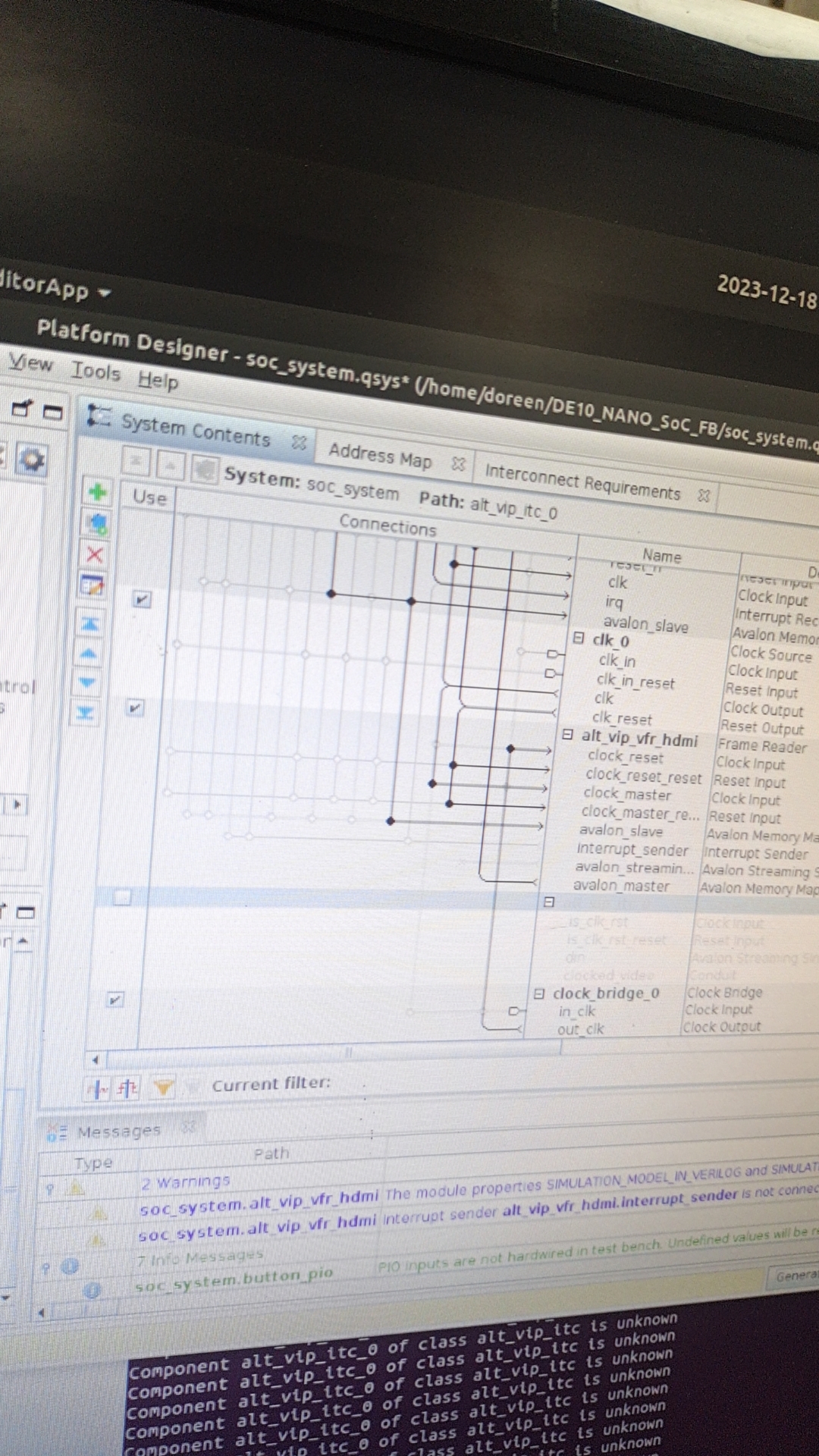

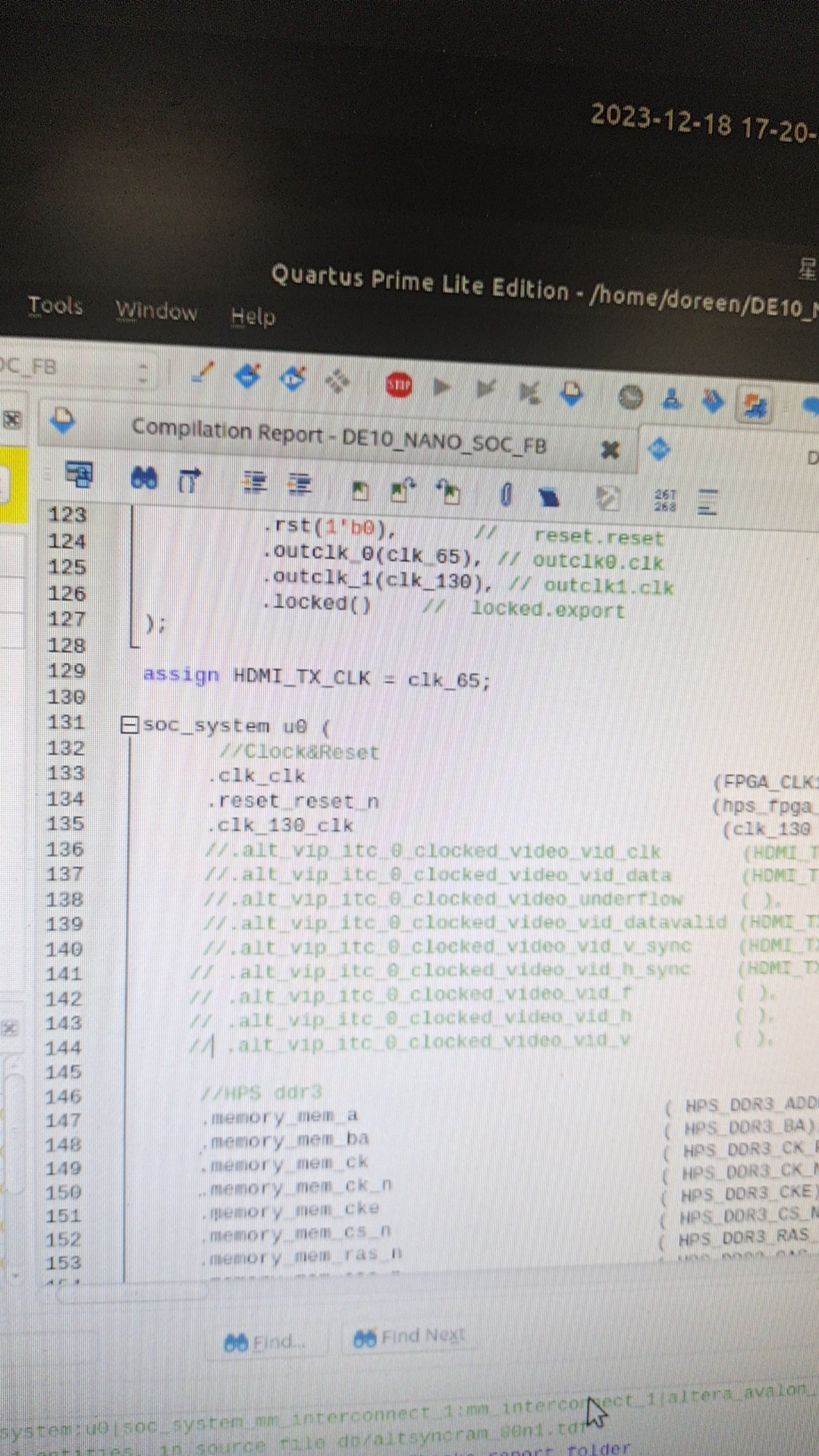

如果没有生成,您可以先在Qsys 中把这两个器件disable 掉, 然后top文件里面把相关的信号也注释掉, 然后重新生成soc_system.sopcinfo

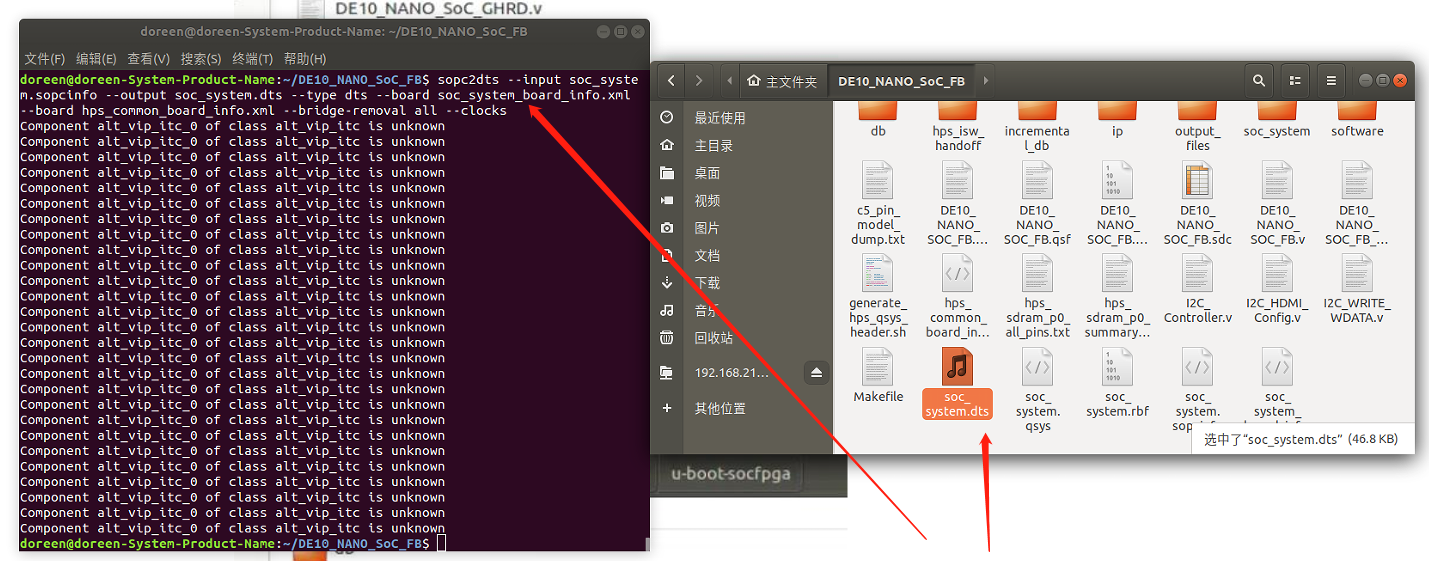

sopc2dts --input soc_system.sopcinfo --output soc_system.dts --type dts --board soc_system_board_info.xml --board hps_common_board_info.xml --bridge-removal all --clocks生成dts文件后,再在qsys里面 eable这两个ip核。

这样操作以后,dts文件里面是不会有这两个ip核的描述。实际 上,这两个IP 是不需要在.dts 中描述的。

额外说明:

当 Qsys 产生出 FPGA 的设计后(.sopcinfo),可以使用 Altera SoC EDS 工具里的 Device Tree Generator 来产生 Device Tree 的源文档(dts)。它描述了有关 HPS 的外设还有选择使用到的 FPGA Soft IP 以及用户自定义的外设等信息。.dtb 文件是.dts 文件被 Device Tree Compiler 编译后生成的二进制格式的 Device Tree描述,可被 Linux 内核解析。通常在我们为开发板制作 NAND、Sdcard 启动 image 时,会为.dtb 文件预留一个很小的存放区域(FAT 分区)。之后 bootloader 在引导 kernel的过程中,会先读取该.dtb 到内存。

无