一、VGA显示原理及VGA驱动模块

请参考这篇文章:

基于权电阻网络的VGA彩条显示(DE0-CV、DE10-Lite)

二、AVD7123芯片的控制

请参考这篇文章:

基于FPGA和ADV7123的VGA彩条显示(DE10-Standard、DE1-SOC、DE2-115)

读完这两篇文章,大家对VGA显示原理和ADV7123的控制就会有所了解,再移植到贪吃蛇游戏里面实现色块显示就非常简单了。

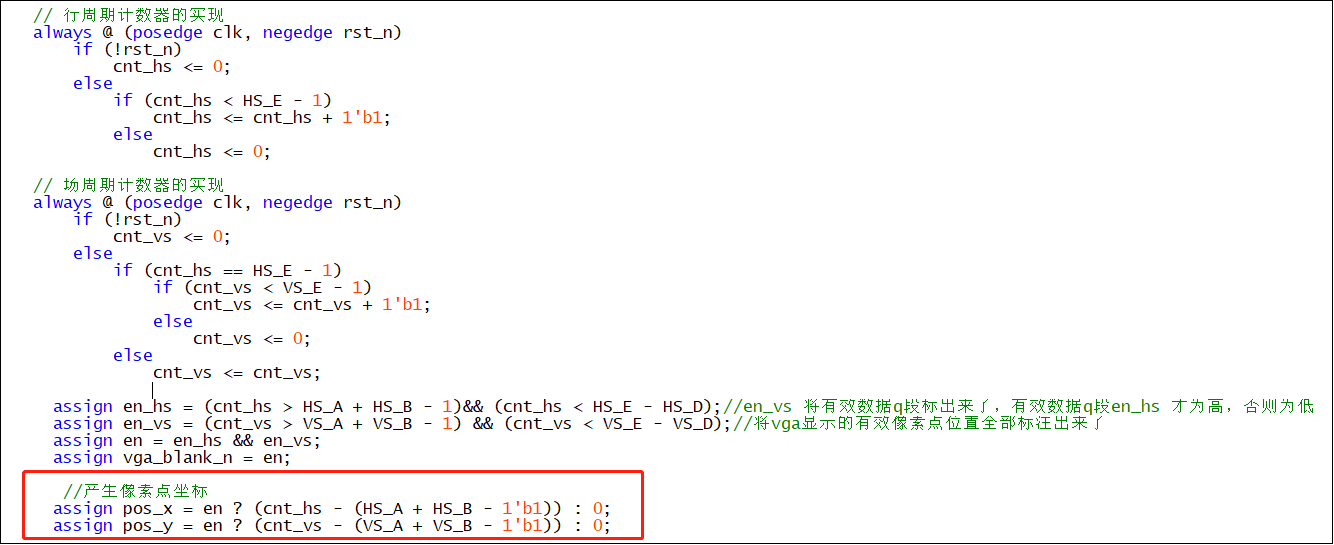

三、VGA像素坐标的产生

四、VGA显示器显示分数(显示色块)

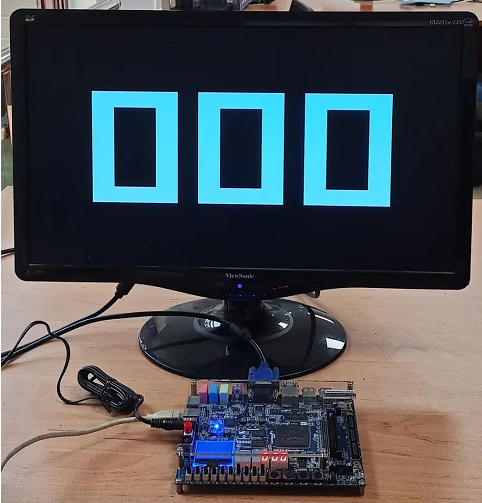

在贪吃蛇游戏结束的时候,VGA显示器会显示当前累计的分数。如下图所示:

这个是怎么实现的呢?

其实就是将VGA显示器划分成几个区域,然后对某些区域输出对应的颜色,比如显示000:

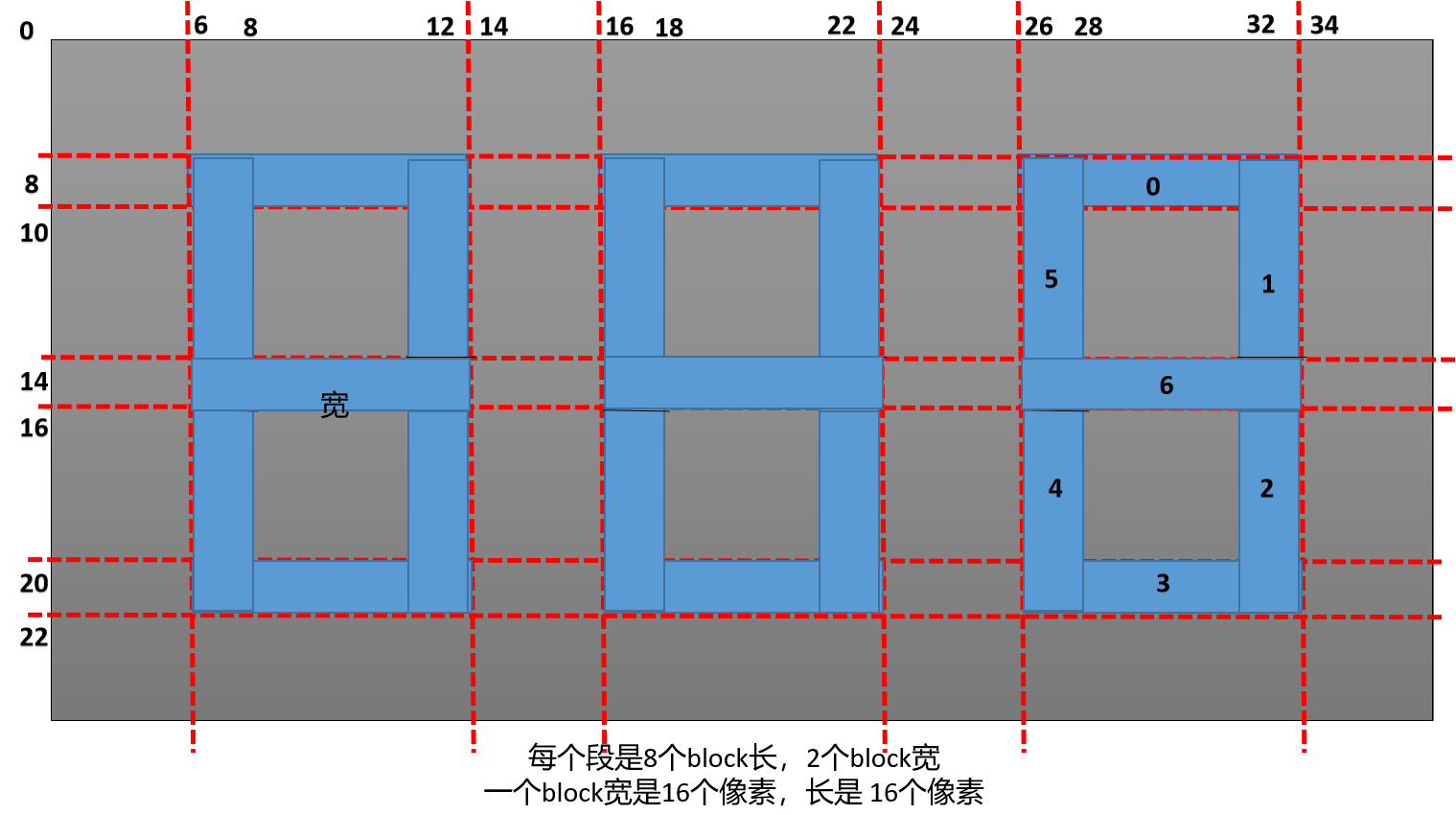

假设在VGA显示器上做出数码管显示的效果,三个数码管,每个数码管7段,每个段是8个block长,2个block宽 。一个block宽是16个像素,长是 16个像素。

所以我们这样划分以后,代码这样对应(下面是右边第一个数显示0的代码,也就是分数的个位数。其他以此类推。):

case (bcd_data[3:0]) //个位数 4'd0:begin //显示0 if(pos_x[9:4] >= 26 && pos_x[9:4] < 34 && pos_y[9:4] >= 8 && pos_y[9:4] < 10) vga_rgb = 24'h80ffff;//第0段输出蓝色 else if(pos_x[9:4] >= 26 && pos_x[9:4] < 34 && pos_y[9:4] >= 20 && pos_y[9:4] < 22) vga_rgb = 24'h80ffff;//第3段输出蓝色 else if(pos_x[9:4] >= 26 && pos_x[9:4] < 28 && pos_y[9:4] >= 8 && pos_y[9:4] < 16) vga_rgb = 24'h80ffff;//第5段输出蓝色 else if(pos_x[9:4] >= 32 && pos_x[9:4] < 34 && pos_y[9:4] >= 8 && pos_y[9:4] < 16) vga_rgb = 24'h80ffff;//第1段输出蓝色 else if(pos_x[9:4] >= 26 && pos_x[9:4] < 28 && pos_y[9:4] >= 14 && pos_y[9:4] < 22) vga_rgb = 24'h80ffff;//第4段输出蓝色 else if(pos_x[9:4] >= 32 && pos_x[9:4] < 34 && pos_y[9:4] >= 14 && pos_y[9:4] < 22) vga_rgb = 24'h80ffff;//第2段输出蓝色 else vga_rgb = 24'h000000;//否则输出黑色 end

(pos_x,pos_y)是像素坐标,这里代码在判断的时候只取pos_y[9:4],为什么呢?

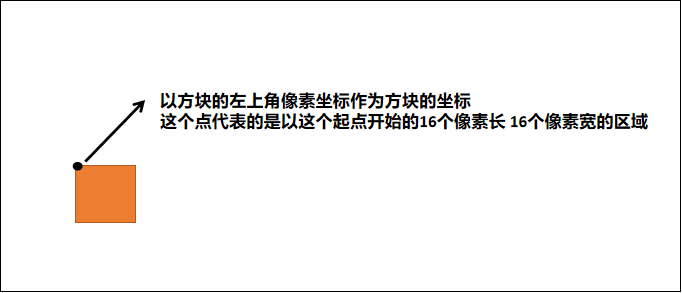

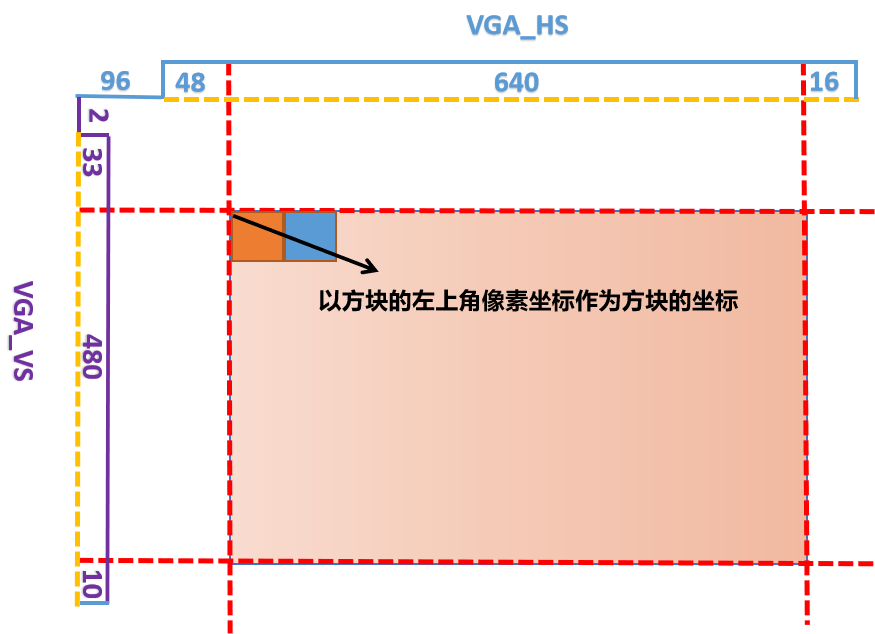

每个方块16*16(256)个像素,以方块的左上角像素坐标作为方块的坐标 :

每个方块的像素坐标pos_x[3:0]和pos_y[3:0]都为0,所以代码里面只需要看pos_x[9:4]和pos_y[9:4]。

比如第一个橙色方块的坐标pos_x[9:4]和pos_y[9:4]是[0,0], 第二个蓝色方块的坐标是[1,0],其他以此类推:

贪吃蛇系列链接:

友晶科技FPGA开发板实现贪吃蛇游戏(九)——蛇身控制 DE10-STANDARD、DE1-SOC、DE2-115 - Doreen的FPGA自留地 - 博客园 (cnblogs.com)

友晶科技FPGA开发板实现贪吃蛇游戏(八)——游戏控制之状态机设计 DE10-STANDARD、DE1-SOC、DE2-115 - Doreen的FPGA自留地 - 博客园 (cnblogs.com)

友晶科技FPGA开发板实现贪吃蛇游戏(七)食物(苹果)的产生 DE10-STANDARD、DE1-SOC、DE2-115 - Doreen的FPGA自留地 - 博客园 (cnblogs.com)

友晶科技FPGA开发板实现贪吃蛇游戏(六)VGA 驱动模块图片显示 DE10-STANDARD、DE1-SOC、DE2-115 - Doreen的FPGA自留地 - 博客园 (cnblogs.com)

友晶科技FPGA开发板实现贪吃蛇游戏(五)VGA 驱动模块字符显示 DE10-STANDARD、DE1-SOC、DE2-115 - Doreen的FPGA自留地 - 博客园 (cnblogs.com)

友晶科技FPGA开发板实现贪吃蛇游戏(四)VGA 驱动模块色块显示 DE10-STANDARD、DE1-SOC、DE2-115 - Doreen的FPGA自留地 - 博客园 (cnblogs.com)

友晶科技FPGA开发板实现贪吃蛇游戏(三)记分模块 DE10-STANDARD、DE1-SOC、DE2-115 - Doreen的FPGA自留地 - 博客园 (cnblogs.com)

友晶科技FPGA开发板实现贪吃蛇游戏(二)数码管驱动模块 DE10-STANDARD、DE1-SOC、DE2-115 - Doreen的FPGA自留地 - 博客园 (cnblogs.com)

友晶科技FPGA开发板实现贪吃蛇游戏(一)——整体描述 DE10-Standard、DE1-SOC、DE2-115 - Doreen的FPGA自留地 - 博客园 (cnblogs.com)