Signal Tap 工具真的是一款非常非常实用的调试工具,它可以帮你定位到非常隐蔽的错误。

最近想显示VGA 三色彩条 (源码:基于友晶科技 FPGA开发板 DE2-115 和 DE10-STANDARD 的VGA彩条显示设计(ADV7123)),引 脚分配和控制信号的设计 都检查了 没有错误。也排除了VGA显示器故障(测试DE10-Standard\Demonstration\FPGA\DE10_Standard_Default有图片显示) , 但是VGA 就是没有信号输出。

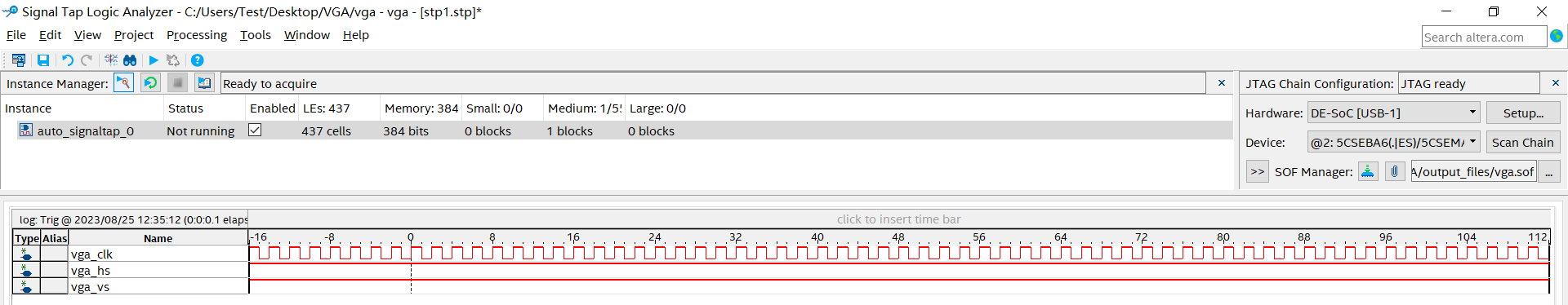

于是我用Signal Tap 工具看看vga_clk、 vga_hs 和 vga_vs 这些控制信号有没有信号先。

Signal Tap 的使用步骤请参考友晶科技官方论论坛【DE10-Nano系列教程】工具篇(四)--Signal Tap Logic Analyzer使用 ,这里有详细的步骤和讲解。

以下是我的操作:

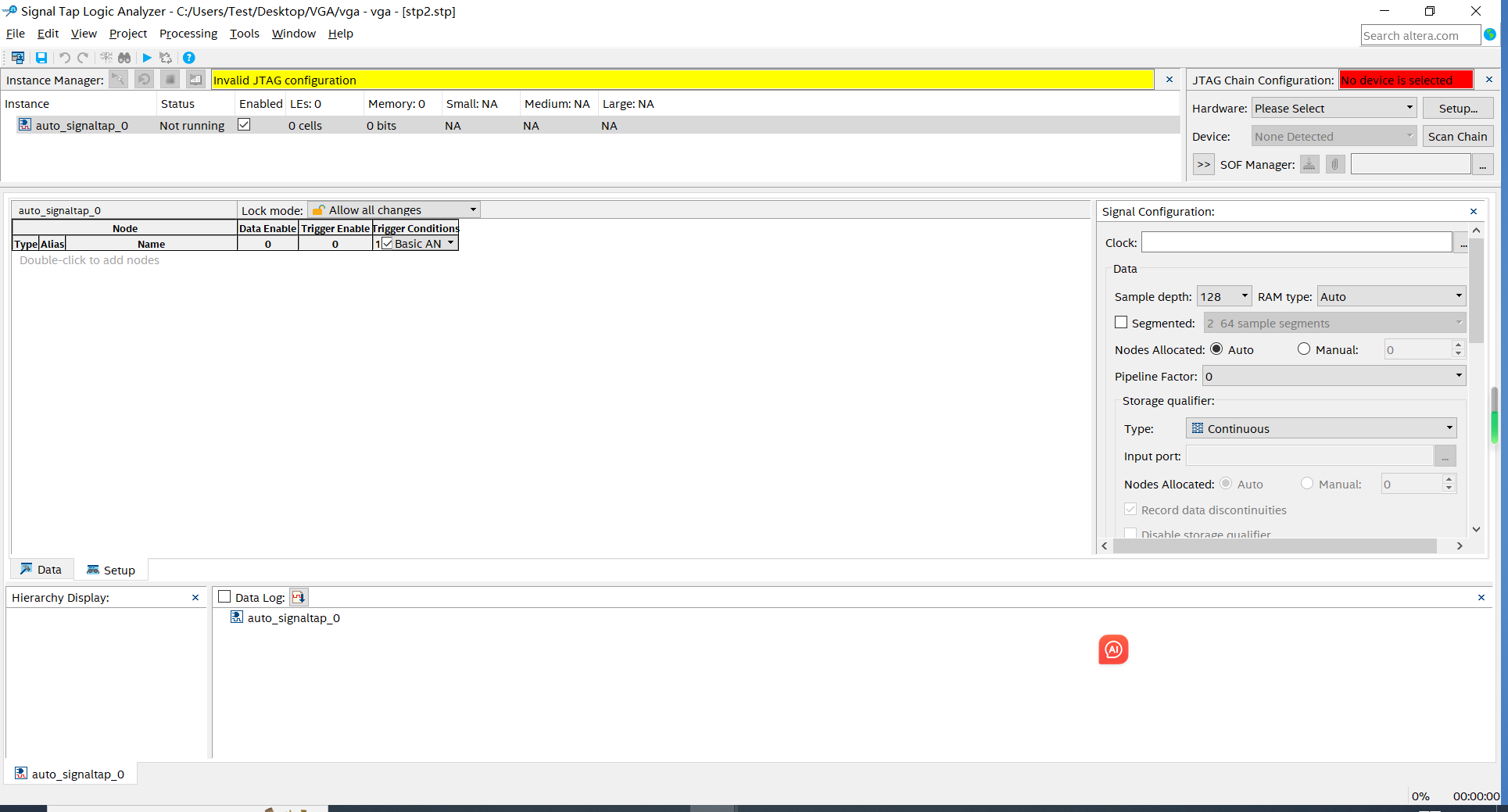

1. 点击File——New——Signal Tap Logic Analyzer File,然后点击OK:

弹出窗口:

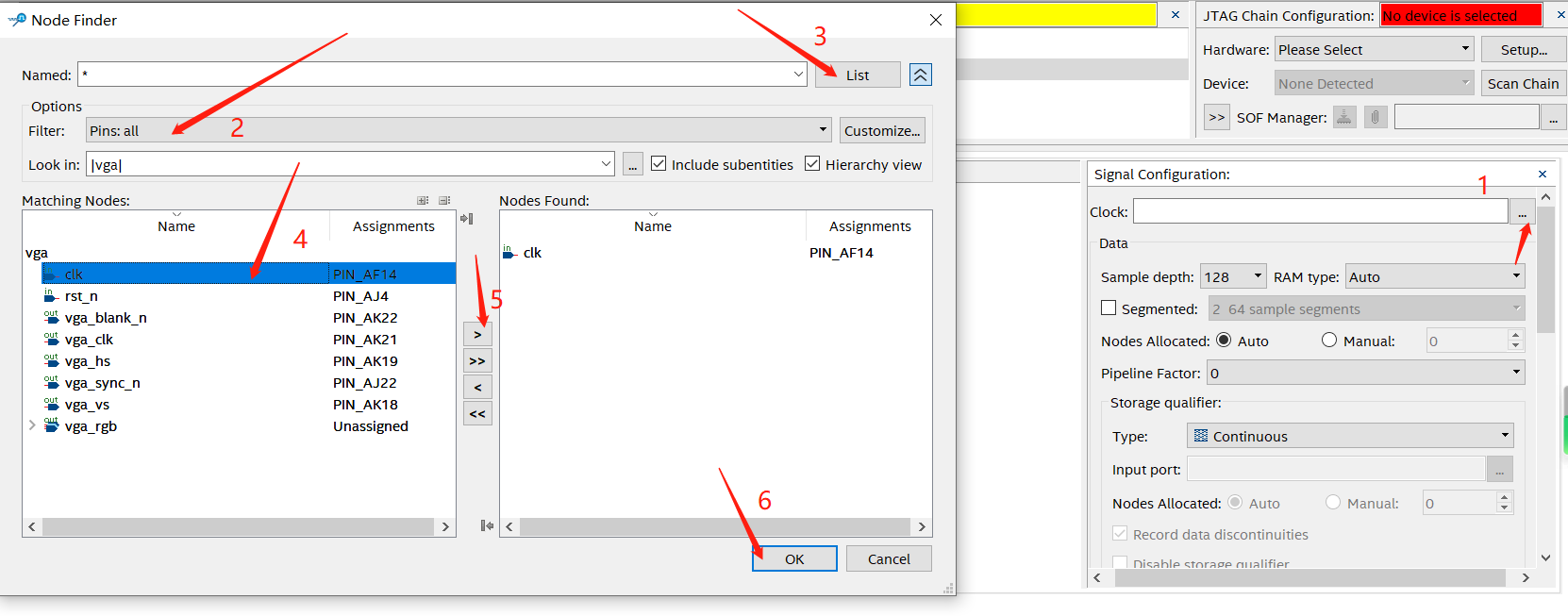

2. 选择采样时钟:点击右侧Clock栏的..., 在Filter处选择Pins:all ,然后点击List,然后选择clk ,然后点击> 然后点击OK:

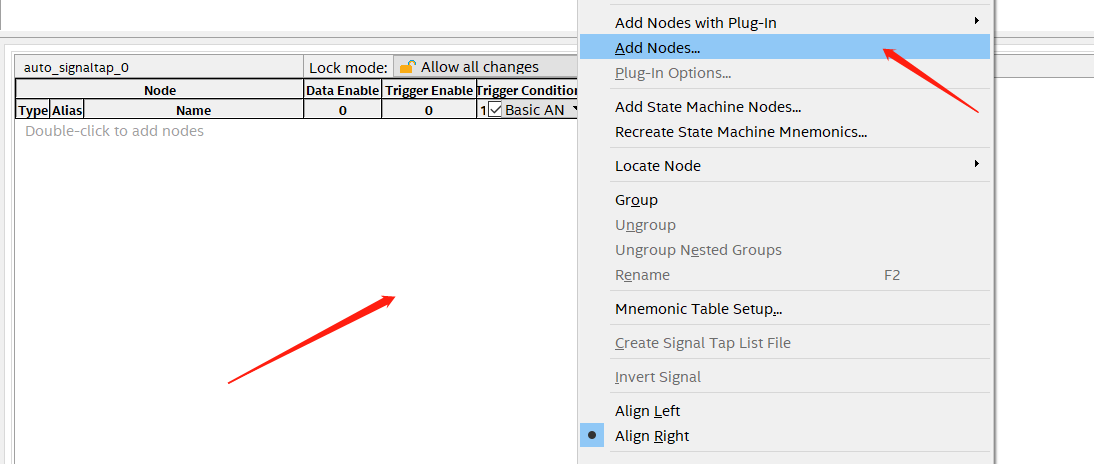

3. 然后在左边空白处右击选择Add Node:

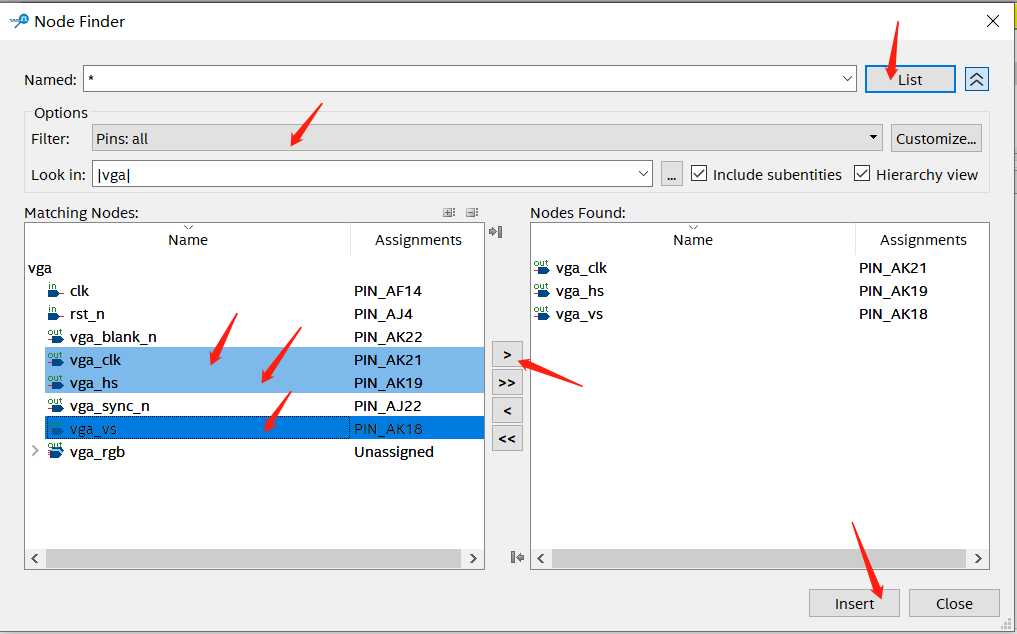

然后在Filter处选择Pins:all ,然后点击List,然后选择vga_clk信号 ,然后点击> , vga_hs vga_vs2个信号也这样加到右边。 然后点击Insert和Close:

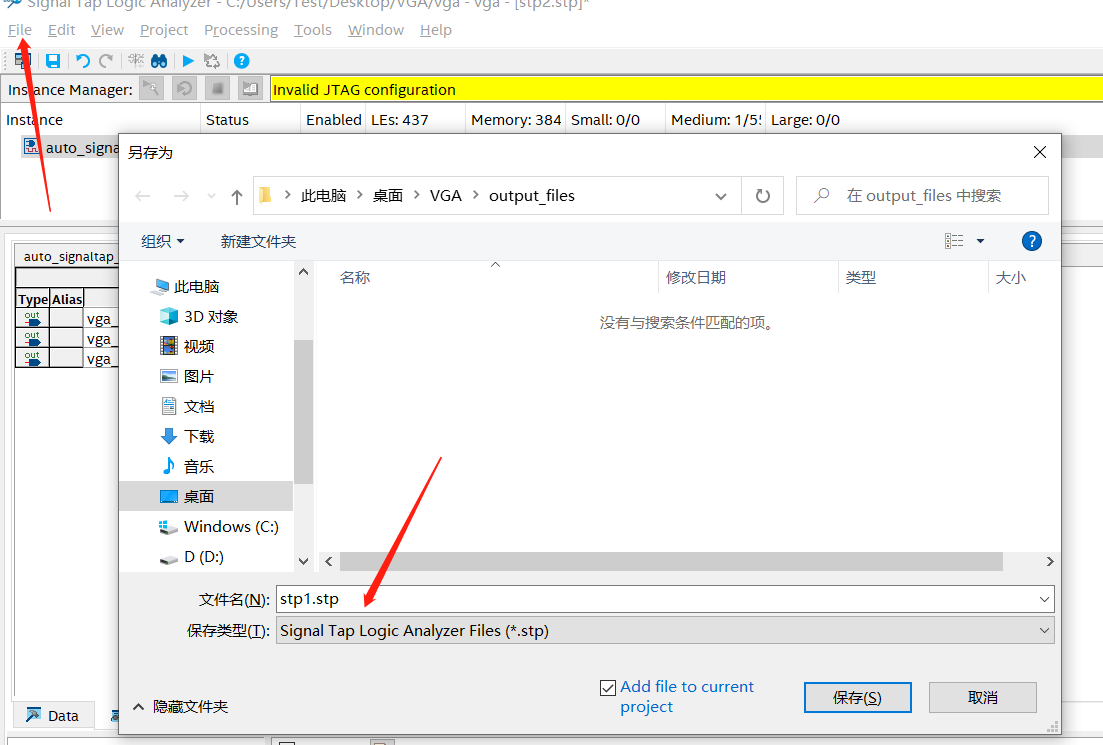

然后保存:

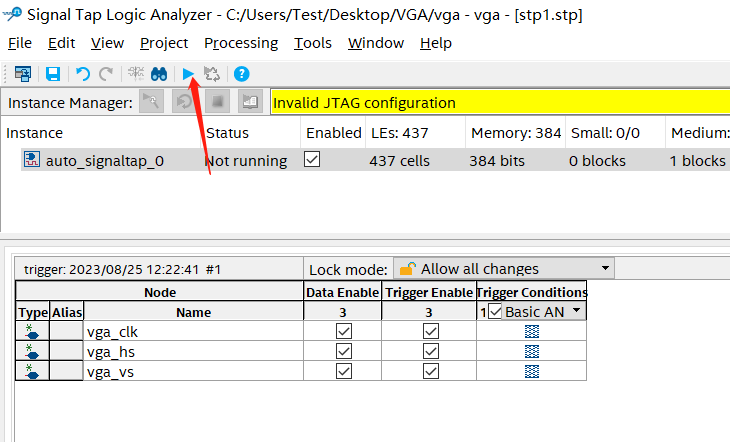

然后点击三角形重新编译:

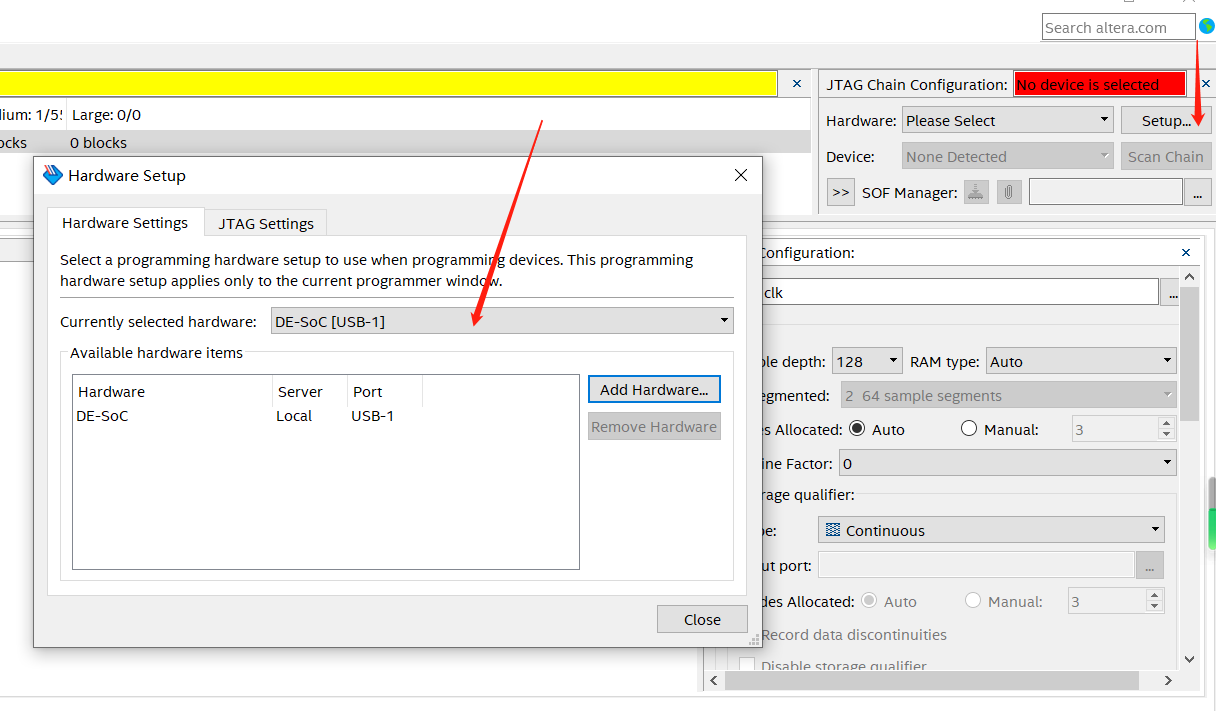

然后连接硬件,找到硬件端口:

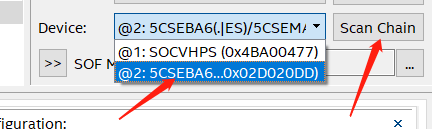

点击Scan Chain , 选择下面的@2 5CSEBA6...0X02D020DD):

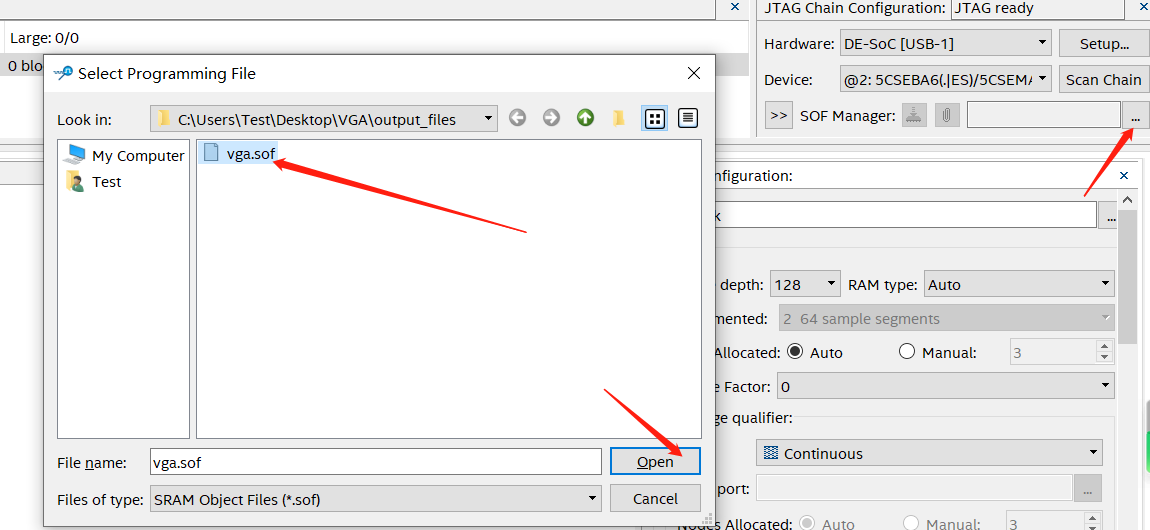

然后选择sof文件:

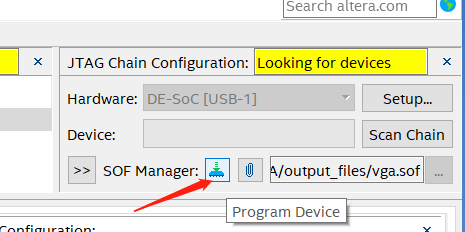

点击下载:

运行:

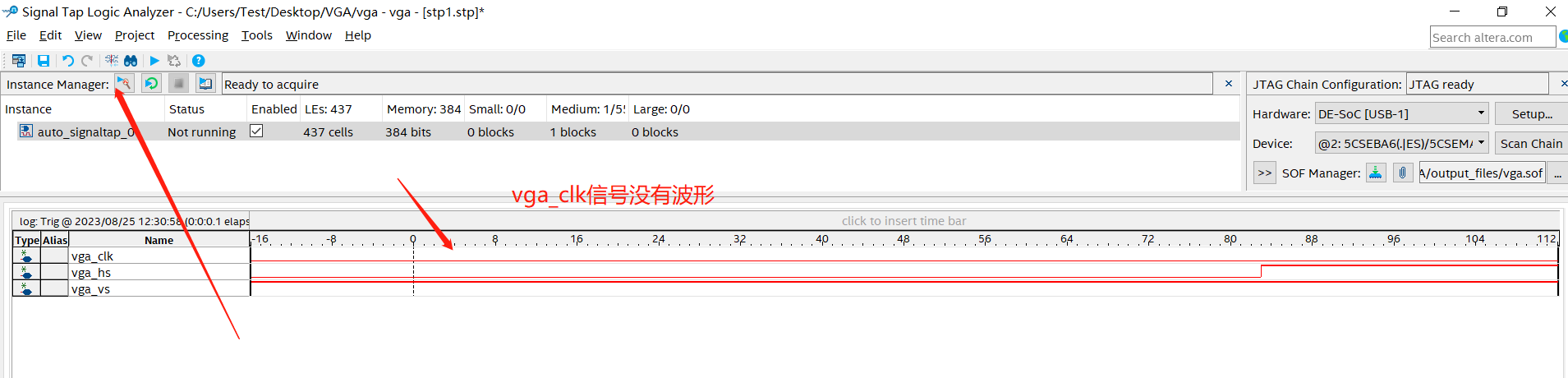

看来是vga_clk 这个信号没有输出呢!

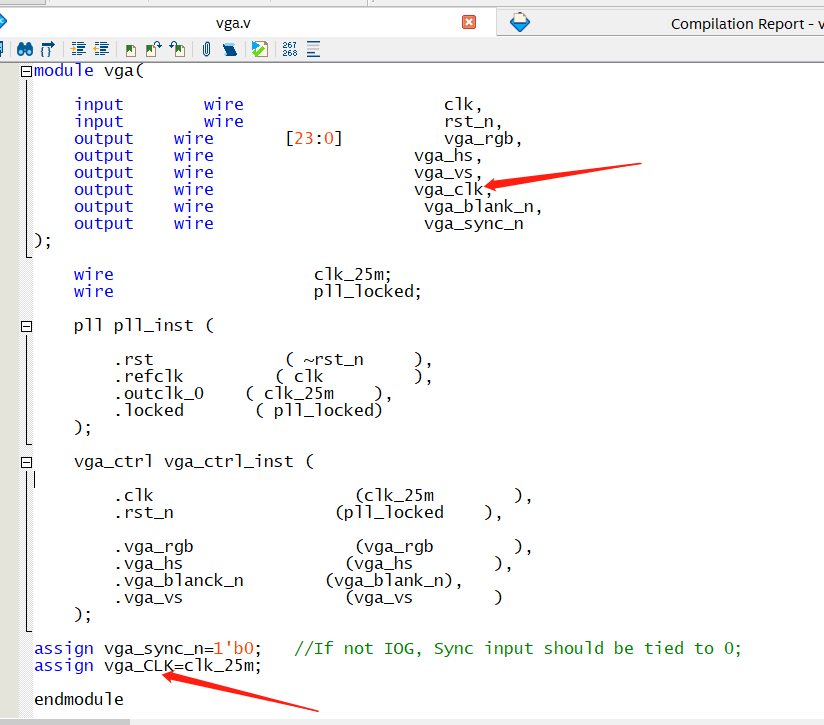

返回TOP文件代码查看发现原来大小写搞错了(但奇怪的是Quartus 编译的时候却不报错!):

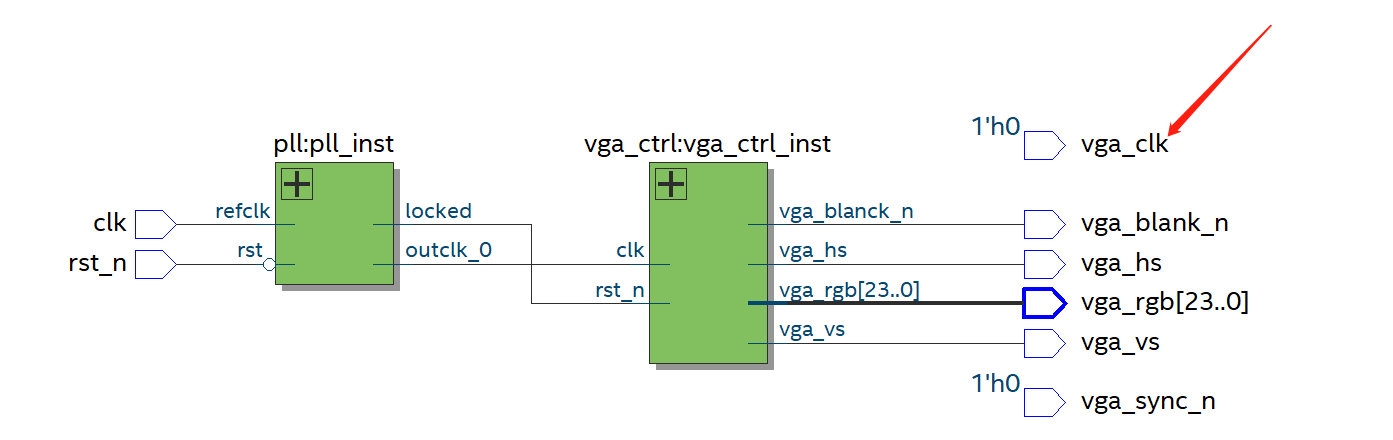

再打开RTL View图,发现vga_clk信号确实没有接什么来源:

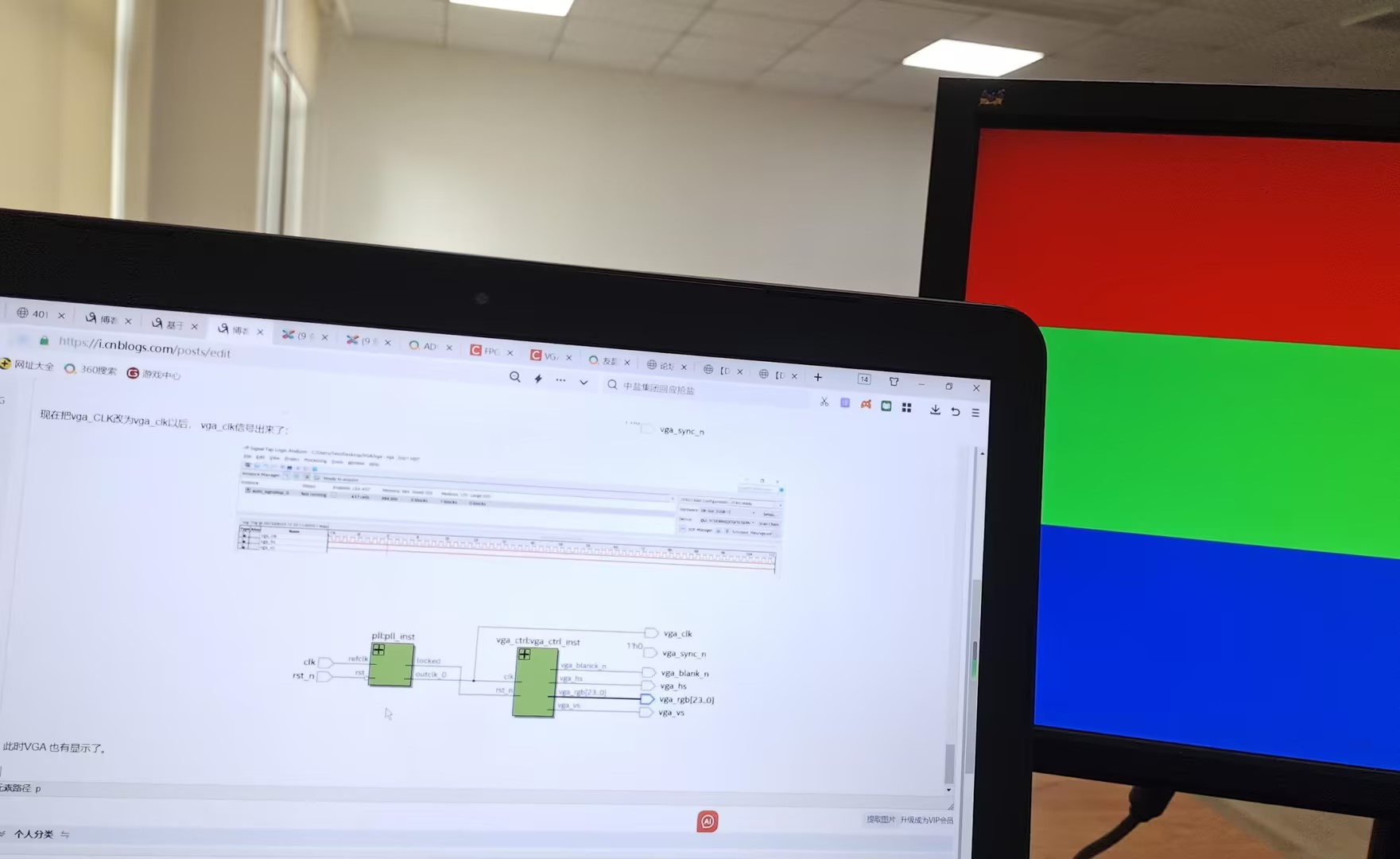

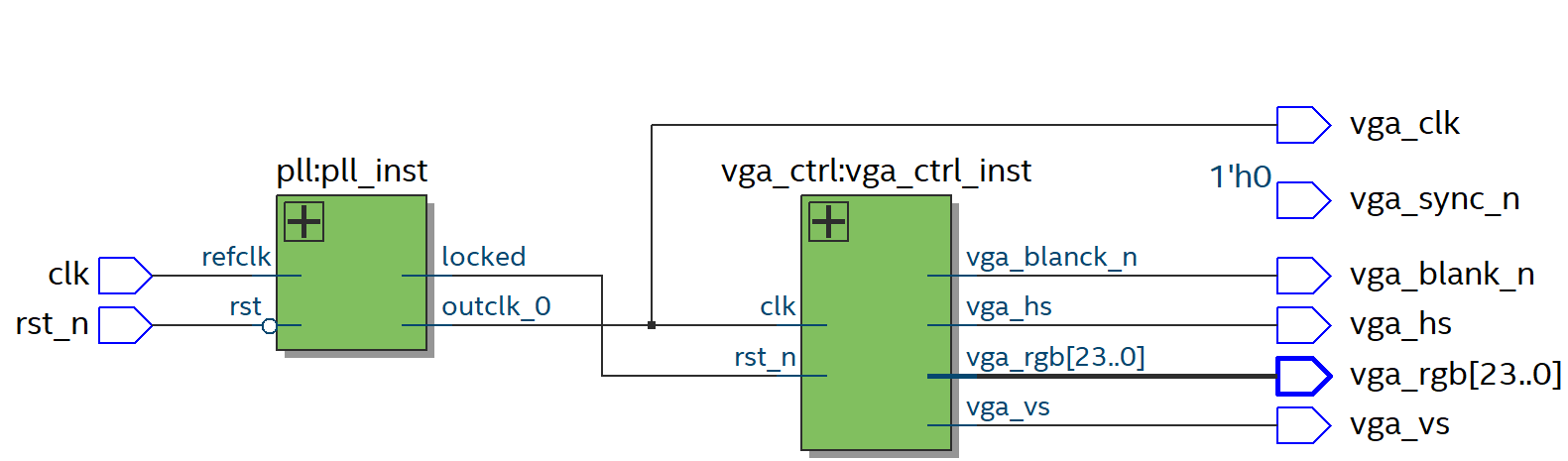

现在把vga_CLK改为vga_clk以后, vga_clk信号出来了:

此时VGA 也有显示了。