TMDS(Transition Minimized Differential Signaling) 最小化传输差分信号。

TMDS由Silicon Image公司开发的一项高速数据传输技术,采用的是差分传动方式。这不仅是DVI技术的基础,也是HDMI技术的基础原理。

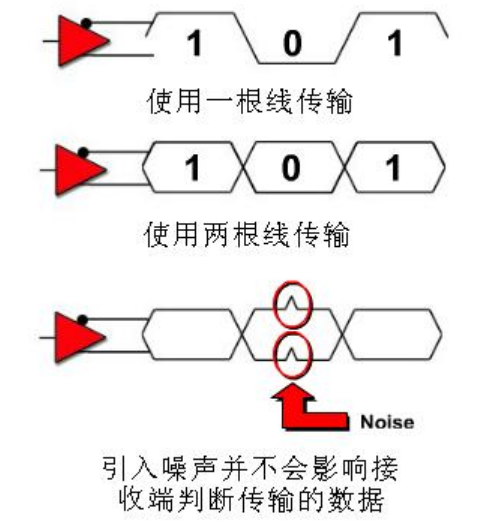

TMDS差分传动技术是一种利用2个引脚间电压差来传送信号的技术。传输数据的数值("0"或者"1")由两脚间电压正负极性和大小决定。即,采用2根线来传输信号,一根线上传输原来的信号,另一根线上传输与原来信号相反的信号。这样接收端就可以通过让一根线上的信号减去另一根线上的信号的方式来屏蔽电磁干扰,从而得到正确的信号。

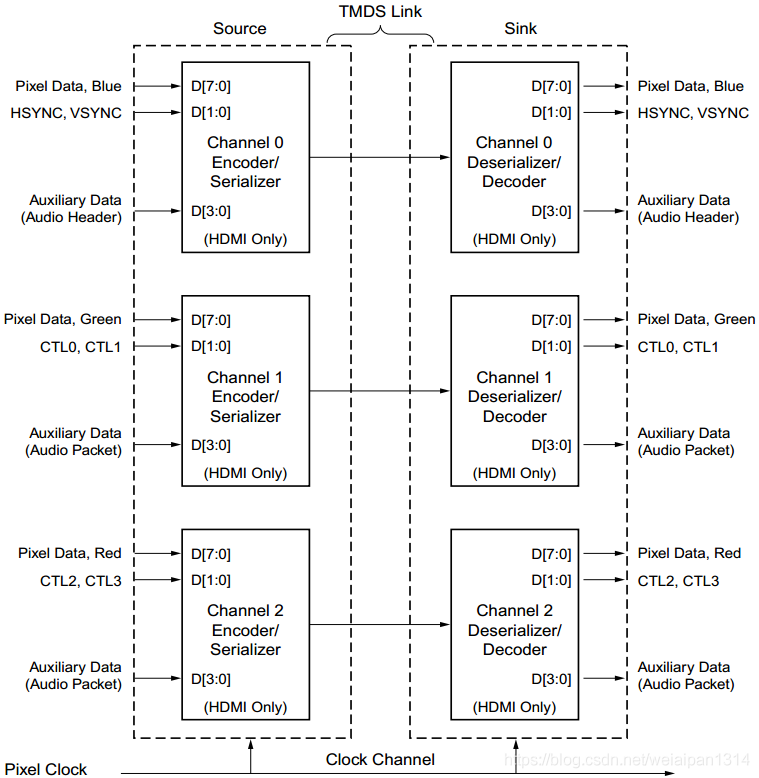

每一个标准的HDMI连接,都包含了3个用于传输数据的TMDS传输通道,还有1个独立的TMDS时钟通道,以保证传输时所需的统一时序。

在一个时钟周期内,每个TMDS通道都能传送10bit的数据流。而这10bit数据,可以由若干种不同的编码格式构成。

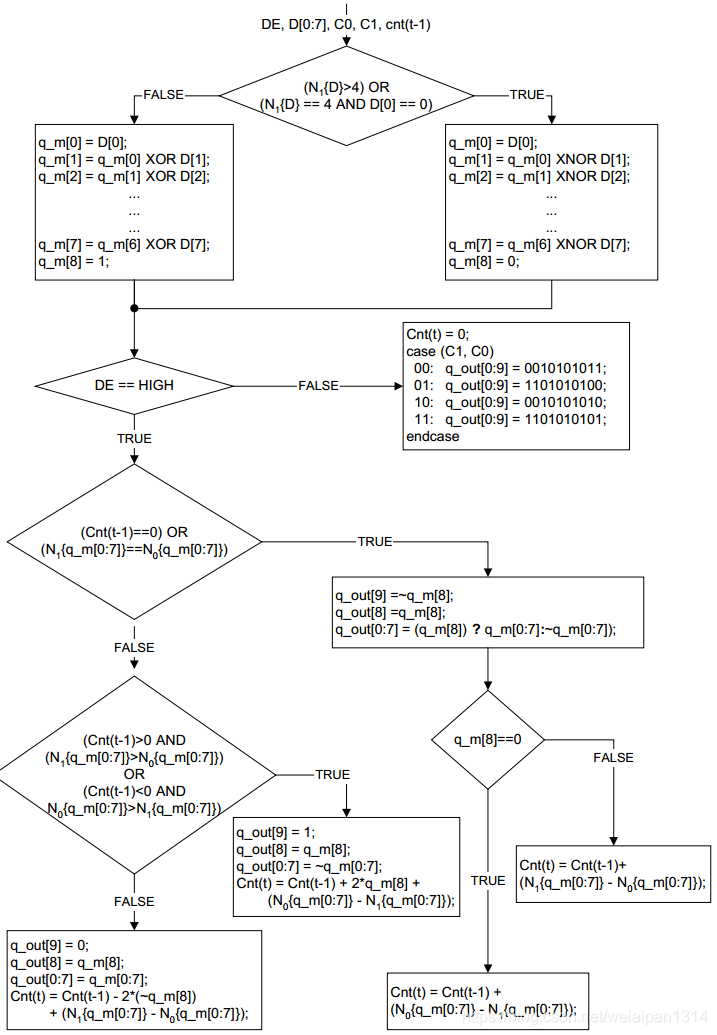

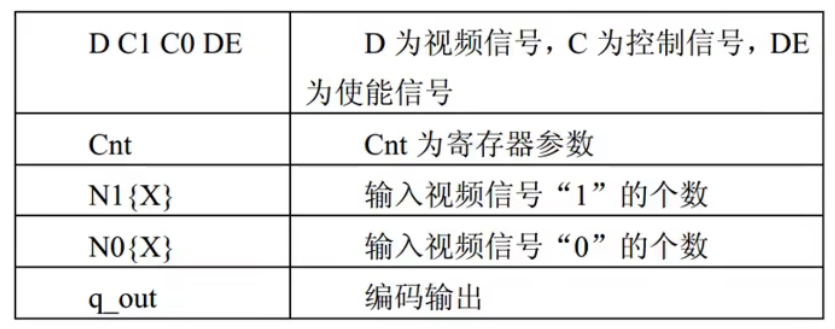

每个数据通道都通过编码算法(异或、异或非等),将8位数据转换成10位数据,前8为数据由原始信号经运算后获得,第9位指示运算的方式,第10位用来对应直流平衡。通过这种算法,会使得数据的传输和恢复更加可靠。

1.减少上信号上冲和下冲

第一步:将8位并行RED数据发送到TMDS Tx。

第二步:进行最小化传输处理,加上第9位,即编码过程。第9位数据称为编码位。(第9 bit = 0, 异或非, 第9 bit = 1, 异或 )

2.直流平衡(DC-balanced)

直流平衡:在编码过程中,保证信道的直流偏移为零。方法是在原来的第9位数据后面加上1位,使得TMDS发送的"0"、"1"数量保持基本一致。这样,传输的数据趋于直流平衡,使信号对传输线的电磁干扰减少,提高信号传输的可靠性。

3.串行 差分信号

将并行信号转化为串行信号,利用两引脚间电压差来传送信号。

TMDS 框图:

TMDS代码:

module Encoder( input i_pixel_clk , //像素时钟 input i_rst , //复位信号,高有效 input [07:00] i_data , //输入8位数据 input i_de , //像素数据有效信号 input i_ctrl_1 , //控制信号1 input i_ctrl_2 , //控制信号2 output reg [09:00] o_data //输出10位数 ); //计算数据中1的个数 reg [02:00] num_1_data; //1的个数 reg [07:00] data_temp1; always@(posedge i_pixel_clk) begin num_1_data <= i_data[7] + i_data[6] + i_data[5] + i_data[4] + i_data[3] + i_data[2] + i_data[1] + i_data[0]; data_temp1 <= i_data; end //判断条件1 8bit转变成9bit,减少跳变沿 wire decision1; wire [08:00] q_m; assign decision1 = (num_1_data > 3'd4) | ((num_1_data == 3'd4) & (data_temp1[0] == 0)); assign q_m[0] = data_temp1 [0]; assign q_m[1] = decision1 ? (q_m[0] ^ (~ data_temp1 [1])) : (q_m[0] ^ data_temp1[1]); assign q_m[2] = decision1 ? (q_m[1] ^ (~ data_temp1 [2])) : (q_m[1] ^ data_temp1[2]); assign q_m[3] = decision1 ? (q_m[2] ^ (~ data_temp1 [3])) : (q_m[2] ^ data_temp1[3]); assign q_m[4] = decision1 ? (q_m[3] ^ (~ data_temp1 [4])) : (q_m[3] ^ data_temp1[4]); assign q_m[5] = decision1 ? (q_m[4] ^ (~ data_temp1 [5])) : (q_m[4] ^ data_temp1[5]); assign q_m[6] = decision1 ? (q_m[5] ^ (~ data_temp1 [6])) : (q_m[5] ^ data_temp1[6]); assign q_m[7] = decision1 ? (q_m[6] ^ (~ data_temp1 [7])) : (q_m[6] ^ data_temp1[7]); assign q_m[8] = decision1 ? 1'b0 : 1'b1; //计算q_m中1的个数和0的个数 reg [03:00] num_1_q_m; reg [03:00] num_0_q_m; always@(posedge i_pixel_clk) begin num_1_q_m <= q_m[7] + q_m[6] + q_m[5] + q_m[4] + q_m[3] + q_m[2] + q_m[1] + q_m[0]; num_0_q_m <= 4'd8 - (q_m[7] + q_m[6] + q_m[5] + q_m[4] + q_m[3] + q_m[2] + q_m[1] + q_m[0]); end parameter CTRLTOKEN0 = 10'b11_0101_0100; parameter CTRLTOKEN1 = 10'b00_1010_1011; parameter CTRLTOKEN2 = 10'b01_0101_0100; parameter CTRLTOKEN3 = 10'b10_1010_1011; reg de_temp1; reg de_temp2; reg ctrl_1_temp1; reg ctrl_1_temp2; reg ctrl_2_temp1; reg ctrl_2_temp2; reg [08:00] q_m_temp; //流水线时钟对齐,i_data已延迟一个时钟,其余延迟两个时钟后输出 always@(posedge i_pixel_clk) begin de_temp1 <= i_de; de_temp2 <= de_temp1; ctrl_1_temp1 <= i_ctrl_1; ctrl_1_temp2 <= ctrl_1_temp1; ctrl_2_temp1 <= i_ctrl_2; ctrl_2_temp2 <= ctrl_2_temp1; q_m_temp <= q_m; end // 1、cnt=0时表示上次传输无数据流极性差异 // 2、cnt>0,即cnt[4]=0表示上次数据流中传输了更多的1 // 3、cnt<0,即cnt[4]=1表示上次数据流中传输了更多的0 wire decision2; wire decision3; reg [04:00] cnt; // cnt=0时表示上次传输无数据流极性差异 assign decision2 = (cnt == 5'd0) | (num_1_q_m == num_0_q_m); assign decision3 = ((~cnt[4]) & (num_1_q_m > num_0_q_m)) | (cnt[4] & (num_1_q_m < num_0_q_m)); always@(posedge i_pixel_clk or posedge i_rst) begin if(i_rst) begin o_data <= 10'd0; cnt <= 5'd0; end else begin if(de_temp2) begin if(decision2) begin o_data[9] <= ~q_m_temp[8]; o_data[8] <= q_m_temp[8]; o_data[07:00] <= q_m_temp[8] ? q_m_temp[07:00] : (~q_m_temp[07:00]); cnt <= q_m_temp[8] ? (cnt + num_1_q_m - num_0_q_m) : (cnt + num_0_q_m - num_1_q_m); end else begin if(decision3) begin o_data[9] <= 1'b1; o_data[8] <= q_m_temp[8]; o_data[07:00] <= ~q_m_temp[07:00]; cnt <= cnt + 2*q_m_temp[8] + num_0_q_m - num_1_q_m; end else begin o_data[9] <= 1'b0; o_data[8] <= q_m_temp[8]; o_data[07:00] <= q_m_temp[07:00]; cnt <= cnt - 2*(~q_m_temp[8]) + num_1_q_m - num_0_q_m; end end end else begin case({ctrl_2_temp2,ctrl_1_temp2}) 2'b00 : o_data <= CTRLTOKEN0; 2'b01 : o_data <= CTRLTOKEN1; 2'b10 : o_data <= CTRLTOKEN2; 2'b11 : o_data <= CTRLTOKEN3; endcase cnt <= 5'd0; end end end endmodule

相关阅读:

友晶科技FPGA开发板DE10-Nano的HDMI彩条实验(一)——HDMI简介

友晶科技FPGA开发板DE10-Nano的HDMI彩条实验(三)——DE10-Nano 的HDMI电路简介

友晶科技FPGA开发板DE10-Nano的HDMI彩条实验(四)——实验源码及现象演示

ADV7513芯片控制解读(中文版)——基于DE10-NANO开发板——C5G 开发板

浙公网安备 33010602011771号

浙公网安备 33010602011771号