有个学生曾经问 qsys 的第一个CLK IP 的 时钟源输入可否选择普通IO 作为输入?他想在普通IO 上接精度较高的10M晶振了。

答案是可以的。

但是他说遇到报错:Error (14566): The Fitter cannot place 1 periphery component(s) due to conflicts with existing constraints (1 fractional PLL(s)).

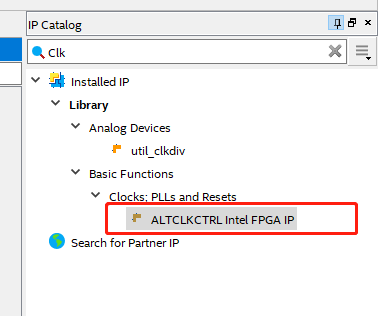

其实这是因为 普通IO 没有wire到 PLL,需要先用 CLKCTRL IP 将普通IO 连上 全局时钟等,然后再进PLL,这样就不会有这样的报错了。

无

浙公网安备 33010602011771号

浙公网安备 33010602011771号