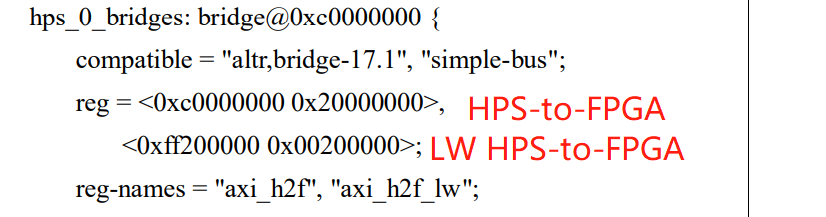

SOC FPGA是在单一器件上集成有双核 ARM Cortex-A9 的硬核处理器和FPGA逻辑资源, 硬核HPS这一端与FPGA 通信的时候采用的是AXI 的总线: HPS-to-FPGA 和LW HPS-to-FPGA。

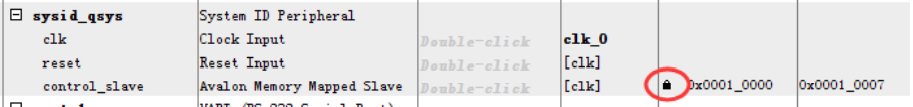

在设备树文件当中,systemid_qsys 这个组件的reg 有三个参数:

第二个地址参数是该组件在qsys里面定义的相对于总线LW HPS-to-FPGA的偏移, 第三个参数是基于该偏移地址映射虚拟地址时的范围。

那第一个参数是什么呢?

我们可以看到在设备树hps_0_bridges节点上的reg 给出了HPS-to-FPGA 和LW HPS-to-FPGA的基地址和映射范围。

hps_0_bridges作为父节点,这个节点里面还包括了PIO,systemid_qsys等组件。 因为systemid_qsys、PIO 等组件都是挂载在LW HPS-to-FPGA总线上的,systemid_qsys 这个组件的reg 的第一个参数0x00000001 代表选择父节点的第二个range也就是 LW_H2F,如果第一个参数是0x00000000 代表父节点第一个range也就是H2F。

无

浙公网安备 33010602011771号

浙公网安备 33010602011771号