RAM IP 核简介

RAM 是随机存取存储器(Random Access Memory),是一个易失性存储器,可随时对任何地址写入或者读出数据。

RAM IP核实现

RAM IP核实现使用的是FPGA 内部的 RAM资源:M9K、LCs......

单端口RAM

读和写使用同一个数据端口。

简单双端口RAM

两个数据端口,一个专门读,一个专门写。

真正双端口RAM

两个数据端口,两个端口都可以读和写。相当于两个单口RAM 的信号。

单口RAM IP调用和参数配置

1. 创建一个新Quartus工程。(步骤略)

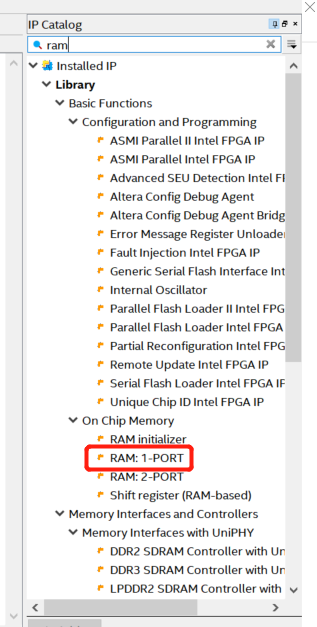

2.在IP Catalog 搜索ram:

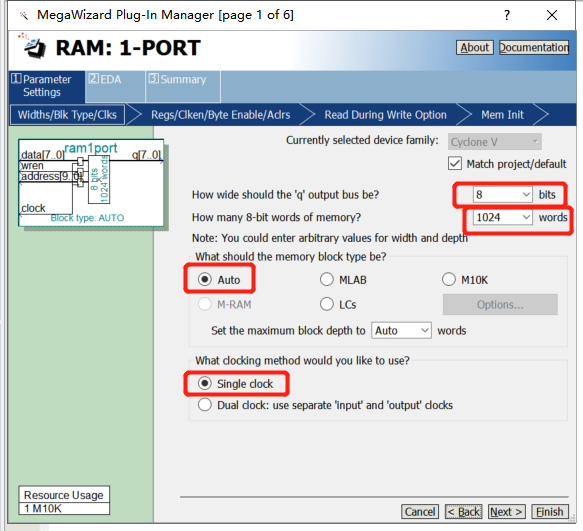

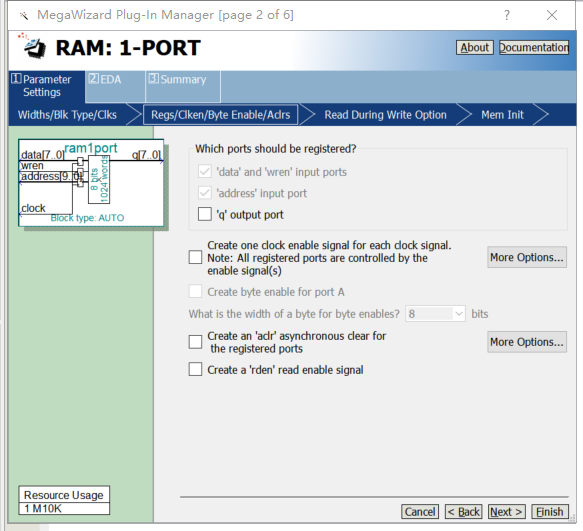

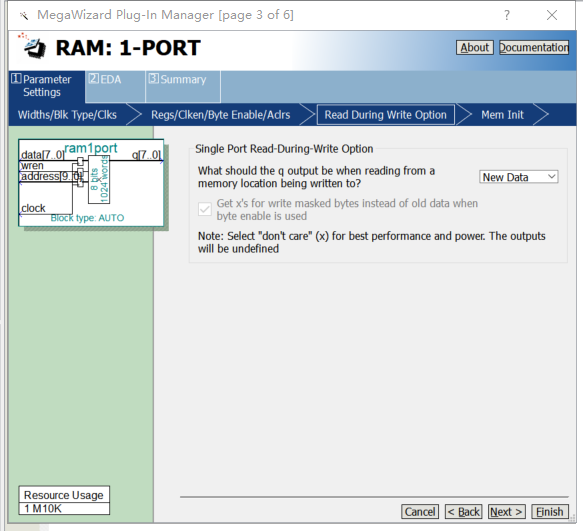

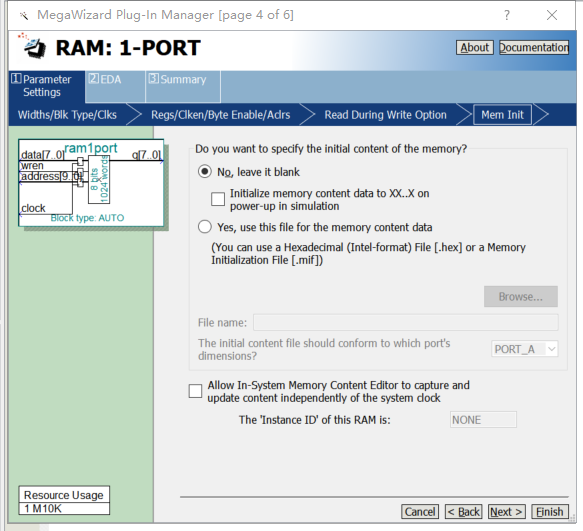

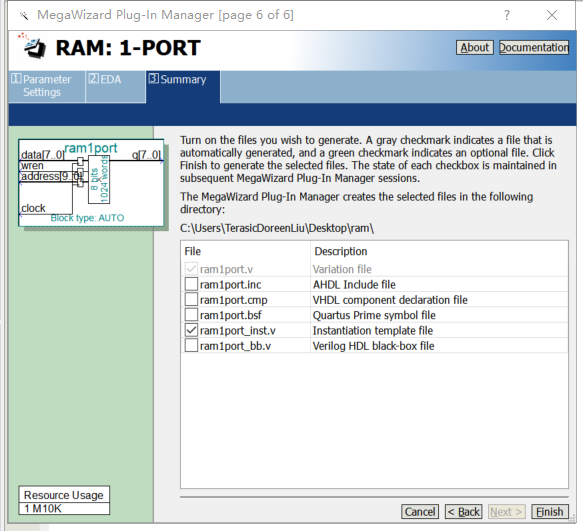

3.设置RAM IP的参数:

4. 点击finish,点击添加IP 到工程即可。

RAM IP 的顶层文件:

module ram( clk, rst_n, q ); input clk; input rst_n; output [7:0]q; wire [9:0]address; wire [7:0]data; wire wren; ram1port ram1port_inst ( .address ( address ), .clock ( clk ), .data ( data ), .wren ( wren ), .q ( q ) ); ram_control ram_control_inst( .clk(clk), .rst_n(rst_n), .address(address), .data(data), .wren(wren) ); endmodule

RAM IP 的控制:

module ram_control( clk, rst_n, address, data, wren ); input clk; input rst_n; output reg [7:0]address; output reg [7:0]data; output reg wren; reg state; always@(posedge clk or negedge rst_n) begin if(!rst_n) begin address<=0; data<=0; wren<=0; state<=0; end else begin case(state) 0:begin wren<=1; if(address<255) begin address<=address+1; data<=data+1; end else begin address<=0; data<=0; wren<=0; state<=1; end end 1:begin if(address<255) begin address<=address+1; end else begin address<=0; end end default:state<=0; endcase end end endmodule

无