关于 HPS IO 复用 细节请参考我之前的博客:

https://www.cnblogs.com/DoreenLiu/p/14012088.html

HPS端普通外设引脚分配(uart、spi、I2C、USB、GPIO、ethernet、SD card等)

当我直接在DE1-SOC 的 GHRD 工程里面为HPS端的串口分配管脚的时候,它提示:Editing location assignment is not successful. Not assignable.

原因是:HPS 端的UART 不能手动在pin planner里面分配, 因为硬件已经分配好了。 那它是在哪里分配的呢?

答案是:UART 的引脚资源使用(包括其他HPS 端的外设)直接在Qsys 中通过HPS IP 进行配置即可。 如下图所示设置UART的引脚:

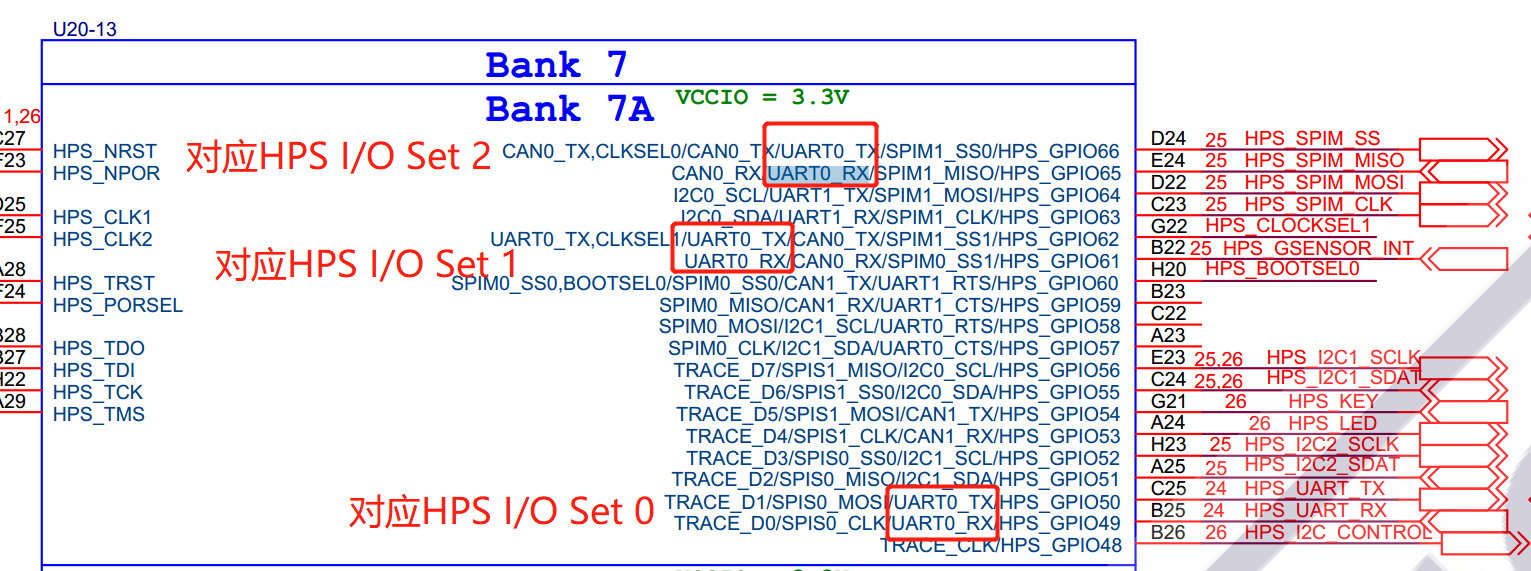

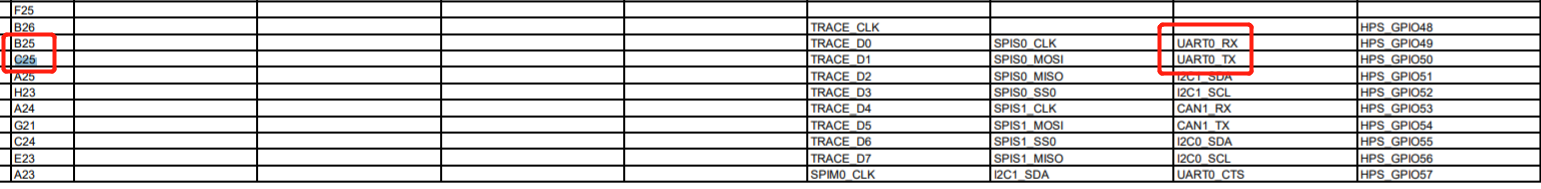

在HPS IP 里面,你想要你的 uart 外设 用HPS 的哪些引脚资源,就可以在HPS IP 里面对应的设置 HPS I/O Set0 还是 HPS I/O Set1 还是 HPS I/O Set2,这里的 HPS I/O Set0、 HPS I/O Set1、 HPS I/O Set2对应到电路里面其选择的引脚是:

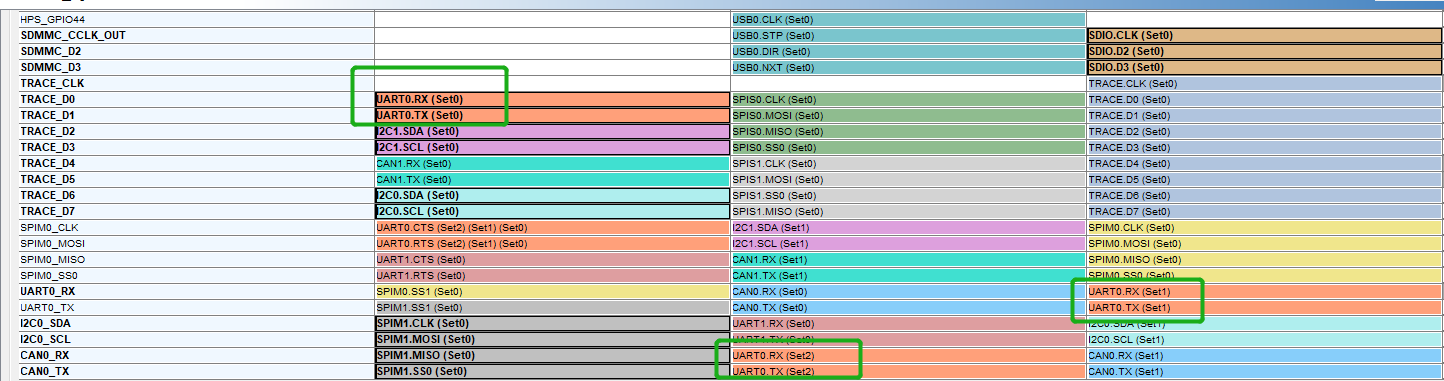

在HPS IP 设定页的最底层有个 Peripherals Mux Table 如下图所示,可以帮助用户检验整个 HPS 外设 I/O pin multiplexing 设定的状态,看看是否有所冲突。每个 mux_select 表内,若管脚名被标注为粗体,就代表此管脚功能已被设定。

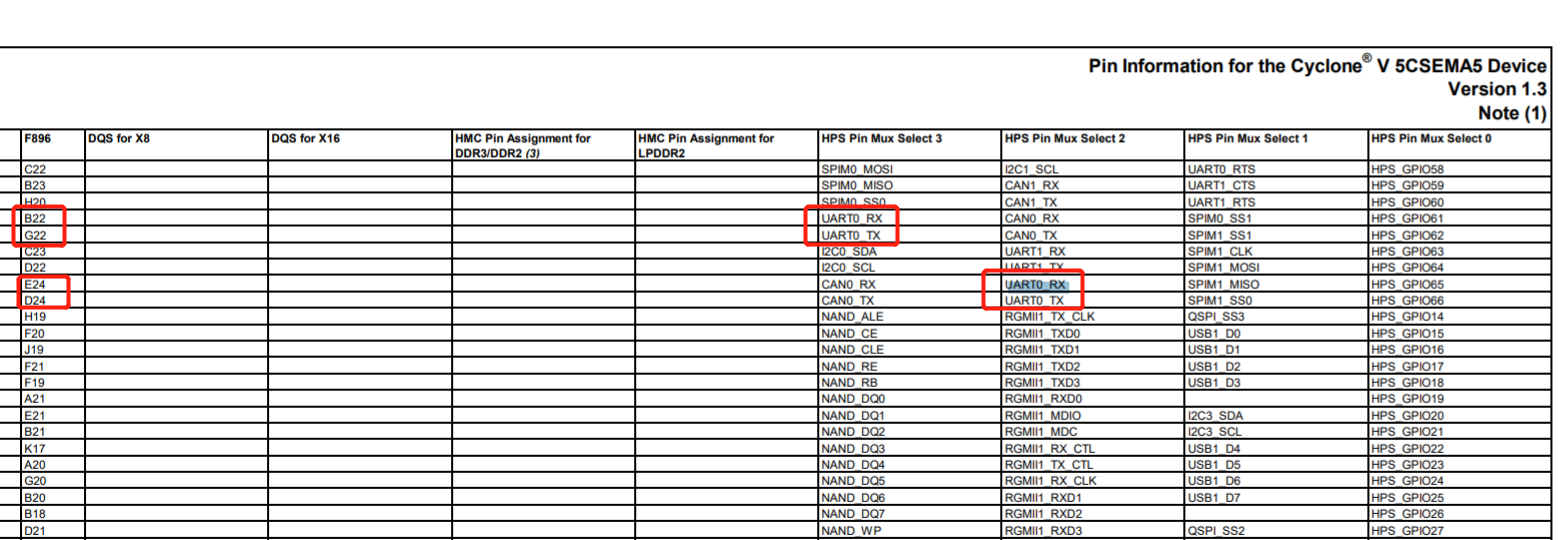

DE1-SOC 对应的 SOC FPGA 芯片 引脚信息还可以参考intel的这个文档(for 5CSEMA5 device)( [](https://www.intel.cn/content/dam/www/programmable/us/en/pdfs/literature/dp/cyclone-v/5csema5.pdf))如下:

DE1-SOC的 uart外设在板子硬件上固定到 C25引脚和B25引脚了,所以直接在HPS IP里面选择 HPS I/O Set0即 完成了 引脚分配(pin assignment)。

HPS 的 SDRAM 外设的引脚分配

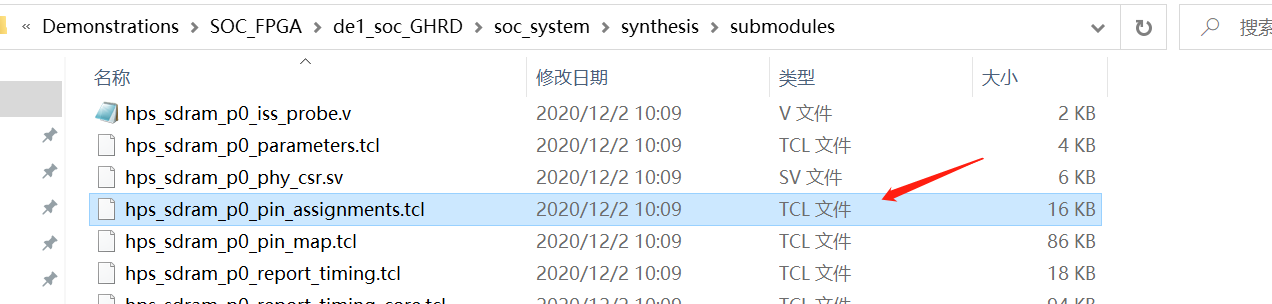

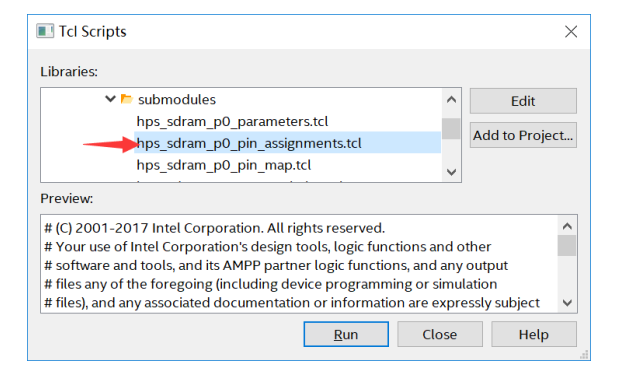

HPS 的 SDRAM 外设 则需要run Qsys自动生成的hps_sdram_p0_pin_assignments.tcl 文件:

无