刚接触SoC FPGA时,我对SoC FPGA的灵活性并没有领会多少,我只觉得它很复杂。为啥复杂?因为不懂嘛!查了好些资料,终于弄明白HPS IO复用的特性,也更加领会到SoC FPGA的灵活是说得一点都没错!

言归正传。

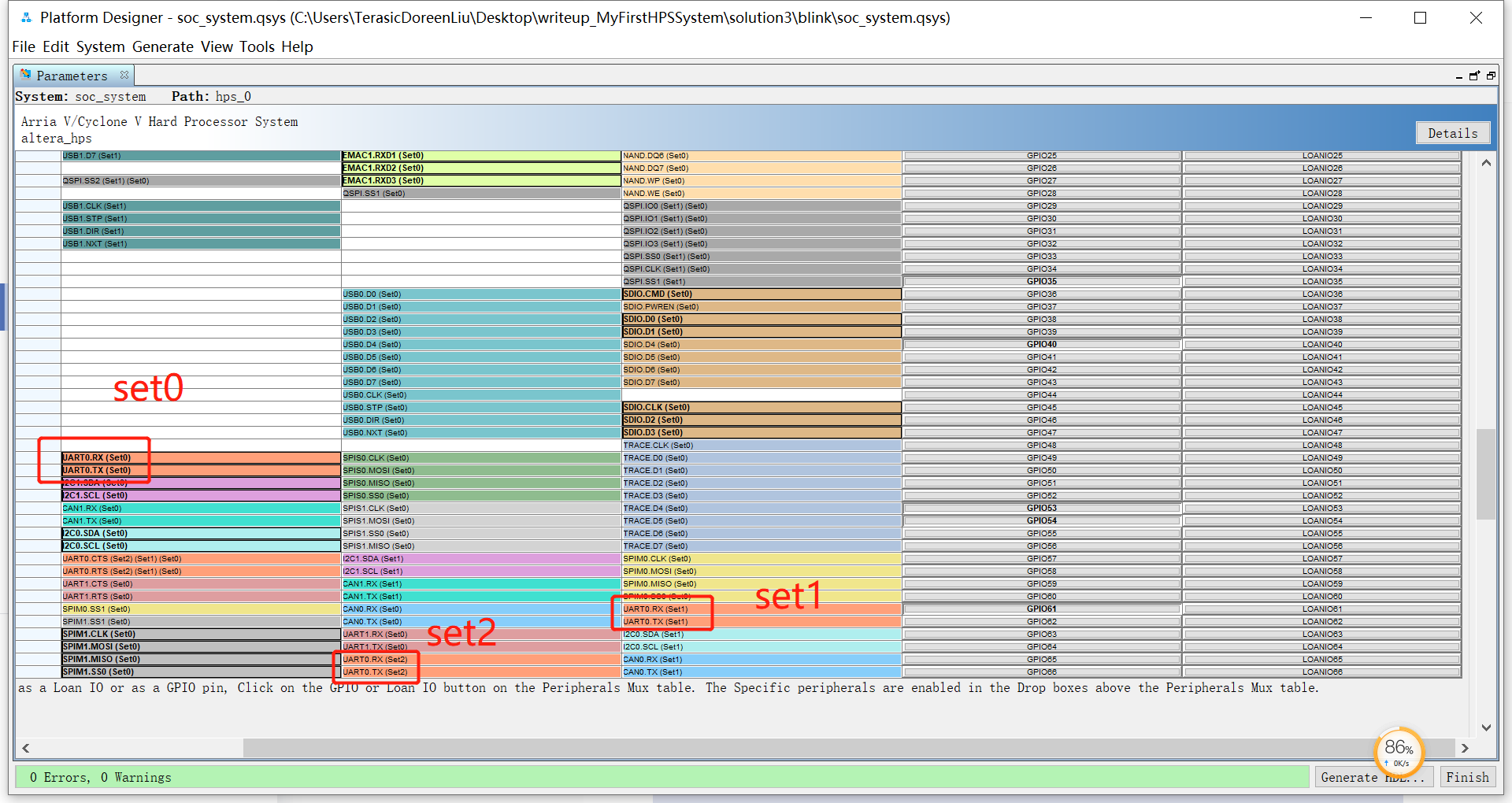

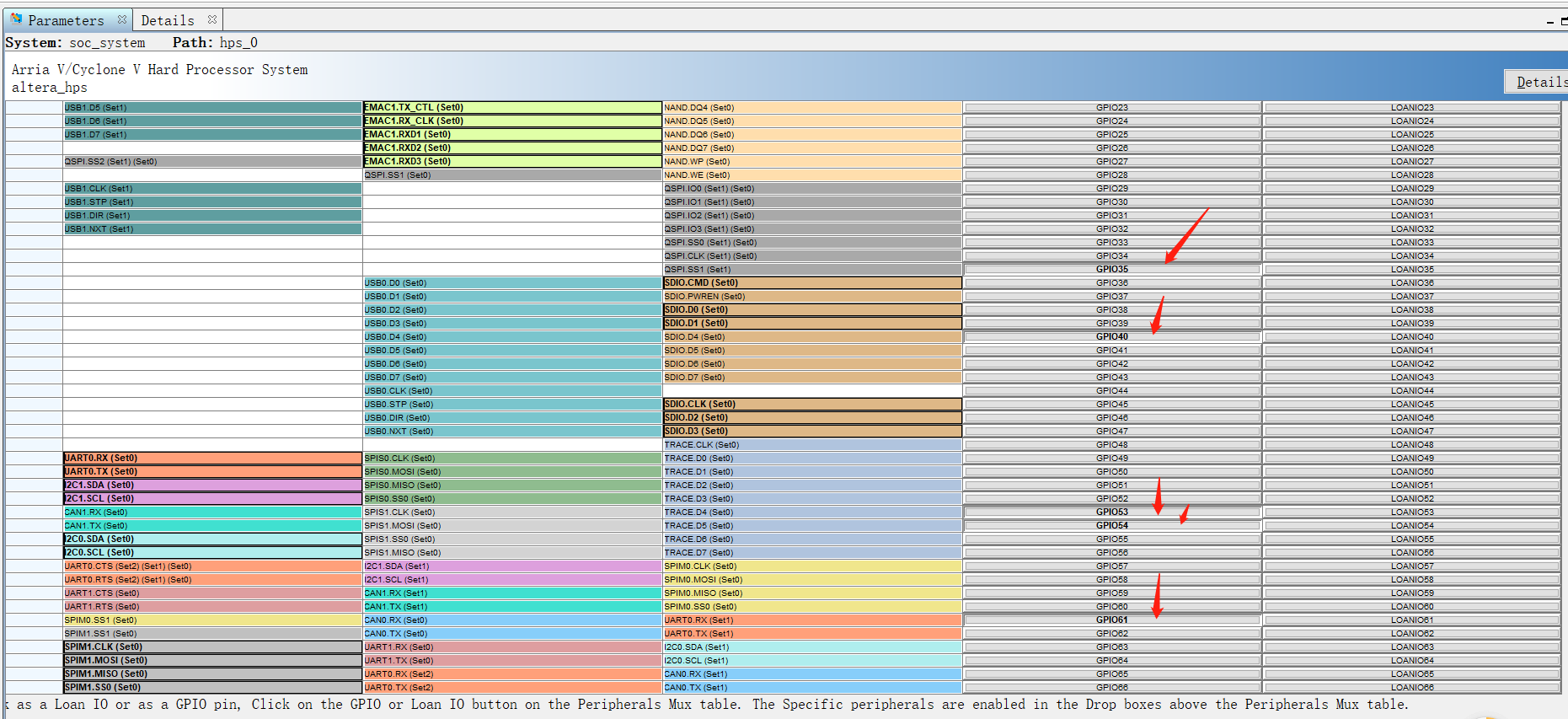

前面已经给大家介绍了SoC FPGA 是在单一芯片上集成了 基于ARM的硬核处理器系统(HPS)和 FPGA 逻辑资源的新型SoC 芯片。SoC FPGA 的 HPS端可以做到在有限的引脚资源上支持很多不同类型的外设,比如USB, I2C, SPI, UART, EMAC等等。这些引脚与外设不是一一对应的, 这些引脚是通过 HPS 引脚复用器切换不同的映射方式来支持不同功能外设的连接。这里映射方式选择有4种: set0 set1 set2 和 FPGA used。对应到具体的硬件产品上的设计时,引脚复用需要根据使用到的具体功能合理设置引脚复用。可能这样讲大家还是不能理解这个HPS IO复用是怎么去应用的, 别急,我来举个栗子:

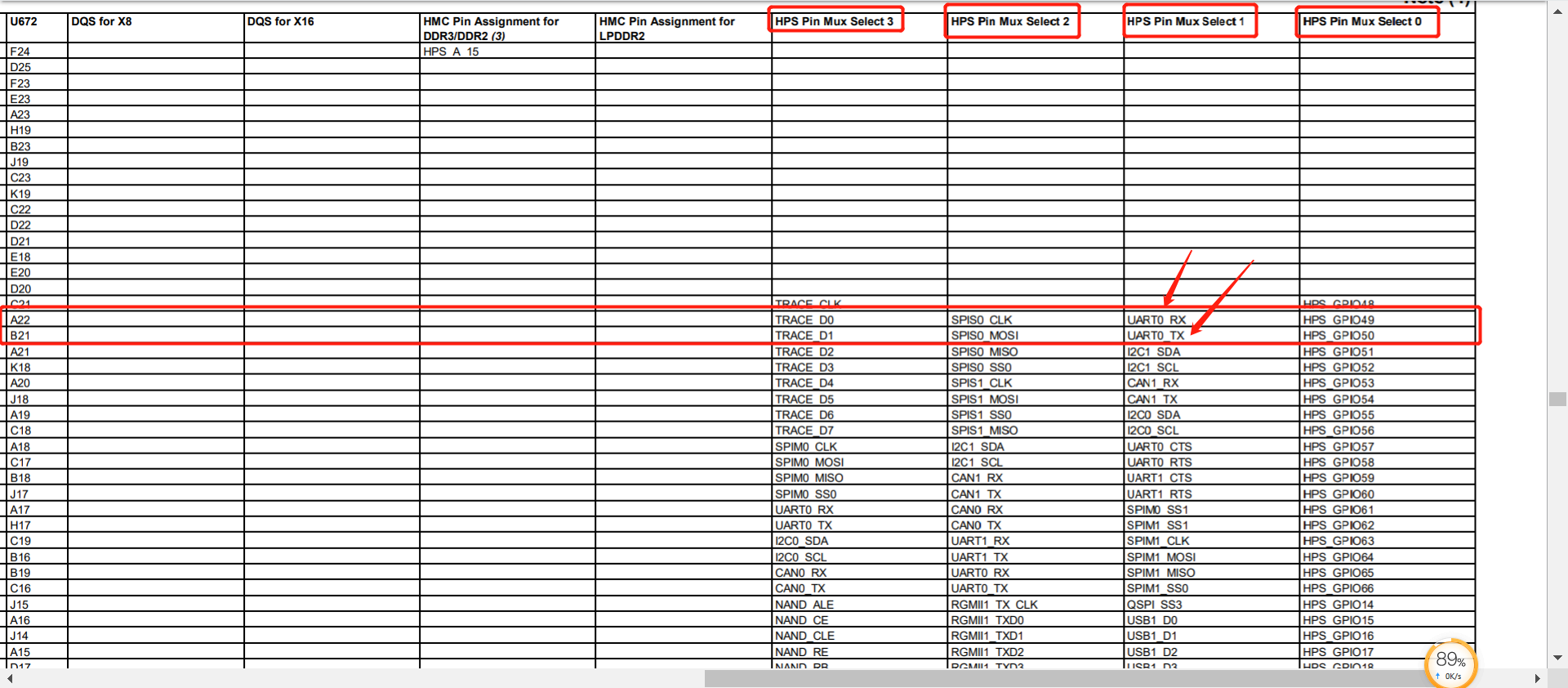

5CSEB6 器件(DE10-Nano上的器件)的A22 B21引脚复用如下图2 所示(查看器件引脚复用对应的完整情况可参考Intel的引脚信息表

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/dp/cyclone-v/5cseba6.pdf。),从截图可看到A22 和B21 可以被选择当TRACE功能,也可以被选择为SPI功能,或者是UART,或者直接就是GPIO功能。

(注意这个截图中的 HPS Pin Mux Select 0 1 2 3 代表四种不同选择,但 不是对应后面HPS IP设置界面的 HPS I/O Set0、1、2 。)

(图1)DE10-Nano开发板的5CSEB6 器件 引脚 信息对应表

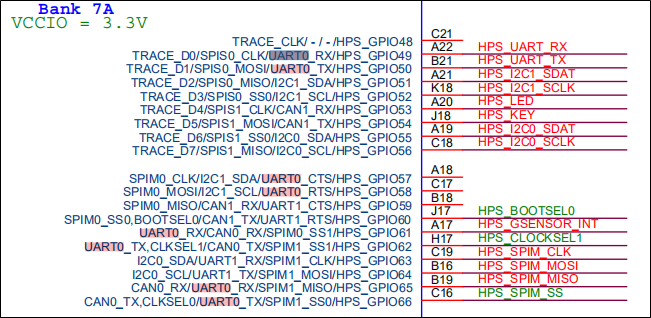

但5CSEB6 器件安装到DE10-Nano(http://www.terasic.com.cn/cgi-bin/page/archive.pl?Language=China&CategoryNo=182&No=1048)开发板以后,它的 A22 B21引脚被固定接UART0 设备了:

(图2)DE10-Nano 电路图

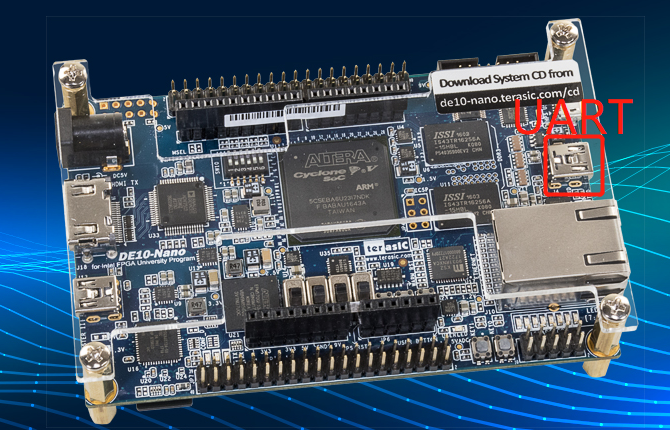

(图3)DE10-Nano 的实际硬件(UART接口)

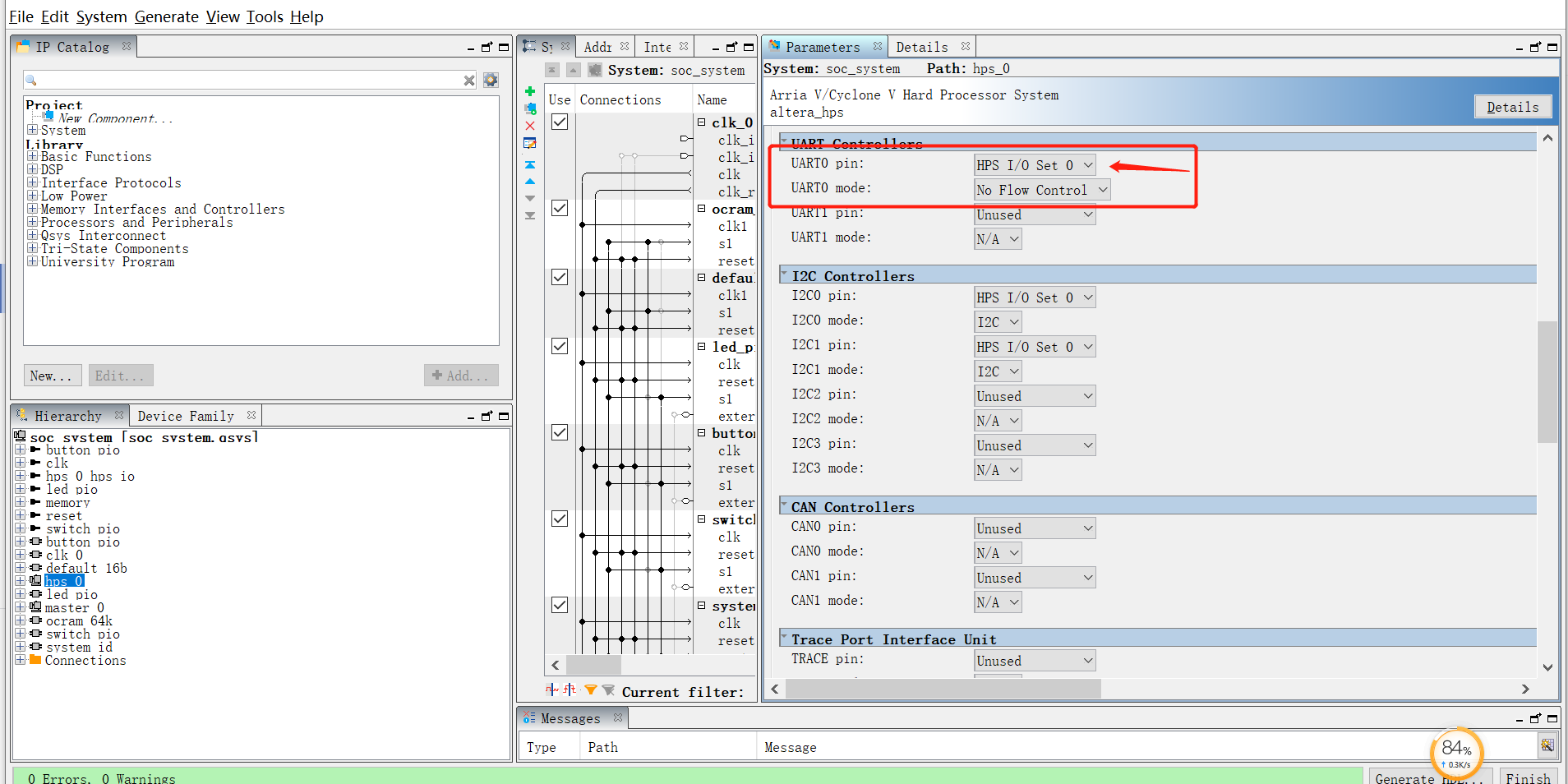

因为DE10-Nano 的外围电路已经固定到UART0, 那么用户在设置 HPS IP 时,UART0的 UART0 pin要设置为HPS I/O Set0 ,UART1不用设置(DE10-Nano硬件上是使用了HPS端的 uart0,没使用uart1)。这就是按照硬件具体情况设置HPS IP 的IO复用。

(图4)该界面是通过打开Quartus Prime软件里面的Platform Designer的HPS IP

那大家肯定会问,为啥 UART0 pin 这里是选 HPS I/O set0 呢?怎么不选择HPS I/O set1或者HPS I/O set2? 那是因为在HPS 映射方案里面set0 才将 A22 B21 映射为UART0了(如下图5所标注的)。(另外还可以参考我后来博客 https://www.cnblogs.com/DoreenLiu/p/14242046.html 的解释)

(图5)

如果这些可复用的引脚没有被复用,那么空闲的它们也可以被HPS GPIO外设使用。具体操作是在Peripherals Mux Table下, 单击倒数第二列中的GPIOxx按钮,即可启用对应的GPIO端口,这时无需设置set0 还是set1等 。这些GPIO 有用于连接HPS用户灯的,有用于连接HPS用户按钮的,等等。

(图6)

眼尖的用户可能发现最右边还有一排 LOANIO,这个是干什么用的呢? “LOAN” 是借贷的意思,这里是表示 当这些引脚没有被HPS外设所用的时候,也可以将其借给FPGA用,被FPGA所控制。 注意这时必须先配 这些管脚为HPS相应管脚再借给FPGA。这种情况在一般的实际应用中其实比较少见。

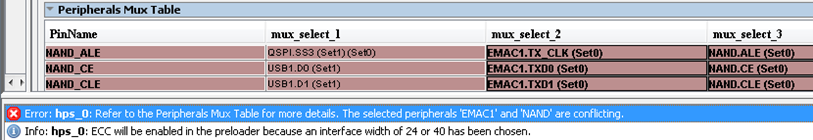

Pin Mux标签的底部是一个冲突信息提示框,显示每一引脚复用的使用情况。如果出现引脚冲突,这也会显示在提示框中。假设将一组管脚即分配外设EMAC1, 又分配给NAND 外设,显示框就会显示EMAC1的引脚和NAND的引脚使用冲突了(如图7所示),为解决这一冲突问题,需要查看开发板硬件实际对应情况。在允许生成系统前,应确保HPS组件的冲突信息提示框没有错误。

(图7)

关于HPS 端外设的引脚 要不要手动分配?请参考我后来的博客: https://www.cnblogs.com/DoreenLiu/p/14242046.html

无