逻辑门电路的延时分析

关于MOS管

NMOS:

PMOS:

NMOS是栅极高电平(VGS > Vt)导通,低电平断开,可用来控制与地之间的导通。适合用于源极接地时的情况(低端驱动),只要栅极电压达到4V或10V就可以了。

PMOS是栅极低电平(VGS < Vt)导通,高电平断开,可用来控制与电源之间的导通。虽然PMOS可以很方便地用作高端驱动,但由于导通电阻大,价格贵,替换种类少等原因,在高端驱动中,通常还是使用NMOS。

MOS管组成的逻辑电路:

我们课本里见到的最基本的逻辑门电路有与门,或门以及非门

但在实际的电路中基本上用的基本逻辑门单位是与非和或非

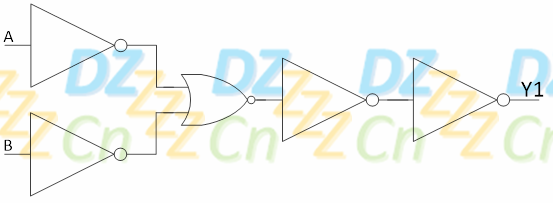

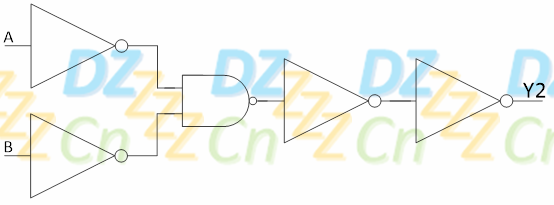

例如最常用的 74HC系列与、或、非逻辑器件数据手册(datasheet)的逻辑原理图(Logic Diagram),我们会发现上面三个门会是下图那样的:

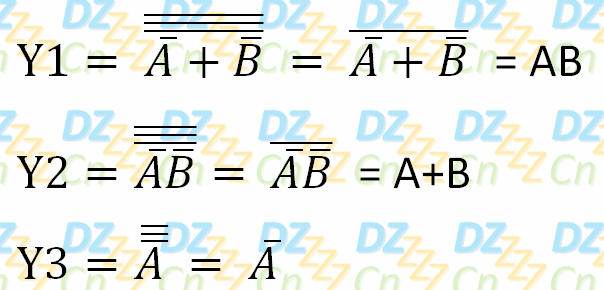

我们利用以前教材上的知识来化简一下这三个组合逻辑,如下所示:

那么这里我们就需要搞明白两个问题

1 为什么要用与非、或非实现这些基本的门电路?

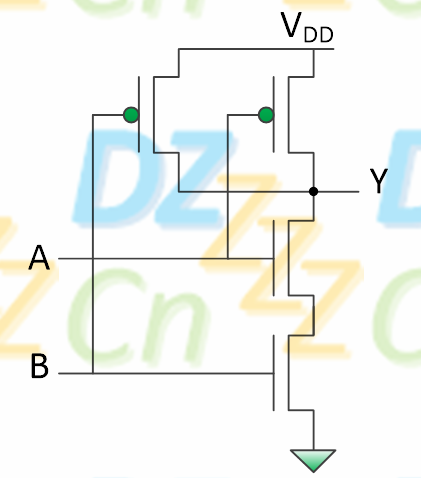

先要清楚CMOS逻辑电路设计中的基本的门电路的样子:

(1)“非门”逻辑构造:

上面带圆圈的是PMOS晶体管,下面是NMOS晶体管,从开关的角度来看,PMOS管相当于PNP三极管,输入为“1”时截止,输入为“0”时导通;而NMOS则相当于NPN三极管,输入为“1”时导通,输入为“0”时截止

当输入为“0”时,下面的NMOS截止,而上面的PMOS导通将输出拉为高电平,即输出“1”。当输入为“1”时,上面的PMOS截止,而下面的NMOS导通将输出拉为低电平,即输出“0”,很明显,这就是个“非门”逻辑。

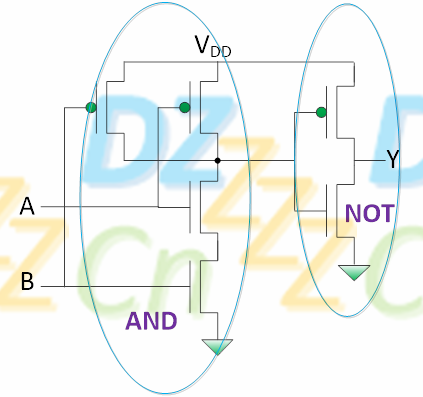

(2)“与非门”逻辑的结构:

当上图中的任何一个输入(A或B)为低时,都将有一只PMOS导通,从而将输出Y拉高,因此该电路是“与非门”逻辑,那么“与门”逻辑就是在“与非门”后面加一级“非门”了,如下图所示:

如果直接反过来的话也可以实现所谓的与门,但是我们需要注意的是NMOS可以有效地传输低电平,PMOS可以有效的传输高电平,两者相配合就可以达到轨对轨的输出,相反则有损耗。

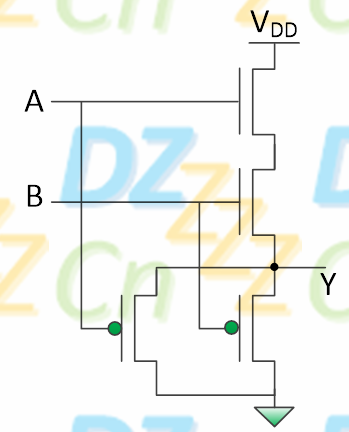

(3)“或非门”的实现

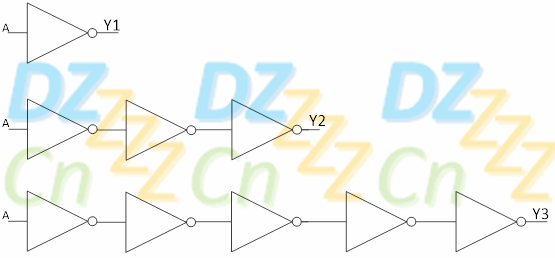

2 为什么要插入那么多的非门?

实际上这样做的目的是优化逻辑门,减少延时。CMOS集成电路中的最有延时告诉我们,存在最优级数,最少级数不一定是最优的

第二个实现非门是最优的,可以获得最快的速度。

还有两个问题

1.数字电路设计中,如何提高电路的翻转速度?

2.数字电路设计中的D触发器的翻转与组合逻辑的反转速度分别是怎样的,两者之间有没有关系

posted on 2018-08-21 09:49 super_star123 阅读(9459) 评论(0) 收藏 举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号