FPGA基础架构总结

1.为什么FPGA的整体逻辑的速度有限制?

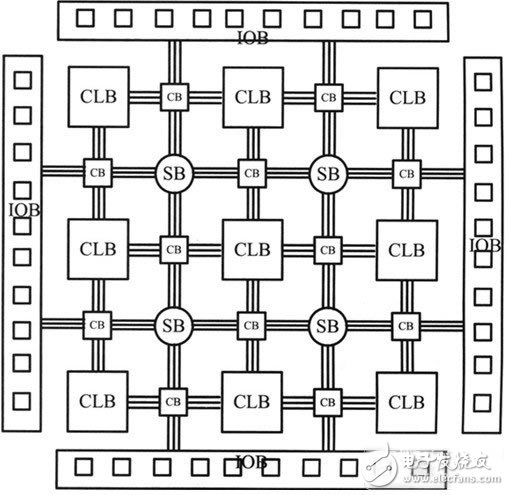

与ASIC相比较,AS指的是(application specific)专用集成应用,而FPGA是可编程逻辑,在实现的过程中,AS是直接用最基础的逻辑门实现数字电路的搭建,而FPGA是用LUT+FF搭建,它是可编程,也就是说可重构的,所以被设计成了一种岛状的逻辑块矩阵电路,每个逻辑块又有很多的子逻辑块组成,每个子逻辑块就包含有实现任意电路的元素,包括LUT(查找表)用于组合逻辑的实现,FF(触发器)用于时序逻辑的实现,逻辑块之间是布线的管道,,其中有各种固定长度的线以及连接这些线的开关。而对于ASIC而言,全部是按照数电逻辑实现的,导线也只是单纯的导线,没有开关的中断。

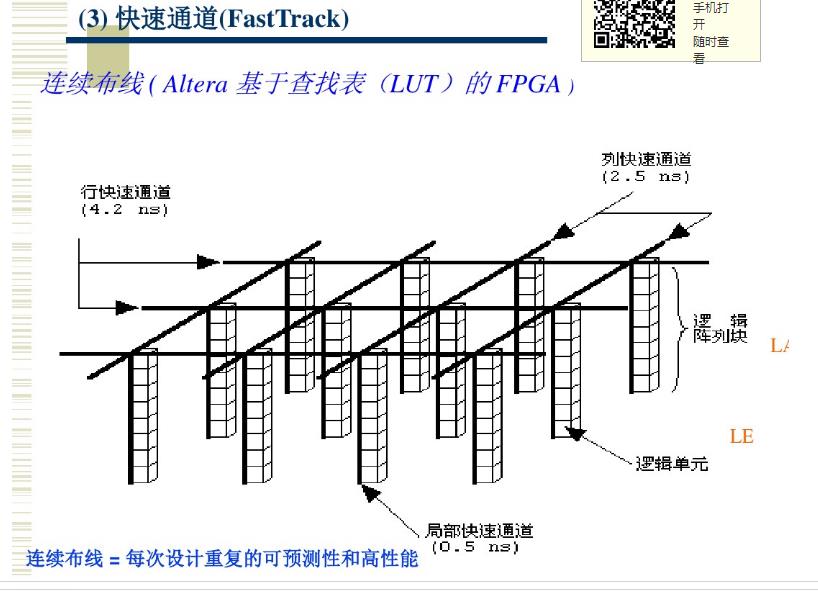

可以观察到这个FPGA的布线在十字路口那块有多么的复杂,研究表明,对于一个只有组合逻辑和时序逻辑,没有存储等的电路,在FPGA上实现需要40倍的ASIC面积以及3-4倍的关键路径延时,12倍的功耗。这些都是布线惹的祸,布线结构面积占了大约总面积的60%-70%。

FPGA的可编程单元可以由反熔丝、闪存单元以及SRAM内存单元实现。其中的反熔丝技术创建的是一个一次性编程的单元。

2.FPGA内部逻辑组成架构详解

先放一个基本的FPGA组成模块图:

全局的来看的话,

全局的来看的话,

在FPGA中所有的逻辑功能都是由CLB来实现的,他的工作原理如下:

软件自动完成的内容包括:首先输入经过FPGA芯片IO管脚后进入可编程连线,作为地址线输入到LUT,LUT查找相应数据输出就实现了组合逻辑。clk通过GPIO输入后进入芯片内部的专用时钟通道,直接连接到触发器的时钟端,D触发器的输出接到I/O,实现结果输出到芯片管脚。

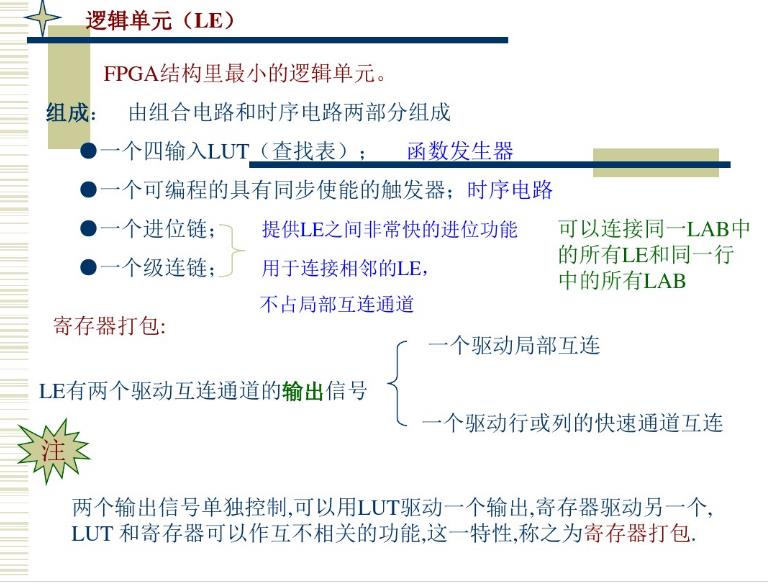

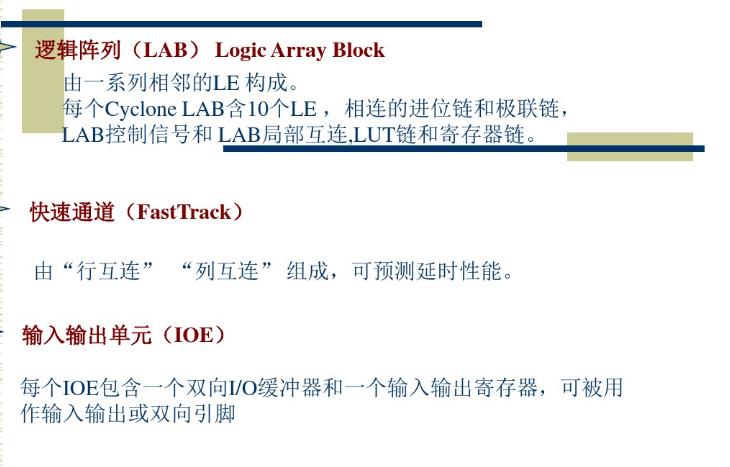

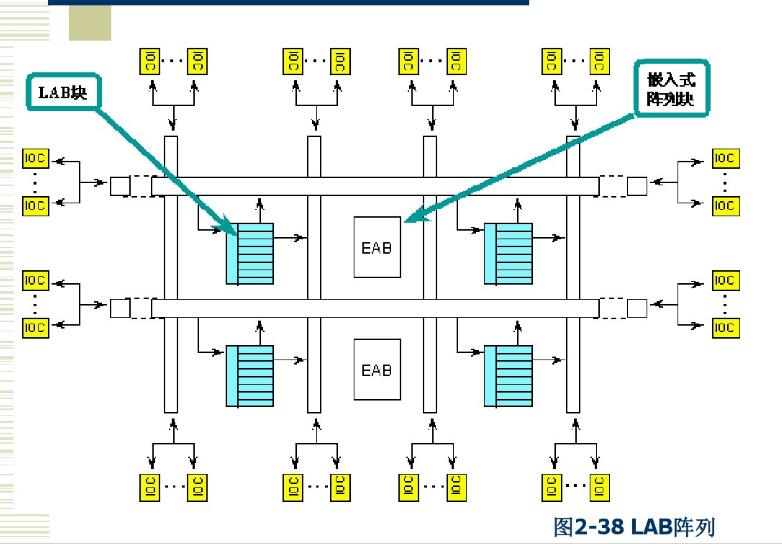

altera器件的结构组成:嵌入式阵列块(EAB)(用于存储)、逻辑阵列块(LAB)(用于逻辑实现)、快速通道互联(Fast Track),IO单元(IOE)。对于其基本的组成单位LE有:

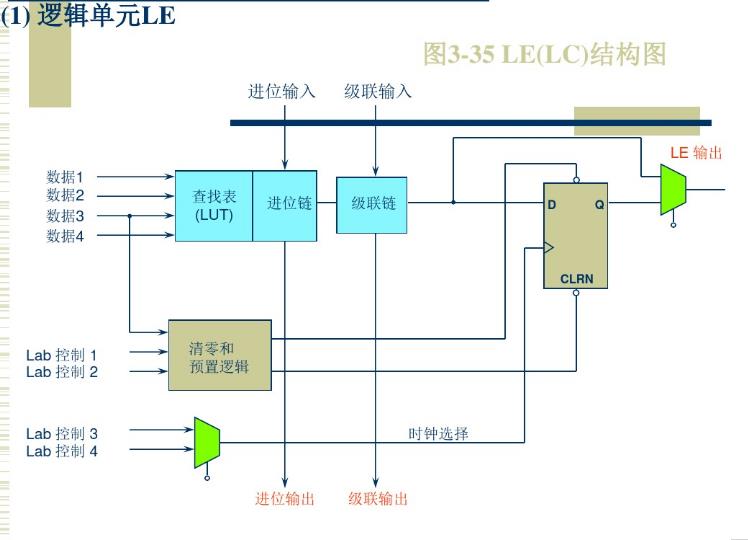

LE作为FPGA的最小组成单元,其组成部分包括LUT,用于同步的D触发器,进位链,级联链。

cyclone的LE具体内部组成:

简化后如下图:

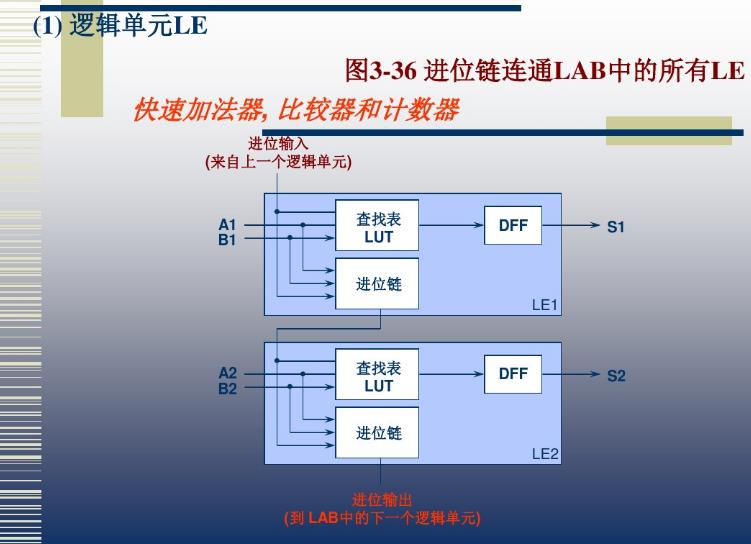

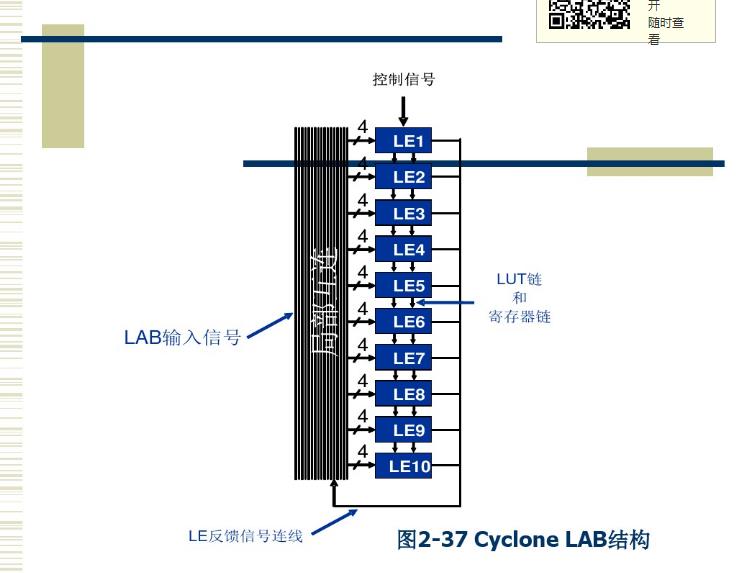

多个LE通过级联链以及进位链以及行列快速通道相连接,得到一个个LAB,对于Cyclone而言,是10个LE组成一个LAB,如下图

更加直观的话:

结论:LUT可以直接生成移位寄存器,怎么生成的呢?

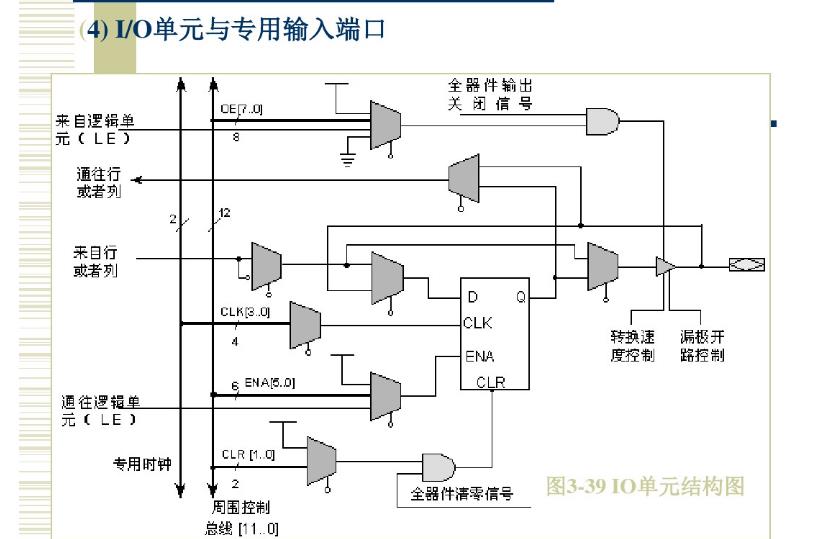

IOB的具体组成:

EAB的组成:

EAB的字长可以控制 ,此外,EAB可以组合成更大的模块。它可以用来实现乘法器,实际上是一个输入输出上都带有寄存器的灵活的RAM电路,即可以用来做存储器,也可以实现逻辑功能。

EAB与LAB之间的关系:

但是在具体编程中如何实现指定所使用的资源是什么呢?

此外

扇入扇出太大或者太小的处理方法http://blog.sina.com.cn/s/blog_b381ebd10102vw6g.html

关于如何减少FPGA设计中逻辑资源的占用:(网上找的主要的几种解决的方法)

更改综合策略,采用资源共享;(如何更改?)如果某个某块大量使用寄存器时可以考虑是否可以采用RAM代替;从架构上分析冗余并进行优化,之后再结合个别FPGA的实现特征,如果实在对资源比较在意而对性能要求不高,就可以考虑用时间换空间,用并行替串行;良好的代码习惯和风格 暂时就那么多,以下都是我在编程时发现的问题,总结一下,怕以后忘了,以我目前的水平不明白类似关键路径,组合数目什么高深理论,这都是我从实际中学到的,比看书学的印象深刻得多.慢慢来吧,我想我以后也会明白那些高级的东西了!

一....尽量不要使用"大于""小于"这样的判断语句, 这样会明显增加使用的逻辑单元数量 .看一下报告,资源使用差别很大.

例程:always@(posedge clk)

begin

count1=count1+1;

if(count1==10000000)

feng=1; //no_ring

else if(count1==90000000)

begin

feng=0; //ring

count1=0;

end

end //这么写会用107个逻辑单元

// 如果把这句话if(count1==10000000)改成大于小于,报告中用了135个逻辑单元

二.....一定要想尽办法减少reg寄存器的长度

上次把[30:0]改到[50:0],报告里逻辑单元从100多直升到2000多!!!太吓人了,至于为什么我就不知道了哈!

三....case语句里一定要加default if一定要加else

如果是组合逻辑的设计,不加default或else的话,不能保证所有的情况都有赋值,就会在内部形成一个锁存器,不再是一个纯粹的组合逻辑了,电路性能就会下降.

例如:case({a,b})

2'b11 e=b;

2'b10 e=a;

endcase

//不加default,虽然只关心a=1时的结果,但是a=0的时候,e就会保存原来的值,直到a变为1

//那么e要保存原来的值,就要在内部生成锁存器了.

四....尽量使用Case语句 而不是if--else语句

复杂的if--else语句通常会生成优先级译码逻辑,这将会增加这些路径上的组合时延

用来产生复杂逻辑的Case语句通常会生成不会有太多时延的并行逻辑

五...组合逻辑的always块中,要注意所有的输入全部放入敏感变量表里

比如:always@(a or b)

begin

out=(a&b&c);

end

posted on 2018-05-21 22:39 super_star123 阅读(7122) 评论(0) 收藏 举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号