PCIe(一)

PCI Express是一种总线接口,是计算机主板上最大尺寸的接口,计算机上的网卡、声卡、以及独立显卡,视频采集卡都是采用的这种接口。是一种高带宽串行互联标准,代替了基于总线的通信架构。

主要用于需要直接与CPU通信的设备使用,目的是为平台输出更加强力的图形能力,弥补核显的不足。根据总线位宽不同而有所差异,包括X1、X4、X8以及X16(X2模式将用于内部接口而非插槽模式)。

PCI Express X1规格支持双向数据传输,每向数据传输带宽250MB/s,PCI Express X1已经可以满足主流声效芯片、网卡芯片和存储设备对数据传输带宽的需求,但是远远无法满足图形芯片对数据传输带宽的需求。

因此,必须采用PCI Express X16,PCI Express X16也支持双向数据传输,每向数据传输带宽高达4GB/s,双向数据传输带宽有8GB/s之多。即16条点对点数据传输通道连接。

(带宽:信号传输的最大速率,单位时间内能传输的数据的量,信道容量(最大传输速率)与信道模拟带宽成正比)https://wenku.baidu.com/view/7d5f4b010740be1e650e9a64.html

在FPGA中实现PCIe的通信协议有其自己独特的优势,

- 因为在目前的大多数FPGA中集成了Gbit的收发器IP,可以实现高速串行协议,包括千兆以太网、PCIe等,

- 可以省去专用接口芯片的费用,

- 利用FPGA的可编程特性,大大提高设计的灵活性、适应性和可扩展性。

- Altera的PCIe硬核IP包含处理层,链路层和物理层所要求的全部功能,以及大多数的可选功能。只需在IPCompiler中经过简单的参数设置即可生成全功能的IP模块,如果是作为端点设备,可以使用Avalon-ST接口或Avalon—MM接口适配器,将应用层映射为处理层的TLP。Avalon—ST适配层将应用层的Avalon—ST接口映射到PCIe处理层的TLPs。

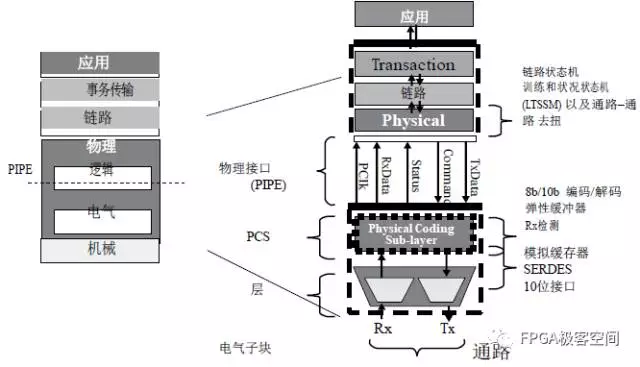

通常将PCI-e总线协议分为3层处理:

PCI-e协议层

通常将机械层和物理层合并为物理层(PHY Layer)(PLP),紧接着第二层为数据链路层(DLL)(DLLP),第三层为事务传输层(TL)(TLP),应用层不算在内。

物理层中的机械层:

机械层定义了诸如对连接器、卡外形尺寸、卡检测和热插拔等要求的机械环境。

物理层中的电气和逻辑层:

-

-

物理层下的电气层实现包括收发器、模拟缓冲器、串行/解串行器(SerDes)在内的模拟器件以及10位接口。

-

物理编码子层(PCS)把每8位数据字节编码/解码为10位代码。这种编码特性不仅能检查有效字符,而且也限制了被发送的“0”和“1”数量上的差异,从而同时在发射器和接收器侧保持了DC均衡,进而大大提高了电磁兼容性(EMC)和电气信号性能。

-

插入一个概念:

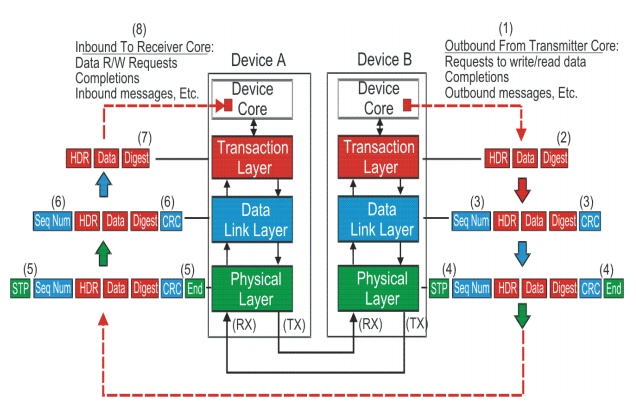

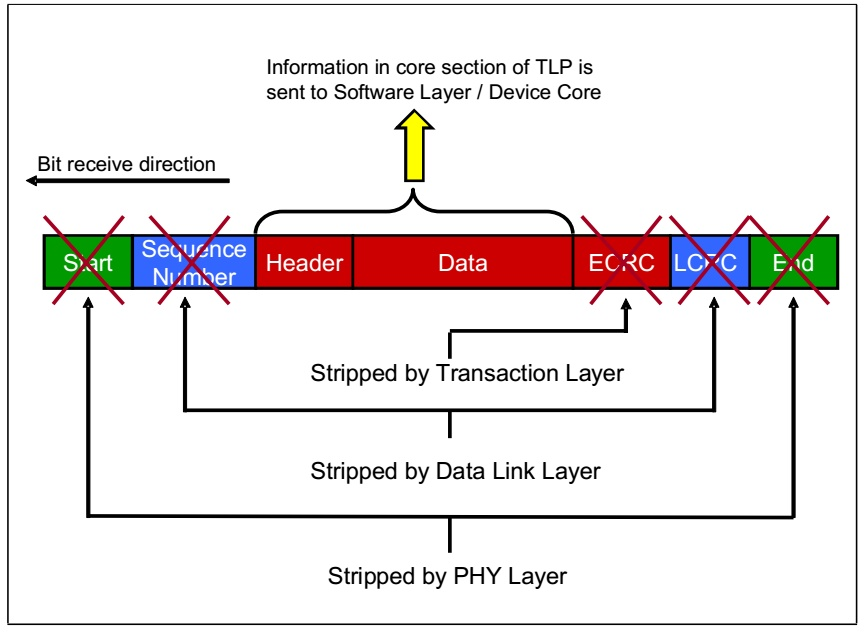

数据包:数据在PCIe网络上的传输过程,PCIe实际上是以数据包的形式在各系统间或数字接口的各层之间传输的。首先是应用层发起事务传输,事务传输层把把请求转换为一个PCIe数据包。数据链路层为该包添加序列号和链路CRC(LCRC)。数据链路层确保数据接收的正确性,然后在物理层PCIe链路上传输该事务。

数据链路层:实际上该层的主要作用是保证数据传输的可靠性,对接受或者发送的数据包进行各种校验处理。

数据链路层完成的主要任务是:

-

数据交换。接收发送方处理层的TLP包,并送到物理层。另外从物理层接收TLP包并送到接收端的处理层。

-

出错检测和裁决。LCRC和序列号(TLP Sequence Number)的生成;存储发送端的TLP用于再试重发;为TLP和DLLP做数据完成性检测(crc校验);DLLP的ack和nack响应;错误指示;链接确认超时重试机制。

-

初始化和电源管理。跟踪链路状态并传送链路活动、链路复位、链路失去连连等状态给处理层;

-

生成DLLP。用于链路管理功能包括TLP确认、电源管理、流程控制信息(VC通道初始化)交流。在链接两端的数据链路层点对点传输。

-

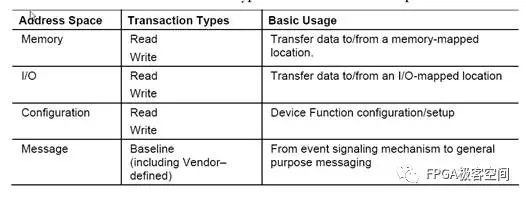

事务传输层:该层的主要作用命令请求和响应。一共有4种地址空间和三种处理类型。

创建出站和接收入站的事务传输层数据包(TLP)。TLP包括一个报头、一个可选数据配载以及一个可选的端到端CRC(ECRC)。TLP既可以是请求也可以是对请求(完成)的响应,它永远是4个字节(1个DWORD)的倍数。报头指定事务类型、优先级、地址,路由规则及其他数据包特征。发送事务传输层构建数据包报头、伺机添加ECRC并门控数据包的传输(直到有足够的远程流量控制额度可用)。接收事务传输层检查TLP格式和报头。

PCI-e基本功能和属性:

-

-

吞吐量:流量控制额度

-

QoS:传输类别和虚拟通道

-

RAS:数据完整性

-

RAS: 排序/PCI规则

-

主动电源管理

-

先进的出错管理

-

中断

-

关于端对端与点对点的连接方式的比较分析https://wenda.so.com/q/1361455318067037

在具体的FPGA 的IP核开发的流程中,已经写好的IP核实际上已经把上述三个层的相关规定都已经写好了,我们的主要职责就是要写出图中的和逻辑接口,将数据从Device Core输出的数据格式转换成IP的TL层可以接受的数据的格式。

所以搞清楚两个点就好,一是PCIe设备进行通信时的数据包的格式,其次就是PCIe系统的整体架构。用两个图就可以概全貌,这两个图说明PCIe设备是以点对点的结构连在一起的,并且点对点时间是以数据包的形式进行传输的。

PCIe的拓扑架构图

注意的是其中RC(Root complex)结构,,他负责的是把几种不同的传输协议聚合到一起,如内存的DDR总线,以及处理器的前端总线(FSB),实际上在PCIe中CPU的操作是由RC代替实现的。如图是一个简单的实例,完成由CPU发送读命令MRd,然后设备返回一个读完成信号CplD。

PCIe的数据传输过程图

TPL包的传输过程中,会出现TLP包的组装和拆解

posted on 2018-05-07 17:17 super_star123 阅读(6962) 评论(0) 收藏 举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号