探索ADC的原理(自制3位并行比较型ADC)

文档标识符:FLASH_ADC_T-D-P5

作者:DLHC

最后修改日期:2021.10.2

修改内容:分类

本文链接:https://www.cnblogs.com/DLHC-TECH/p/FLASH_ADC_T-D-P5.html

摘要

本文通过列举历史中出现的产品,梳理了模数转换器在20世纪30年代~~20世纪80年代末的发展历史。接下来,简要介绍模数转换器的原理、技术指标、分类和未来发展方向。最后,提供了一种自制3位FLASH型ADC的方法(该方法经过了作者的测试且价格在20元以下)。

参考文献

涉及到的数据手册(eyg7)

Flash ADC_Chapter 13 - Digital-Analog Conversion

《Analog-Digital Conversion》 Chapter I Walt Kester

ADC的历史

世界上记载的第一个”纯电子“的A/D转换器于1939年被亚历克·哈利·里夫斯(Alec Harley Reeves)发明,该设计的采样率为6KSPS,分辨率为5位。

亚历克·哈利·里夫斯设计的A/D转换器原理图,《Analog-Digital Conversion》 Chapter I Walt Kester

1947年,锗晶体管于贝尔实验室诞生。

1946年,ENIAC问世,现代数字计算机的鼻祖,为A/D的蓬勃发展做铺垫。(实际上,世界上第一台电子计算机是由艾奥瓦州立大学的数学与物理学教授约翰·文森特·阿塔纳索夫和他的研究生克里福德·贝里于1939年研发的阿塔纳索夫-贝里(ABC)计算机)

1948年,贝尔实验室发明了5位、8KSPS的逐次逼近型A/D转换器。

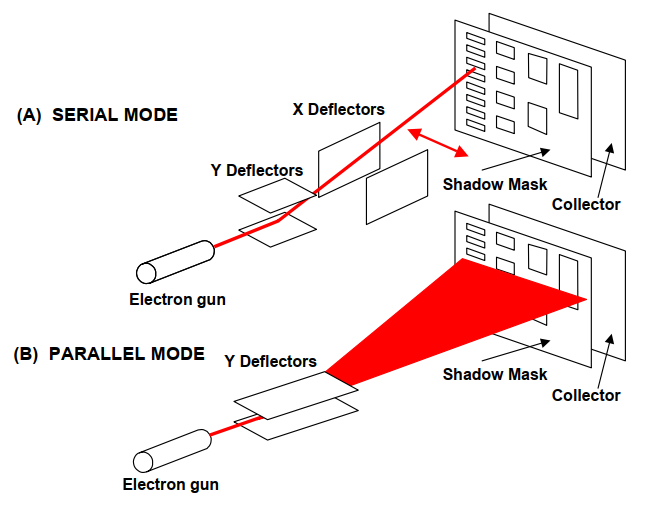

得力于电子束编码管技术,在1960年左右出现了12MSPS、9位的编码器(A/D)。

电子束编码管原理图,《Analog-Digital Conversion》 Chapter I Walt Kester

1954年,硅晶体管于德州仪器诞生。

1954年,伯纳德·M·戈登(Bernard M. Gordon)发明了11位、50KSPS的基于真空管的A/D,这被认为是世界上第一个商业化的A/D转换器。“Datrac”功率500W,售价8000~~9000美元。

伯纳德·M·戈登发明的 “Datrac”,《Analog-Digital Conversion》 Chapter I Walt Kester

1958/1959,集成电路问世,德州仪器(1958),仙童半导体(1959)。

1963~1965年,为了给美国军方的雷达提供高速A/D,贝尔实验室的John M. Eubanks和Robert C. Bedingfield研发了8位、10MSPS的A/D,其功率为150W、售价10000美元。

John M. Eubanks和Robert C. Bedingfield研发的A/D,《Analog-Digital Conversion》 Chapter I Walt Kester

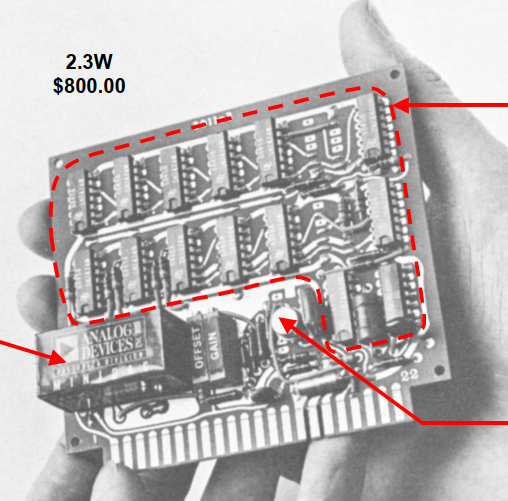

1969年,Pastoriza公司利用分立元件制造了12位、10us、2.3W的逐次逼近型A/D样机----"ADC-12U",售价800美元。

"ADC-12U"原型机,《Analog-Digital Conversion》 Chapter I Walt Kester

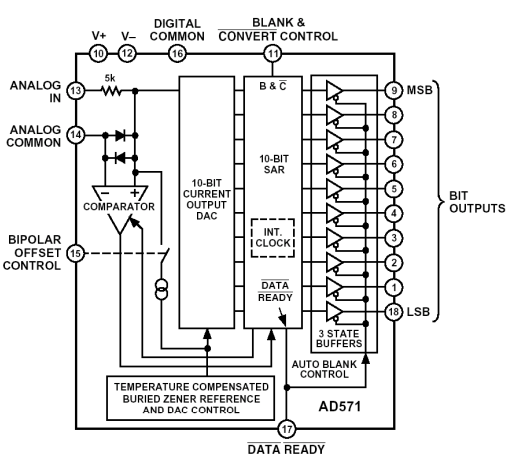

1978年,Paul Brokaw设计了第一个完整的单芯片ADC,型号为AD571,使用了双极型工艺,参数为:10位、25us、SAR结构。同年,诞生了最具重要意义的SAR ADC--AD574。这时的A/D可以说开始走向现代。

AD571,源

AD571框图,《Analog-Digital Conversion》 Chapter I Walt Kester

1988年,Crystal Semiconductor推出了世界上第一个单芯片商业化的ε-Δ ADC--CSZ5316,参数:16位、20KSPS,可以用于语音处理。

接下来的历史中,各厂商不断改进ADC的性能、推出更多不同用途的ADC。总而言之,就是让ADC进入千家万户。

ADC的原理

ADC(Analog to Digital Converter)是一类将模拟信号(连续信号)转换为数字信号(离散信号)的器件,按原理可分为:并行比较型A/D转换器(FLASH ADC)、逐次比较型A/D转换器(SAR ADC)和双积分式A/D转换器(Double Integral ADC)。

模拟信号,下图中的ui(t)是一个输入的模拟电压信号,可以想象成从一个麦克风输出的音频信号。

数字信号,现代计算机能够处理的信号,表现为下图中的“n位数字量输出”。

香农-奈奎斯特(Shannon & Nyquist)采样定理规定,使恢复出的信号不失真的条件:采样频率大于原始信号频率的两倍,即 Fs >= 2Fi

一个连续的电压信号ui(t)通过一个由方波CPs控制的开关S之后施加到电容C上,由于电容两端的电压不会突变,可知在S断开时C将维持ui(t)在开关断开瞬间的电压一段时间,直到开关S再次打开。这样,一个模拟的电压信号就转换成了采样展宽信号us(t),其中CPs的频率就是采样频率Fs。然后,由ADC的数字编码电路将采样展宽信号us(t)转换成n位的数字量dn-1 : d0并输出。

通过上述步骤,一个连续的电压信号就转换成了n位的数字量,而实现该过程的器件叫做模拟-数字转换器(ADC)。

AD转换的一般原理,"数字电子技术" SWPU

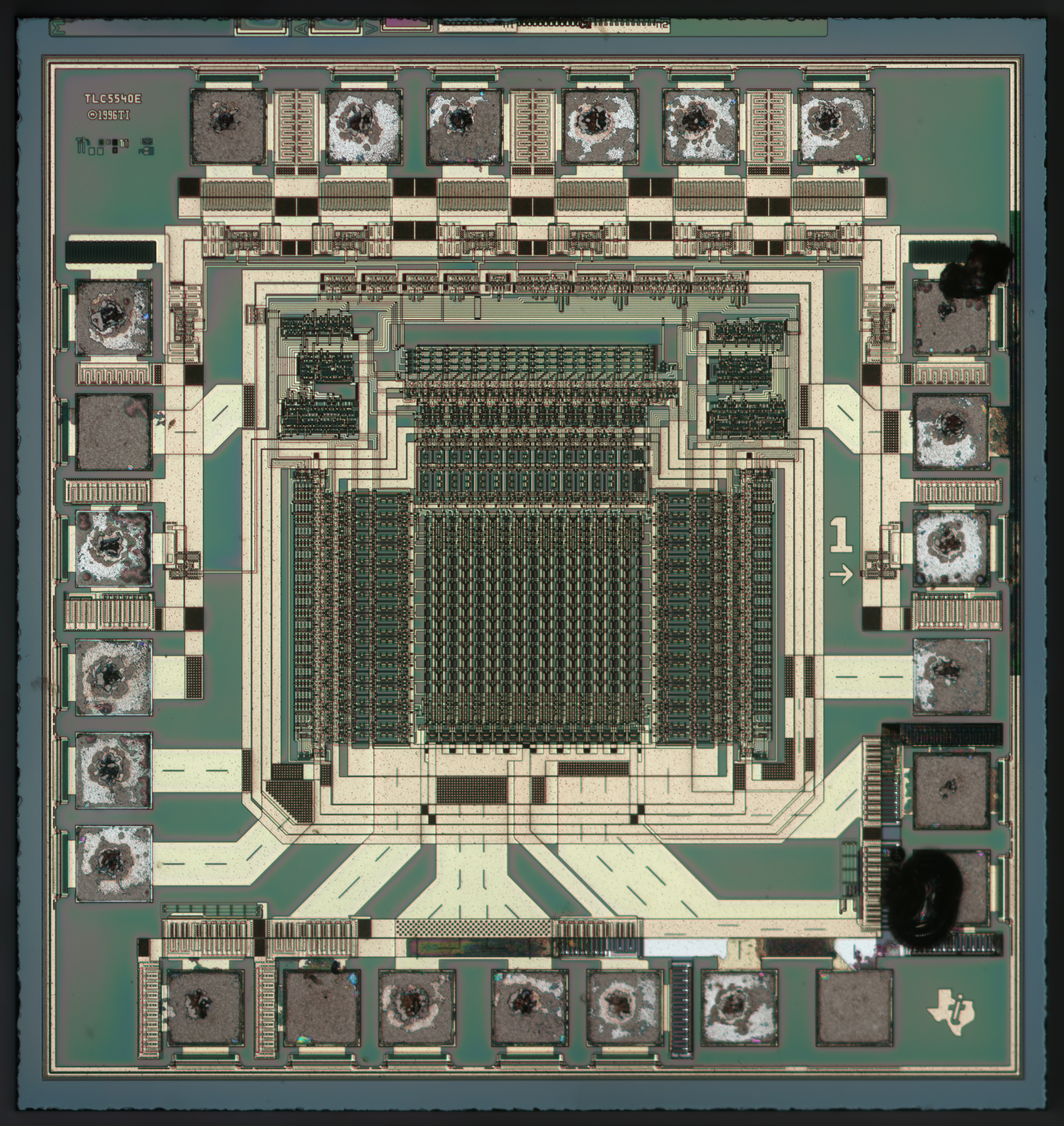

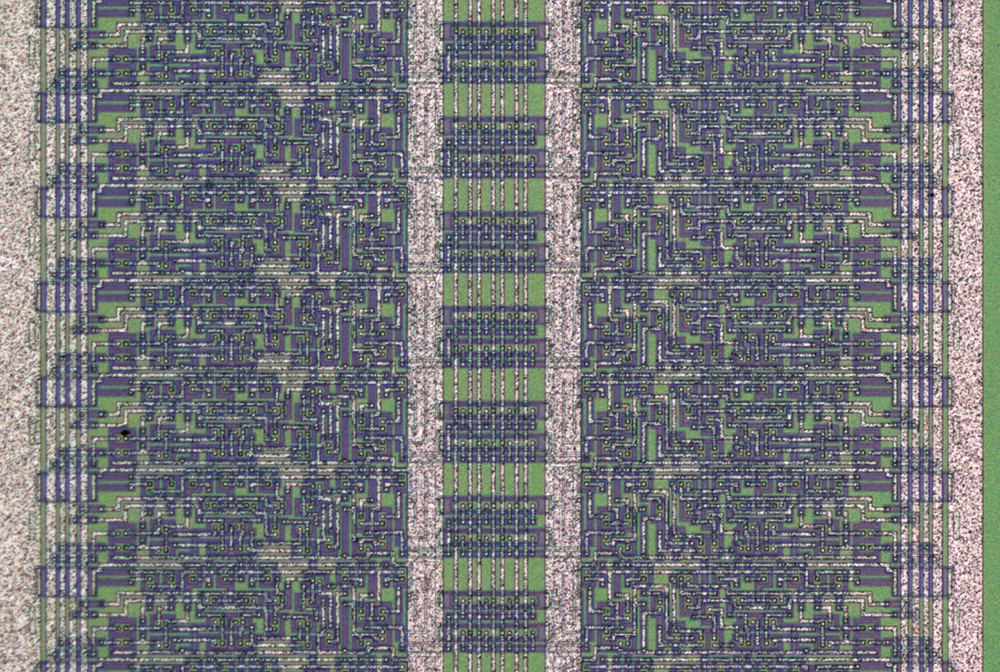

TLC5540I,8位、40MSPS、CMOS工艺的并行比较型A/D转换器的版图,https://zeptobars.com/,license: CC BY 3.0,未修改

ADC的主要性能指标

分辨率:ADC能分辨的最小电压,通常用位数表示,例如:8位。一个n=8位的ADC,参考电压为5V,则其能分辨的最小电压为 5 / 2^n = 19.53mV

转换时间:ADC从控制信号到来开始,到输出端得到稳定的数字信号所经历的时间。

转换精度:ADC输出的数字量所表示的模拟值与实际输入的模拟量之间的偏差。

ADC的分类

并行比较型A/D转换器:这是本文尝试构建的ADC,其由电阻分压器、电压比较器(运算放大器)、D触发器和优先级编码器构成。其原理简单,将在后文介绍。

优点:1.转换时间最短,其转换周期为通过比较器、触发器和优先级编码器的时间总和(见下式),这个数值通常很小。

T转 = T比 + T寄 + T编

缺点:1.造价高昂,随着分辨位数的提高,所需的元件几乎按几何级数增长,如:一个n位的并行比较型ADC,需要2^n - 1个比较器和2^n - 1个触发器,假如n=12,那么一共需要8190个比较器和触发器!

2.对集成电路的工艺要求很高。

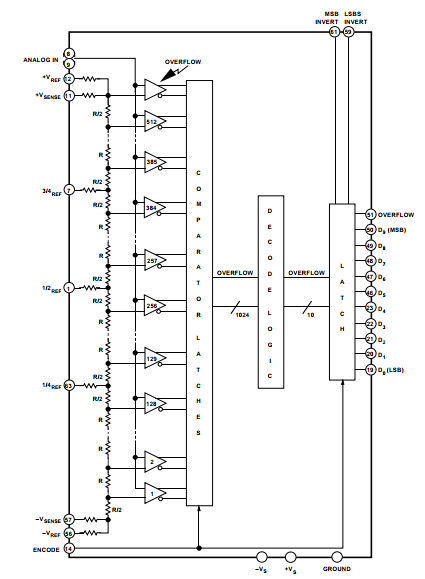

常见的型号:AD9012,TTL工艺,分辨率为8位,采样率为100MSPS,模拟输入电压范围 -Vs~~+0.5V(Vs为芯片供电电压)。

AD9002,ECL工艺(射极耦合逻辑),分辨率为8位,采样率为150MSPS,模拟输入电压范围 -Vs~~+0.5V(Vs为芯片供电电压)。

AD9020,TTL工艺,分辨率为10位,采样率为60MSPS,双极性模拟输入(+-1.75V)。

3位并行比较型A/D转换器原理图,《数字电子技术》第六版 康华光

AD9012原理图,Analog Devices

AD9002原理图,Analog Devices

AD9020原理图,Analog Devices

1107PV2,苏联,8位、20MSPS,典型的并行比较型A/D转换器的版图,https://zeptobars.com/,license: CC BY 3.0,未修改

1107PV2,苏联,8位、20MSPS,典型的并行比较型A/D转换器的比较器的版图,https://zeptobars.com/,license: CC BY 3.0,未修改

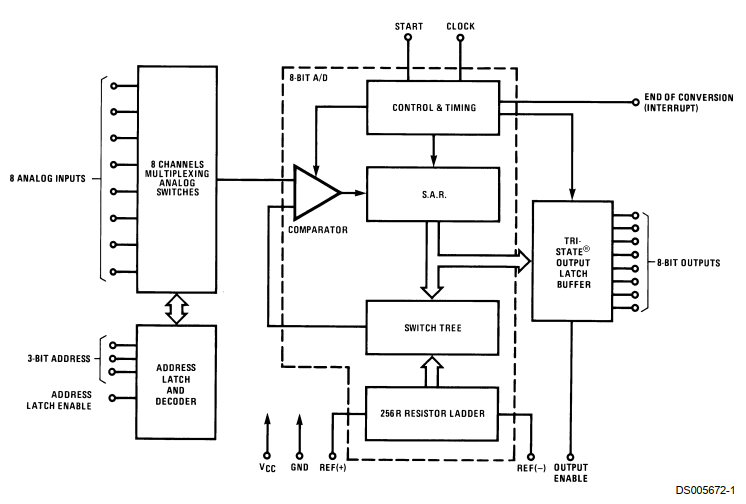

逐次比较型A/D转换器:原理像天平,对输入的模拟电压信号与不同权值的电压做多次比较,使得转换所得的数字量在数值上不断逼近输入的模拟量。通常由控制逻辑电路、数据寄存器、移位寄存器、D/A转换器(Digital Analog Converter)和电压比较器构成。

优点:1.转换速度快。其转换周期等于 分辨率 * 时钟周期(见下式),如一个8位的逐次比较型A/D转换器,时钟周期为10us,则其转换周期为80us。

T转 = n * Tclk (n为分辨率)

常见的型号:1.ADC0808/ADC0809,8位逐次比较型A/D转换器,转换时间100us,输入电压范围0~~5V,可接入8个模拟量输入。

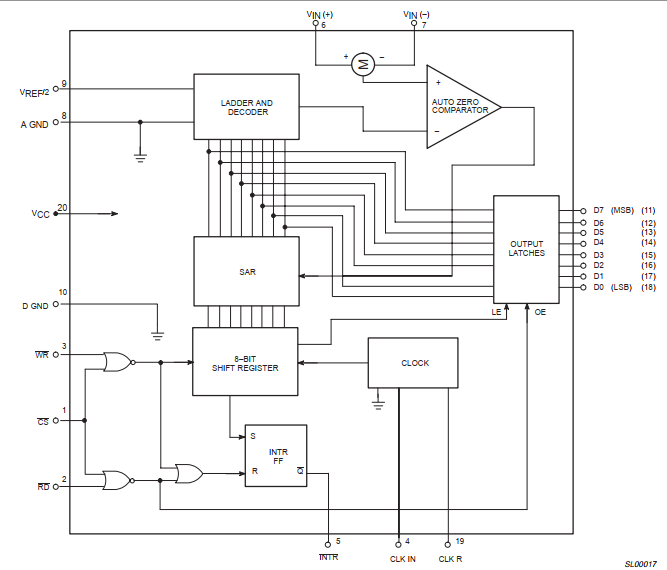

2.ADC0803/ADC0804,8位逐次比较型A/D转换器,在1MHz的时钟频率下,转换时间在66~~73us之间,支持一对差分模拟电压输入。

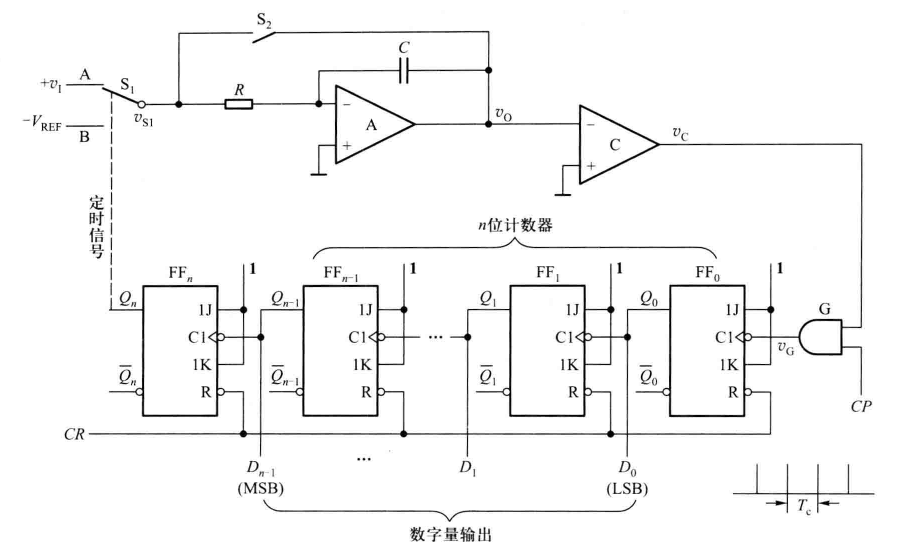

逐次比较型A/D转换器原理图 ,《数字电子技术》第六版 康华光

ADC0808/ADC0809原理图,National Semiconductor

ADC0803/ADC0804原理图,Philips Semiconductors

双积分式A/D转换器:一种间接的A/D转换器,其分别对输入电压和参考电压进行两次积分,将输入电压平均值变换成与之成正比的时间间隔,然后利用时钟脉冲和计数器测出此时间间隔,进而在输出端得到与模拟量相应的数字量。通常由积分器(运算放大器及相应的外部电路)、过零比较器(运算放大器)、时钟脉冲控制门和计数器等构成。

优点:1.抗工频干扰能力强。通过对输入电压的平均值进行变换来实现抗干扰。

缺点:1.转换速度最慢。

常见的型号:TLC7135,4.5位双积分式A/D转换器,CMOS工艺,差分电压输入。

双积分式A/D转换器原理图,《数字电子技术》第六版 康华光

TLC7135数字部分原理图,Texas Instruments

ADC的未来发展方向

ADC在未来会变得性能更强、价格更低、功耗更低、通用性和专业性更强。

性能:从历史上看,对ADC性能的改进主要集中在改进架构和改善制造工艺两个方面。ADC有很多架构,典型的包括:FLASH、SAR和双积分;其他的有:流水线等。在集成电路发展的过程中,出现了许多的工艺:双极性、ECL、CMOS、CB、BiCMOS、GaAs......这些工艺可以帮助改进ADC的性能。

价格:随着集成电路工艺的不断成熟,价格变低只是时间问题。

功耗:得力于集成电路工艺的改善,如:使用更低线宽的IC的功耗会低于高线宽的IC。功耗同时也取决于ADC架构。

元件清单(” * “为可选)

------------------------------------------------------------时钟发生器部分--------------------------------------------------------------------

NE555 *1

*DIP-8芯片座 *1

8位拨码开关 *1

*3pin排针 *1

3.9K电阻 *1

68K电阻 *1

10uF无极电容 *1

1uF无极电容 *1

100nF无极电容 *1

10nF无极电容 *2

1nF无极电容 *1

100pF无极电容 *1

10pF无极电容 *1

1pF无极电容 *1

所有元件合照(时钟发生器部分)

-----------------------------------------------------------------------------------------------------------------------------------------------

------------------------------------------------------------数模转换器部分--------------------------------------------------------------------

MCP6004 *1(可以使用LM324替换)

*DIP-14芯片座 *1

CD4042B *1

CD4532B *1

*DIP-16芯片座 *2

2K可调电阻器 *1

330R电阻 *3

390R电阻 *1

1K电阻 *5

LED-G *3

*Pin-3排母 *1

*Pin-2排针 *1

所有元件合照(数模转换器部分,不含Pin-2排针)

-----------------------------------------------------------------------------------------------------------------------------------------------

电路原理

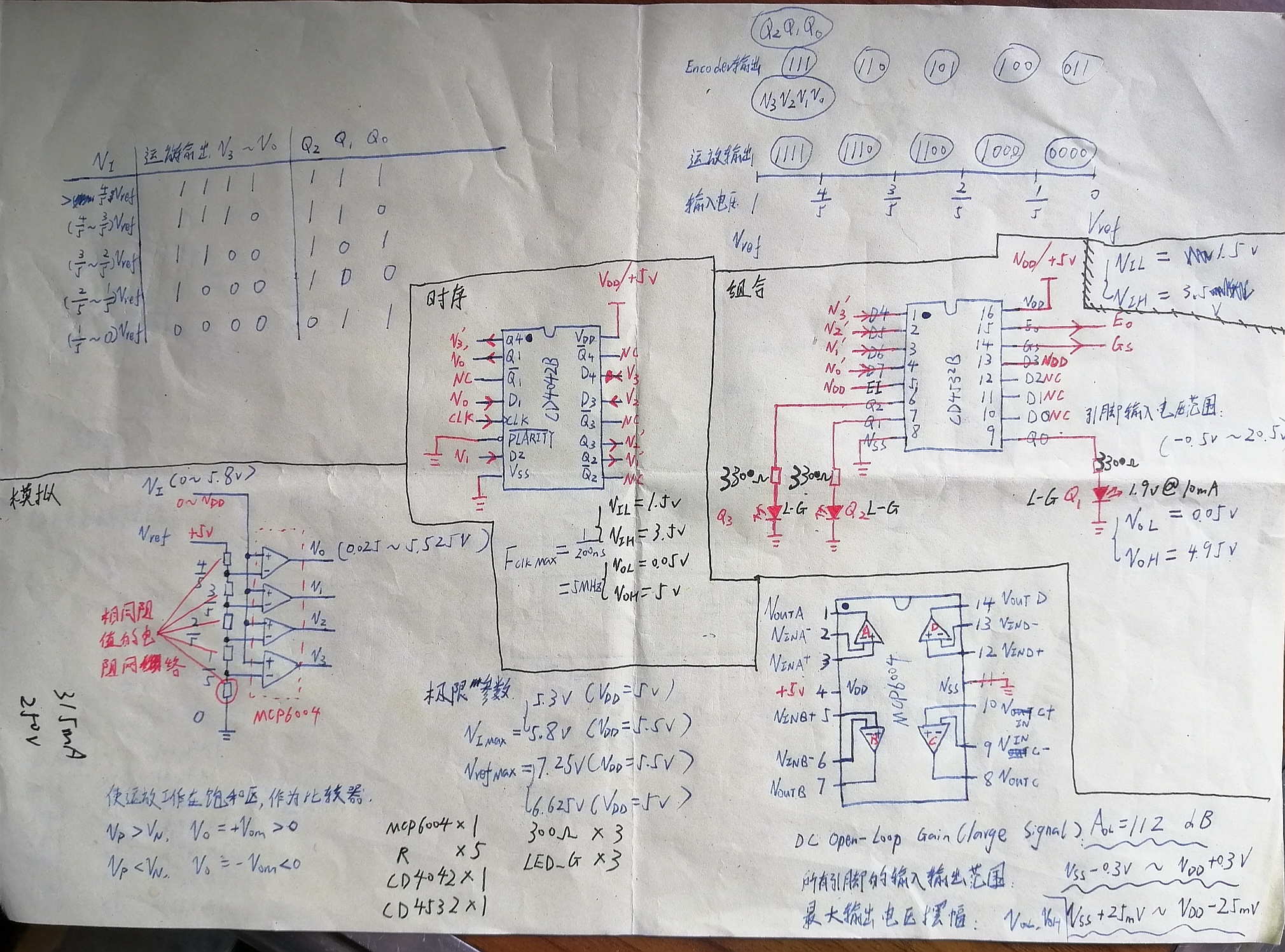

总原理图(1)

总原理图(2)

------------------------------------------------------------时钟发生器部分--------------------------------------------------------------------

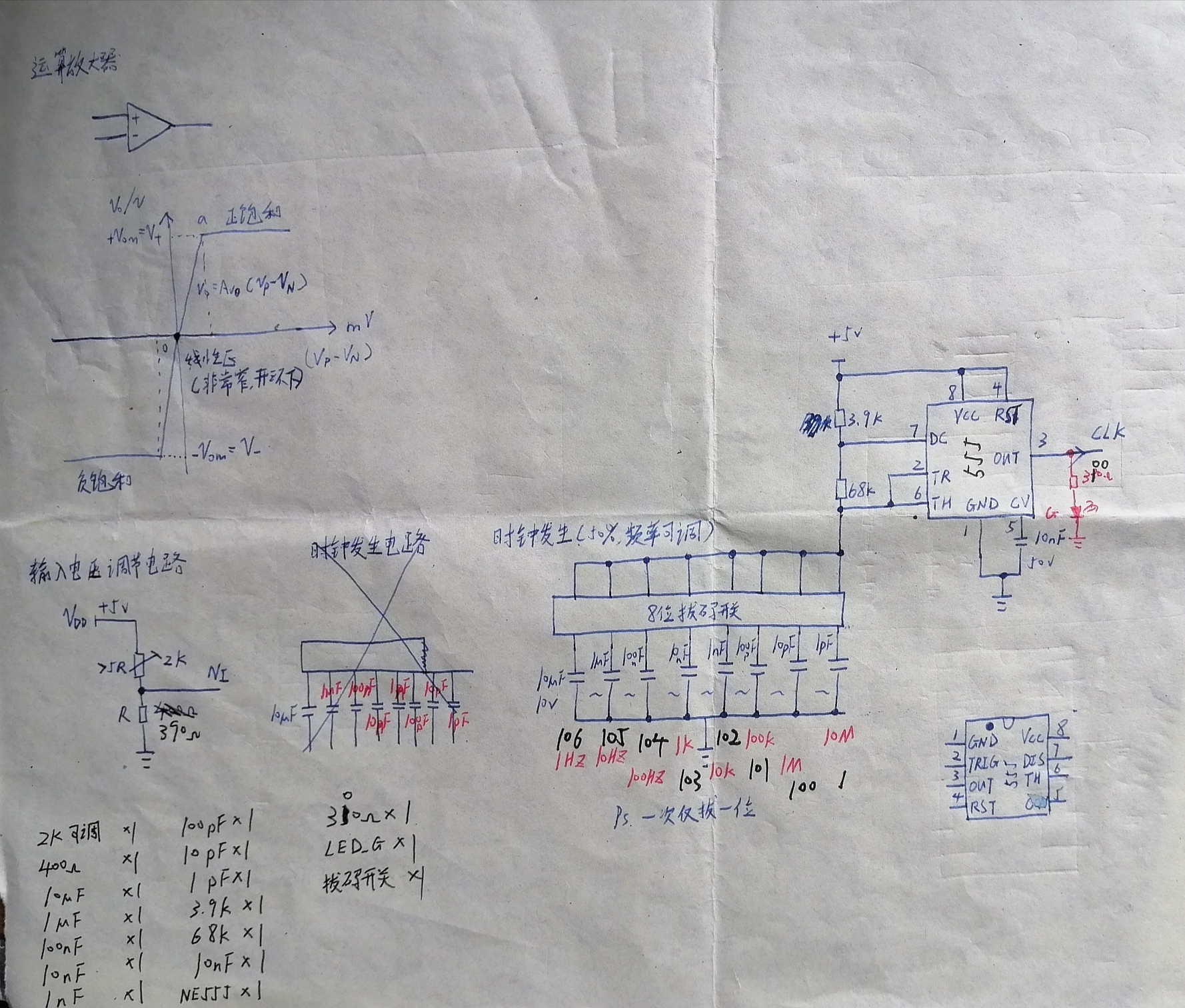

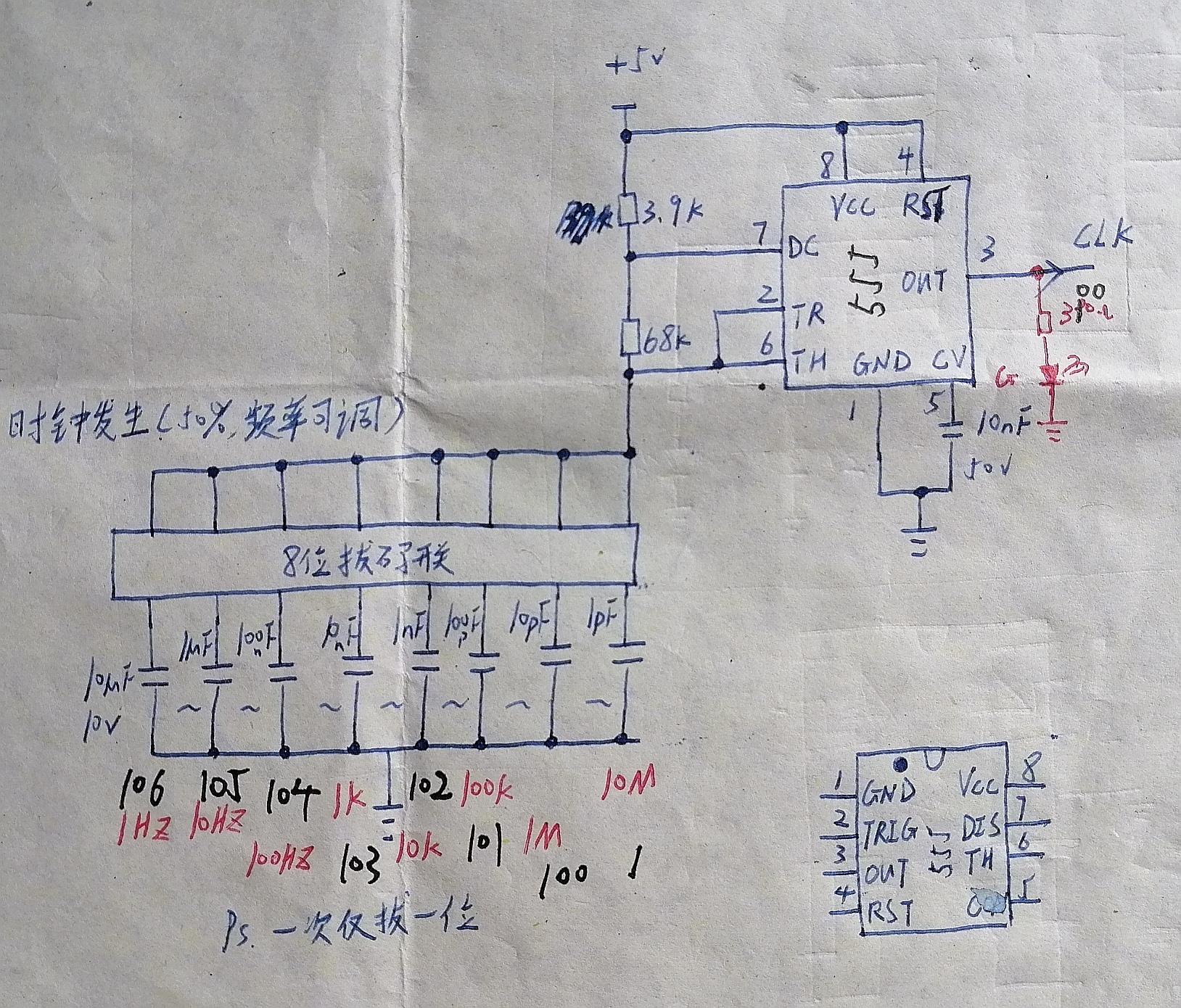

555定时器工作在多谐振荡器模式,通过拨码开关选择不同的电容来产生不同频率的方波。

基于555定时器的时钟发生器原理图

------------------------------------------------------------------------------------------------------------------------------------------------

------------------------------------------------------------数模转换器部分--------------------------------------------------------------------

比较器:左侧的电阻分压网络为右侧的四个比较器的反相输入端提供阶梯状的参考电压(4V、3V、2V、1V),可调电阻模拟输入到四个比较器同相端的模拟电压(0~~5V)。比较器通过比较同相输入端与反相输入端电压的大小,输出0V(Vp<Vn)或5V(Vp>Vn)给后面的D锁存器。

运放的特性图

四路D锁存器:在时钟的每一个上升沿,将四个运放输出的电压(比较结果)存储起来并交给后面的编码器。

优先级编码器:对来自锁存器的四个比较结果进行编码,并输出给计算机处理(如果有计算机的话)。

-----------------------------------------------------------------------------------------------------------------------------------------------

集成电路简介

MCP6004:微芯公司生产的低功耗1MHz带宽的4路运算放大器,本项目的运算放大器均工作在饱和区。

MCP6004实物图

MCP6004引脚定义

CD4042B:CMOS四路D锁存器,在本项目中使用上升沿触发,时钟由555定时器提供,用于保存MCP6004输出的4位数据。

CD4042B实物图

CD4042B引脚定义

CD4042B真值表

CD4532B: CMOS的8位优先级编码器,用于对CD4042B锁存的数据进行编码。

CD4532B实物图

CD4532B引脚定义

CD4532B真值表

测试

------------------------------------------------------------时钟发生器部分--------------------------------------------------------------------

此555时钟发生电路,实际测试可以产生1Hz、10Hz、100Hz、1KHz、10KHz、100KHz、0.4MHz、0.7MHz的方波信号。实测中,产生的0.4MHz和0.7MHz与设计的1MHz、10MHz存在较大的误差,可能是电容的问题(这两个频率对应所使用的是贴片电容)。

时钟发生器(正面)

时钟发生器(反面)

实测产生的最大频率的波形(Vcc=5V下,Vpp=4.7V)

------------------------------------------------------------------------------------------------------------------------------------------------

------------------------------------------------------------数模转换器部分--------------------------------------------------------------------

在时钟为400KHz下,此并行比较型A/D可以正常工作;使用700KHz的时钟会导致转换故障。

主要参数:A/D分辨率为3位(严格来说只有2位,可以在不改变架构的情况下通过增加4个比较器拓增至3位)

采样率为400KSPS~~700KSPS。

功耗:20mA@5V = 100mW (包含时钟发生器部分)

当输入电压为2.5V时,输出的情况(可以看出LED指示“101”,正好是对“1100”编码的结果)

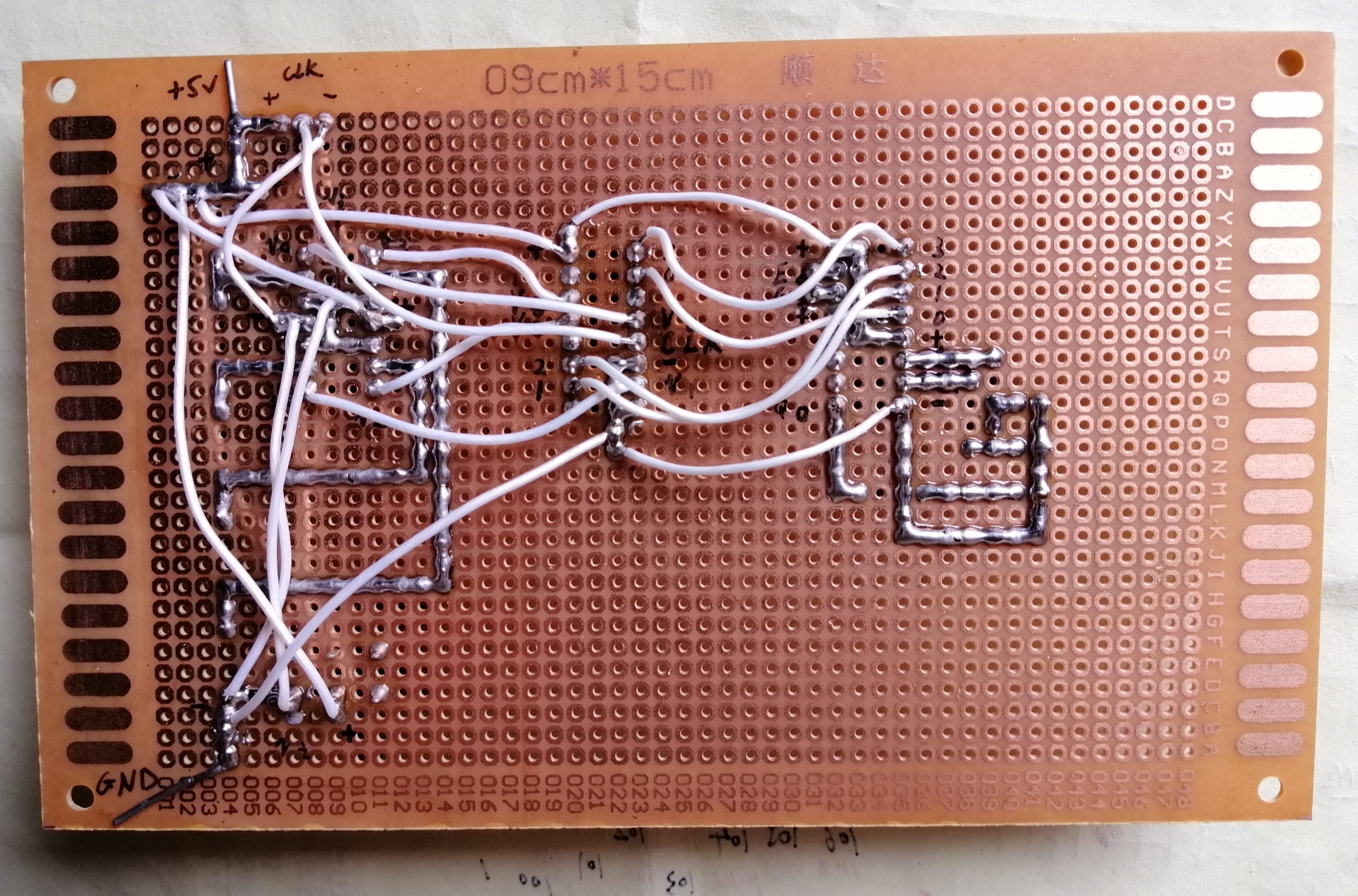

正面(1)

正面(2)

反面

-----------------------------------------------------------------------------------------------------------------------------------------------

声明

此教程未经DLHC允许,禁止转载。所有引用均注明了出处。DLHC保留所有权利。

由于本人学识有限且整理较为仓促,如有错误或不妥,请指正。

如有问题,请在评论区留言。