微机系统知识点整理(1)

写在前面

教材:微型计算机原理与汇编语言程序设计第二版(科学出版社),微型计算机原理与接口技术第二版(科学出版社),汇编语言实验指导书(校内教材)。教材主要以Intel8086CPU和Pentium系列处理器为例介绍。

微机系统对我来说太难了,之后继续学硬件/计算机底层的概率极低,不打算在此花费太长时间,于是决定每天花1h来学微机。更新随机,随时会咕咕咕。这里只是记录一下教学指导中重要的知识点,没写的不代表不重要。其他关于理解方面的会放在其他随笔中。大概率也会咕掉OTZ

欢迎捉虫!

上册:微型计算机原理与汇编语言程序设计

第1章 绪论

1.CISC和RISC技术的主要特点。

| 指令系统 | 内存访问 | 电路结构 | 典型处理器 | |

|---|---|---|---|---|

| RISC | 简单,指令短、等长 | 专有指令、简单 | 简单,设计周期较短,面积小,功耗低 | IBM的PowerPC和PowerPC2,ARM微处理器,Sun的SPARC,HP的PA-RISC 7000和MIPS的R系列 |

| CISC | 复杂,指令长、不等长 | 很多指令、复杂 | 复杂,设计周期长,技术更新难,功能强 | Intel x86、AMD、TI、Cyrix、VIA |

第2章 16位微处理器Intel8086

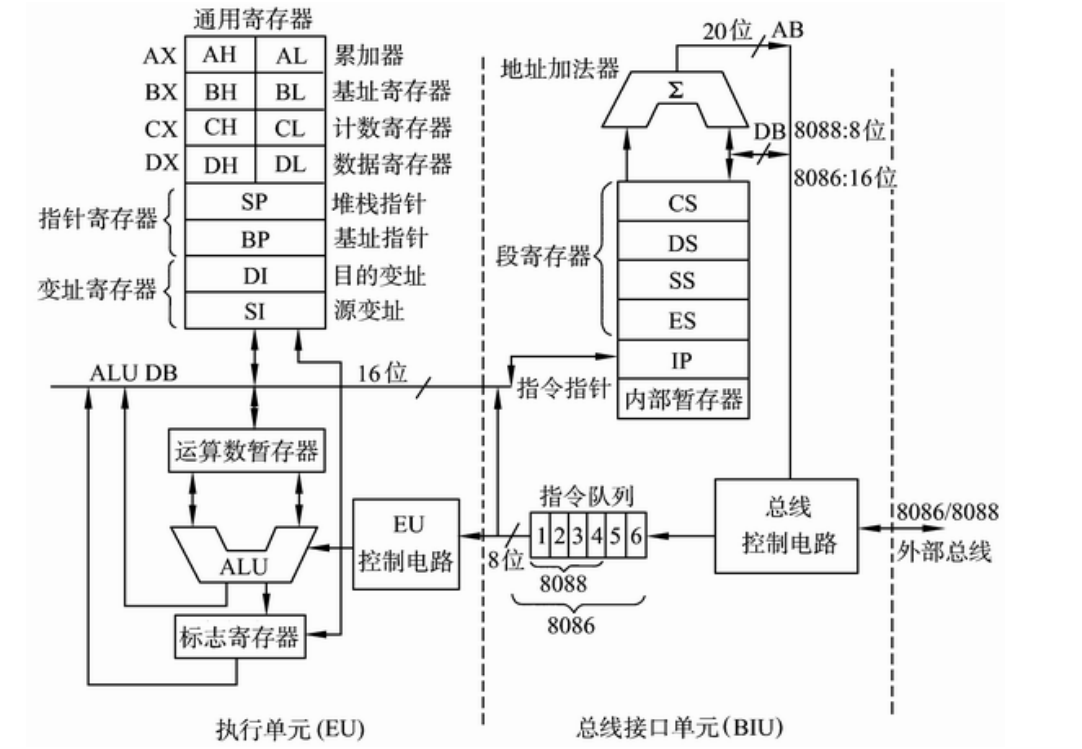

2.8086的内部逻辑结构——BIU和EU的组成与功能;

- BIU:Bus Interface Unit,总线接口单元,用来完成所有总线操作

- 组成:

1.4个16位指令指针

2.16位指令指针

3.6字节指令队列

4.总线控制逻辑

5.20位地址加法器 - 功能:

1)取地址

2)形成物理地址

3)传送数据,实现CPU与内存、I/O端口间的数据传送

- 组成:

指令预取策略:当指令队列出现2个以上空字节(8086)时,自动按CS:IP组成20位物理地址,到存储器去取指令,一次取两个字节。

- EU:Execution Unit,执行单元,即执行各项运算的单元。

- 组成:

1.16位ALU

2.16位标志寄存器

3.EU控制电路

4.8个16位通用寄存器 - 功能:

1)从BIU指令队列读取指令

2)由EU控制电路译码分析

3)在EU中计算操作数的16位偏移地址送BIU,由BIU形成20位物理地址

4)将取来的操作数送ALU进行指令运算

5)结果送寄存器或BIU放到内存中

6)本次操作状态放到标志寄存器中

- 组成:

8086微处理器的构成(加上与8088的比较)

可以看出,8086CPU与8088CPU的EU相同,BIU有差别:

- 外部DB

- 8086有16位

- 8088只有8位

- 指令队列

- 8086为6个字节

- 8088为4个字节

*DB:Data Bus,数据总线

8086的结构特点

- 由BIU、EU两个独立单元组成

- 取指和执行重叠

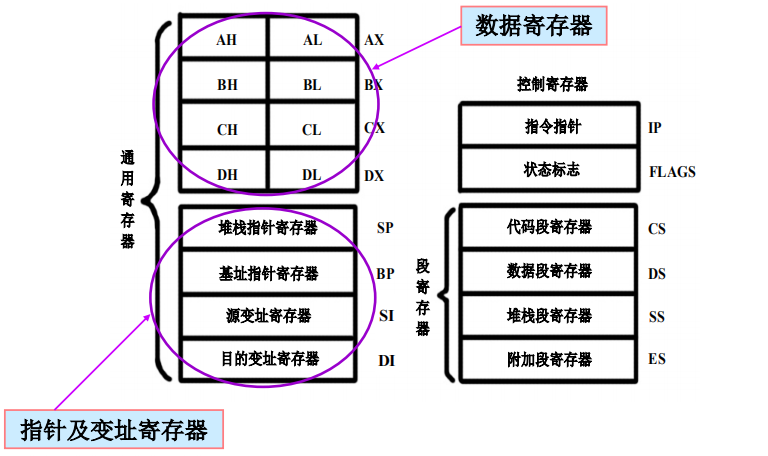

3.8086微处理器的寄存器及功能;

8086CPU有14个16位寄存器,包括:

- 4个数据寄存器

- 4个指针及变址寄存器

- 2个控制寄存器

- 4个段寄存器

数据寄存器与指针及变址寄存器都称为通用寄存器

功能:

- 数据寄存器:存放操作数据及中间结果

- AX 累加器,Accumulator Register

- BX 基址寄存器,Base Register

- CX 计数器,Counter

- DX 数据寄存器,Data Register

可高低字节分别寻址,H为高字节,L为低字节 可存16位地址 有专门功能

- 指针及变址寄存器:存放逻辑地址的偏移量,是20位物理地址的组成部分

- SP 堆栈指针,Stack Pointer,指示堆栈段中栈顶位置,用于数据进出栈的位置指向

- BP 基址指针,Base Pointer,指示堆栈段中一个数据区的基址位置,用于访问堆栈段的某个数据

- SI 源变址寄存器,Source Index,源串指针,指示在数据段中一个源串操作数的位置

- DI 目的变址寄存器,Destination Index,目的串指针,指示在附加段中一个目的串操作数的位置

源串操作数:被操作的数据串

目的串操作数:操作后的被存放的数据串

SI、DI用于数据传操作,且隐含使用。 - 段寄存器

- CS 代码段寄存器,Code Segment,存放当前执行程序的段起始地址

- SS 堆栈段寄存器,Stack Segment,存放当前堆栈段的段起始地址

- DS 数据段寄存器,Data Segment,存放当前数据段的段起始地址

- ES 附加段寄存器,Extra Segment,存放当前附加段的段起始地址

8086中,默认段起始地址是16的倍数。即20位物理地址的低四位都是0。

附加段:有时程序需要从一个数据段取出,存放到另外一个段,这时需要同时指示两个段,即一个数据段,一个附加段。 - 控制寄存器:

- IP 指令指针,Instruction Pointer,存放下一次要取出的指令的偏移地址

- Flag 标志寄存器,存放ALU状态和对CPU的控制状态。16位定义9位,分为6位状态标志和3位控制标志

IP不能被程序直接存取,有BIU来修改,类似PC。下一条指令的实际地址: CS:IP

4.引脚功能:INTR、NMI、RD、WR、MN/MX、BHE、M/IO;

- INTR :可屏蔽中断请求信号,高电平有效

- NMI :非屏蔽中断请求信号,上升沿有效

- RD :读选通,低电平时有效

- WR :写信号,低电平时有效

- MN/MX :最小/最大模式,接+5V最小模式,接地最大模式

- M/IO :存储器、输入输出控制,高电平时为存储器,低电平时为输入输出

- BHE :与A0的代码组合对应相应的操作

| BHE | A0 | 操作 | 所用数据引脚 |

|---|---|---|---|

| 0 | 0 | 从偶地址单元开始读/写一个字 | AD15~AD0 |

| 0 | 1 | 从奇地址单元或端口读/写一个字 | AD15~AD8 |

| 1 | 0 | 从偶地址单元或端口读/写一个字 | AD7~AD0 |

| 1 | 1 | 无效 | -- |

当连续两个周期BHE与A0值为{0,1}和{1,0}时,从奇地址开始读/写一个字(在第一个总线周期将第八位数据送到AD15AD8,下一个周期将高八位数据送到AD7AD0),所用的数据引脚为AD15~AD0.

5.两种工作(组成)模式;

- 最小模式:单机系统,只有一个8086CPU,所有控制信号由该CPU产生。系统中的控制电路可减到最小。

- 最大模式:多机系统,有两个以上CPU,一个主8086CPU,其他为协处理器(如8087/8089),控制信号由总线控制器8288产生。

6.8086逻辑地址、物理地址及转换。

物理地址:信息在存储器中实际存放的地址。地址通过地址线给出

逻辑地址:编程中使用的地址

逻辑地址的格式:

段地址:段内偏移量

物理地址的计算:

物理地址 = 段寄存器 * 16 + 段内偏移量

(20位) (16位)(10H)(16位)

段地址:决定该段第一个字节的位置

段内偏移量:该存储单元相对于该段起点字节的距离。指令中称为有效地址EA

同一个物理地址可以用不同的逻辑地址来表示

7.8086中断向量表。

8086可以处理256种不同类型的终端,每一种终端都规定一个唯一的中断类型编码。CPU根据中断类型编码来识别中断源。

中断分类:

- 外部中断:由外部中断源引起的终端,INTR,NMI。

- 内部中断:由内部软件中断指令产生,或者在某些特定情况下,由CPU本身触发产生。

- 软件中断:中断指令INT n,一处中断指令INTO,断电中断指令INT3。

特点:- 不受IF控制

- 不读取中断向量

- 优先权高

- 软件陷阱:除法错误中断,单步中断

- 软件中断:中断指令INT n,一处中断指令INTO,断电中断指令INT3。

中断向量:中断服务程序的起始地址。一个中断向量占4个存储单元。

中断向量地址 = 中断类型码 * 4

中断优先级:(高)除法错误 - 软件中断 - NMI - INTR - 单步(低)

END

浙公网安备 33010602011771号

浙公网安备 33010602011771号