DSP_Analog to Digital Converter

Ref:TMS320x2833x Analog-to-Digital Converter (ADC) Module

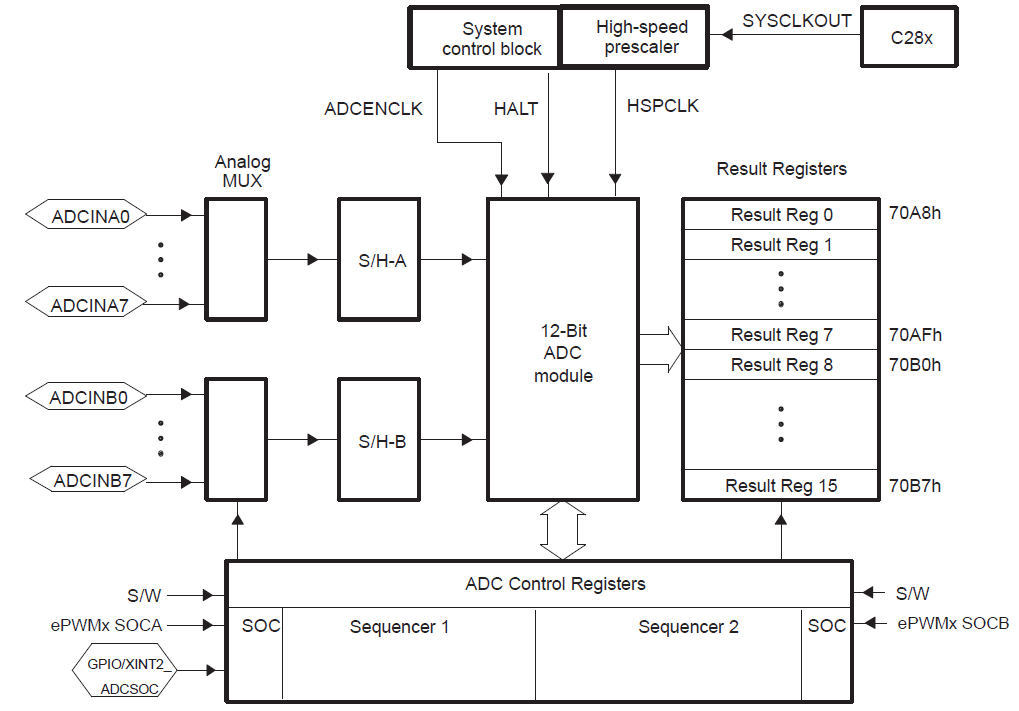

Functions of the ADC module include:

- 內建取樣與保持電路(S / H),兩組12位元的ADC轉換模組。

- 類比輸入:0~3V

- ADC時鐘快速轉換時間運行在12.5 MHz,或6.25 MSPS

- 16個多工類比輸入訊號(ADCIN0-ADCIN15)

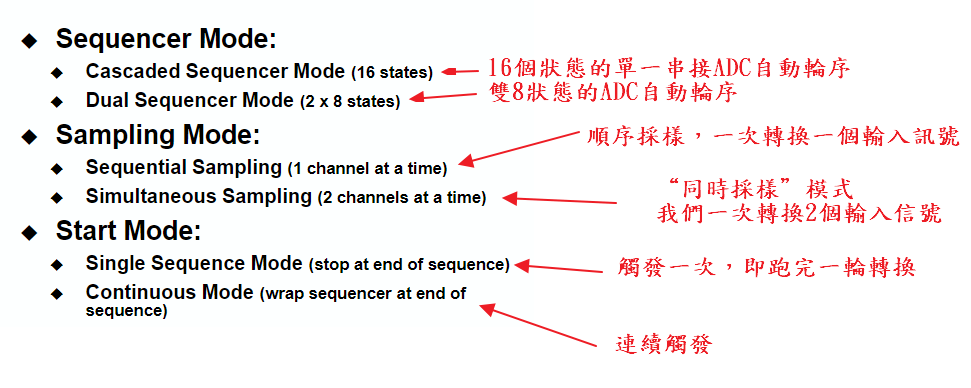

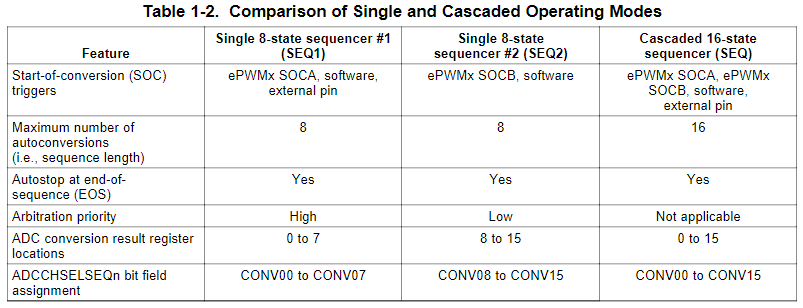

- SEQ(倫循順序)可以作為兩個獨立的8狀態定序器或作為倫循順序來操作或一個大的16倫循順序狀態來操作

- 輸入模擬電壓的數字值由下式導出

- 靈活的中斷控制允許每個序列結束(EOS)或每個其他EOS的中斷請求

- ePWM觸發器可以在雙音序器模式下獨立運行

- 作為轉換開始(SOC)序列的源的多個觸發器

- 軟體觸發(SOC_SEQn位元設定)

- ePWM 1-6

- GPIO XINT2

Block Diagram of the ADC Module

ADC Operating Modes

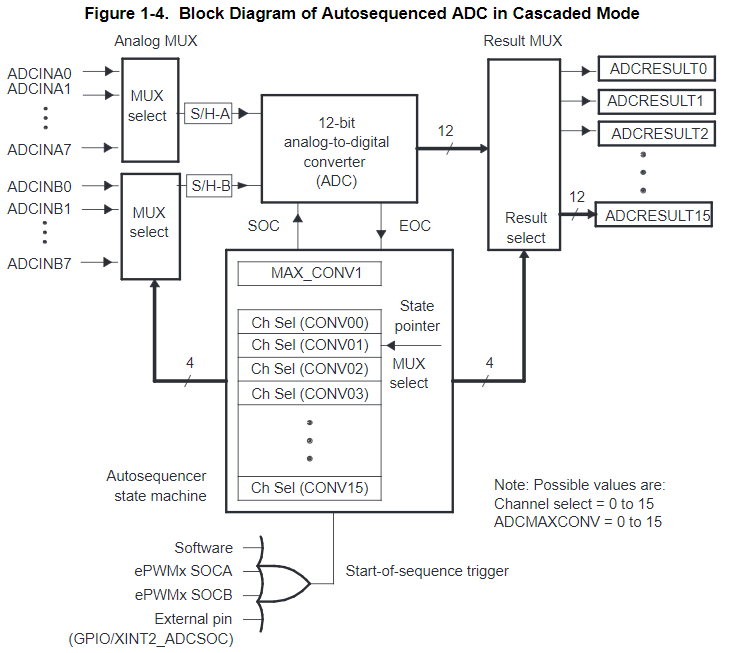

ADC In Cascaded Mode (16個狀態的單一串接自動輪序方塊結構圖)

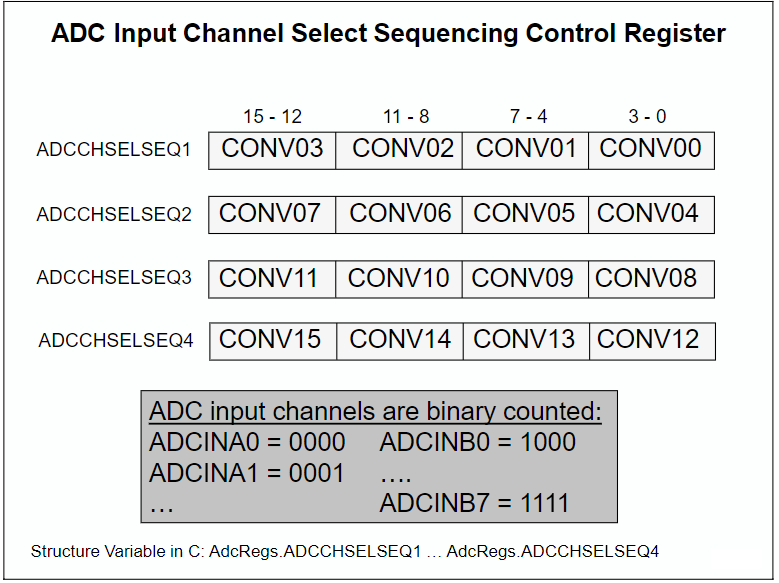

CONV.xx由4位元來定義輸入接腳,來選擇ADCINXX被輸入取樣保持和緩衝

最高位元選擇ADCINA or ADCINB 0:A 1:B

後三位元選擇ADCINX0-7

Ex:

- CONVxx=0101=> ADCINA5

- CONVxx=1011=> ADCINB3

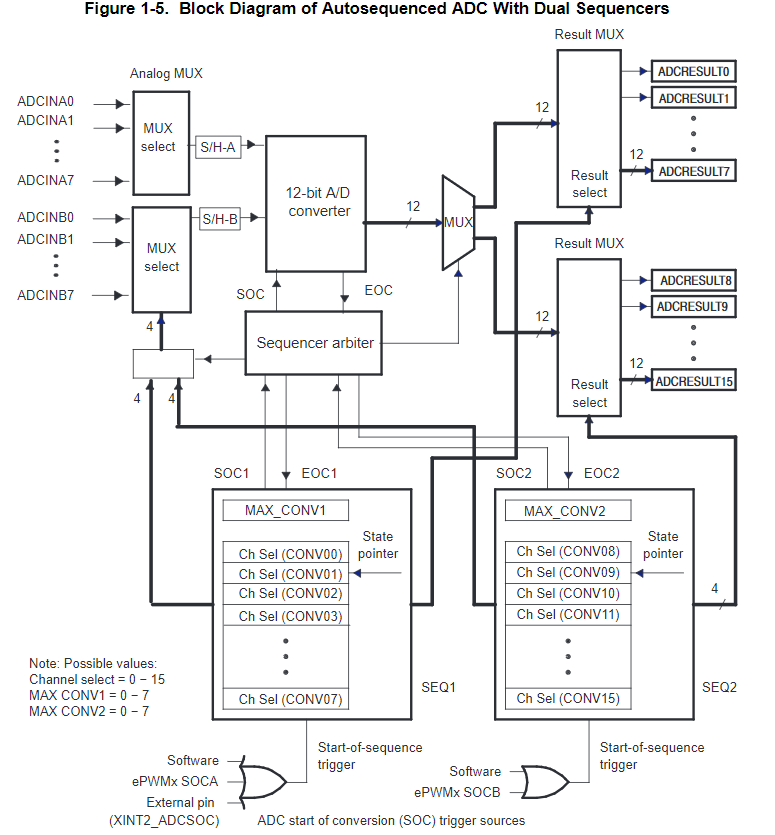

雙8狀態的ADC自動輪序方塊結構圖

在此模式下,CONVxx的最高為元失去意義,只有三位元去選擇ADCINA0-7 and ADCINB0-7

在此雙輪序模式中,SEQ1有最高的耶先續,例如SEQ1 and SEQ2同時提出要求,會先執行SEQ1

若處理SEQ1輪序期間,SEQ1 & SEQ2又提出要求,則ADC依然會選擇SEQ1做處理

輪序器運作於8狀態與16狀態的些微差異表

可以注意到只有SEQ1右外接腳的SOC

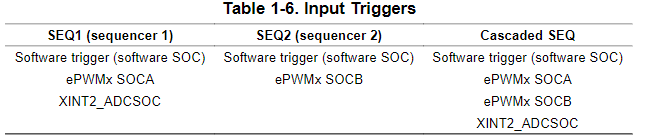

Input Trigger Description(輸入觸發描述)

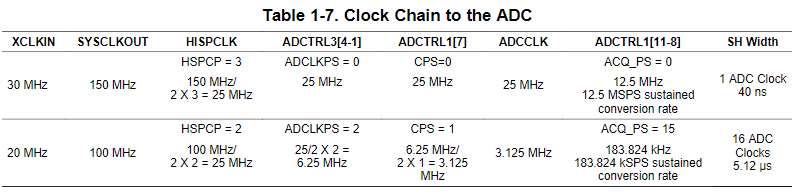

ADC Clock Prescaler (ADC時鐘分頻器)

ADC-module Clock and Sample Rate

ADC模塊具有多個預分頻器級以產生任何所需的ADC工作時鐘速度。

ACQ_PS為採樣窗的大小

以25MHZ為ADCCLK為例,ACQ_PS=0的話 採樣視窗為0+1=1個(只有含HIGH的視窗),故採樣率的部分要25MHZ/1+1=12.5MHZ

Example 1-1.Simultaneous Sampling Dual Sequencer Mode Example(同時採樣雙序列器模式示例)

Example initialization: AdcRegs.ADCTRL3.bit.SMODE_SEL = 0x1; // 設置同步採樣MODE AdcRegs.ADCMAXCONV.all = 0x0033; // 每個排序器4個轉換(共八個) AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0; // Setup conv from ADCINA0 & ADCINB0 AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x1; // Setup conv from ADCINA1 & ADCINB1 AdcRegs.ADCCHSELSEQ1.bit.CONV02 = 0x2; // Setup conv from ADCINA2 & ADCINB2 AdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0x3; // Setup conv from ADCINA3 & ADCINB3 AdcRegs.ADCCHSELSEQ3.bit.CONV08 = 0x4; // Setup conv from ADCINA4 & ADCINB4 AdcRegs.ADCCHSELSEQ3.bit.CONV09 = 0x5; // Setup conv from ADCINA5 & ADCINB5 AdcRegs.ADCCHSELSEQ3.bit.CONV10 = 0x6; // Setup conv from ADCINA6 & ADCINB6 AdcRegs.ADCCHSELSEQ3.bit.CONV11 = 0x7; // Setup conv from ADCINA7 & ADCINB7 If SEQ1 and SEQ2 were both executed, the results would go to the following RESULT registers: ADCINA0 -> ADCRESULT0 ADCINB0 -> ADCRESULT1 ADCINA1 -> ADCRESULT2 ADCINB1 -> ADCRESULT3 ADCINA2 -> ADCRESULT4 ADCINB2 -> ADCRESULT5 ADCINA3 -> ADCRESULT6 ADCINB3 -> ADCRESULT7 ADCINA4 -> ADCRESULT8 ADCINB4 -> ADCRESULT9 ADCINA5 -> ADCRESULT10 ADCINB5 -> ADCRESULT11 ADCINA6 -> ADCRESULT12 ADCINB6 -> ADCRESULT13 ADCINA7 -> ADCRESULT14 ADCINB7 -> ADCRESULT15

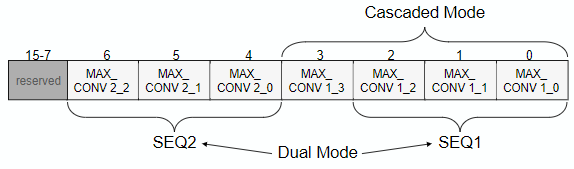

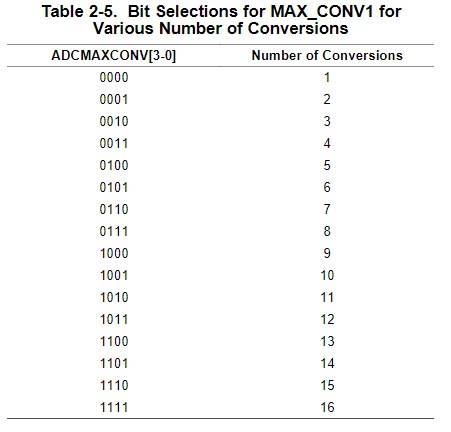

ADC MAXCONV Register(ADCMAXCONV小補充)

- BIT定義每個觸發器的轉換次數(二進制+1)

- 每個排序器從“初始狀態”開始並順序前進

- 除非軟件提早重置,否則每個都會以“結束狀態”進行換行

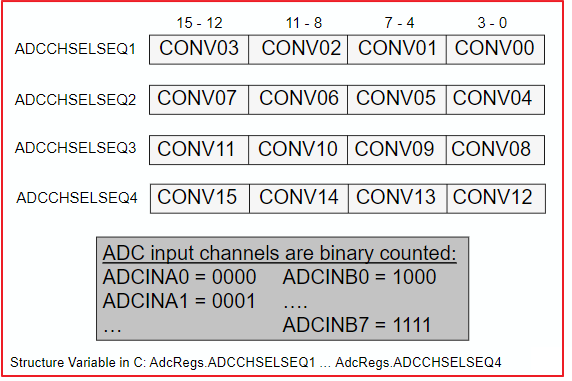

ADC Input Channel Select Registers(ADCCHSELSEQn 小補充)

- ADC輸入通道選擇排序控制寄存器

Example 1-2. Simultaneous Sampling Cascaded Sequencer Mode Example(級聯排序列同步採樣模式示例)

AdcRegs.ADCTRL3.bit.SMODE_SEL = 0x1; // Setup simultaneous sampling mode 同步採樣模式 AdcRegs.ADCTRL1.bit.SEQ_CASC = 0x1; // Setup cascaded sequencer mode 設置級聯排序器模式 AdcRegs.ADCMAXCONV.all = 0x0007; // 8 double conv's (16 total) 每個排序器8個轉換(共16個) AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0; // Setup conv from ADCINA0 & ADCINB0 AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x1; // Setup conv from ADCINA1 & ADCINB1 AdcRegs.ADCCHSELSEQ1.bit.CONV02 = 0x2; // Setup conv from ADCINA2 & ADCINB2 AdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0x3; // Setup conv from ADCINA3 & ADCINB3 AdcRegs.ADCCHSELSEQ2.bit.CONV04 = 0x4; // Setup conv from ADCINA4 & ADCINB4 AdcRegs.ADCCHSELSEQ2.bit.CONV05 = 0x5; // Setup conv from ADCINA5 & ADCINB5 AdcRegs.ADCCHSELSEQ2.bit.CONV06 = 0x6; // Setup conv from ADCINA6 & ADCINB6 AdcRegs.ADCCHSELSEQ2.bit.CONV07 = 0x7; // Setup conv from ADCINA7 & ADCINB7 If the cascaded SEQ was executed, the results would go to the following ADCRESULT registers: ADCINA0 -> ADCRESULT0 ADCINB0 -> ADCRESULT1 ADCINA1 -> ADCRESULT2 ADCINB1 -> ADCRESULT3 ADCINA2 -> ADCRESULT4 ADCINB2 -> ADCRESULT5 ADCINA3 -> ADCRESULT6 ADCINB3 -> ADCRESULT7 ADCINA4 -> ADCRESULT8 ADCINB4 -> ADCRESULT9 ADCINA5 -> ADCRESULT10 ADCINB5 -> ADCRESULT11 ADCINA6 -> ADCRESULT12 ADCINB6 -> ADCRESULT13 ADCINA7 -> ADCRESULT14 ADCINB7 -> ADCRESULT15

Example 1-3. Conversion in Dual-Sequencer Mode Using SEQ1 (使用SEQ1的雙輪序模式之轉換)

假如要用SEQ1做7個輪序轉換(例如在自動輪序期間,通道2、3、2、3、6、7、12需要被轉換),則ADCMAXCONV.all=0x006 (6+1=7)

同時ADCCHSELSEQn 需要設計為下表的值

-

CONV00 = 2

-

CONV01 = 3

-

CONV02 = 2

-

CONV03 = 3

-

CONV04 = 6

-

CONV05 = 7

-

CONV06 = 12

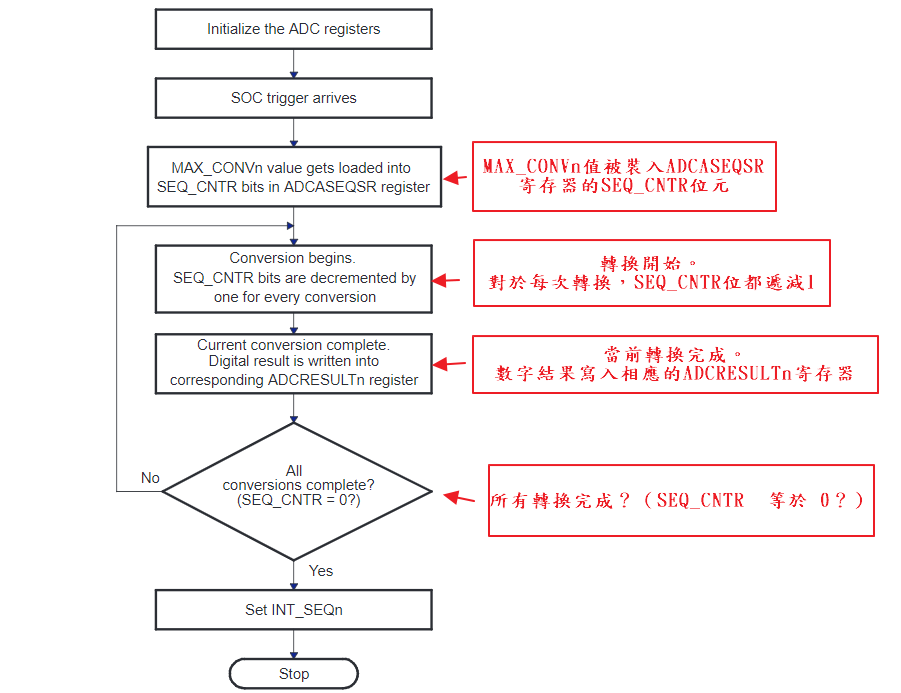

Flow Chart for Uninterrupted Autosequenced Mode(連續自動排序模式程式運作流程圖)

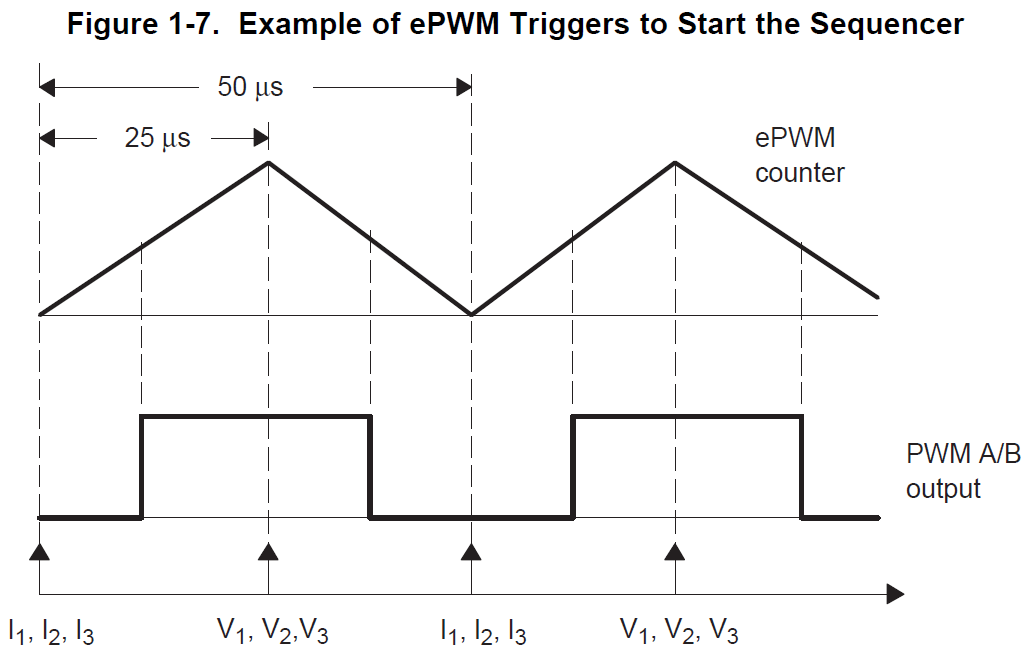

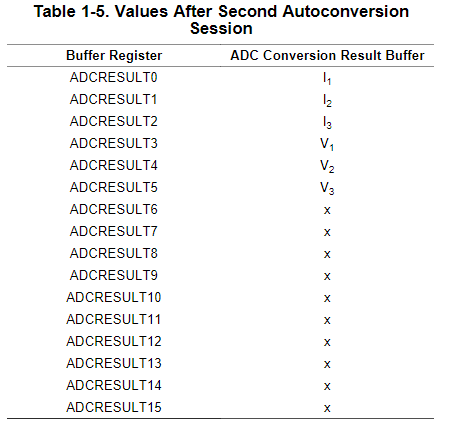

Example 1-4. Sequencer Start/Stop Operation(排序器啟動/停止操作)

Configuration Requirements:

- ePWMtriggers the ADC

-

Three auto conversions (V1, V2, V3) off trigger 1 (CTR = 0)

-

Three auto conversions (I1, I2, I3) off trigger 2 (CTR = PRD) (共兩個觸發條件)

- ADC採用級聯序列發生器和順序採樣模式

這樣的控制給出了數字電機控制的三相控制系統的典型示例

MAX_CONV1設置為2,通道選擇排序控制寄存器設置為:

- 一旦復位並初始化,SEQ1等待觸發器

- 第一次觸發,執行三次轉換:CONV00(V1),CONV01(V2),CONV02(V3)

- SEQ1等待第二個觸發器

- 第二次觸發,執行三次轉換:CONV03(I1),CONV04(I2),CONV05(I3)

- 第二個序列結束時,ADC結果寄存器具有以下值:

![]()

- SEQ1在當前狀態下等待另一個觸發器

- ISR讀取結果並重置SEQ1

觸發信號1&2可能是由EVA發出的OSC訊號、外部街腳端、軟體設定觸發,這種相同的觸發來源在這個例子中可能發生兩次來滿足雙觸發的需求。

ADC Converter Registers

ADC Control Register

Bit 14(“RESET”)可用於將整個ADC單元復位到其初始狀態

位6(“CONT_RUN”)定義自動序列發生器是從序列末尾(= 0)開始並等待另一個觸發器,或者序列是否應立即重新開始(= 1)。(是否連續模式)

位5(“SEQ_OVRD”)為連續模式定義了兩個不同的選項。在我們的實驗室中,我們不會使用這種模式,所以它是'don't care'。

位4(“SEQ_CASC”)是序列/級聯位。它將定序器模式定義為具有16個狀態(SEQCASC = 1)的狀態機,或者作為兩個獨立的狀態機運行,每個狀態機有8個狀態(SEQ_CASC = 0)。

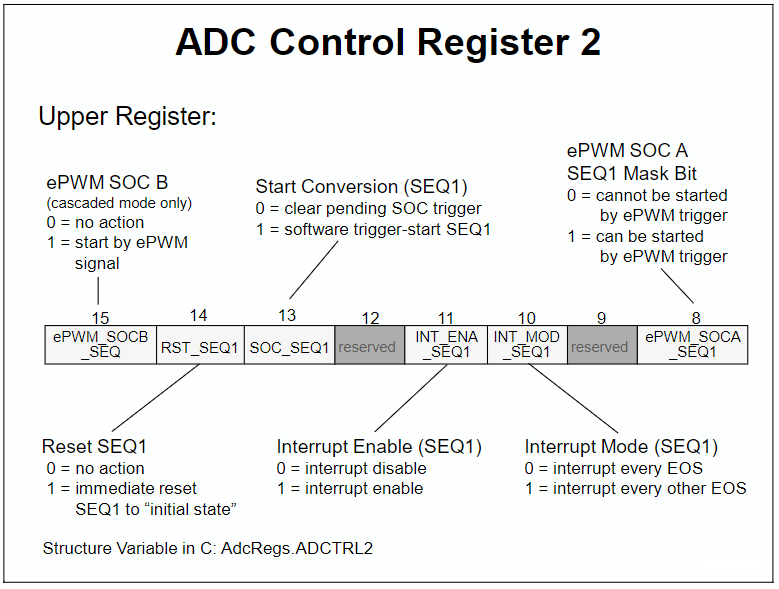

位15(“ePWM_SOCB_SEQ”)允許級聯音序器由ePWM SOCB信號啟動。該位在“雙音序器模式”中不起作用(請參見位0)

位14(“RST_SEQ1”),我們可以將SEQ1的狀態機重置為其初始狀態。這意味著下一個觸發器將開始對CONV00中定義的通道進行新的轉換

位13(“SOC_SEQ1”)設置為1,我們在軟件控制下立即開始轉換

位11(“INT_ENA_SEQ1”)和10(“INT_MOD_SEQ1”)定義了SEQ1的中斷模式。我們可以指定每個“序列結束”(EOS)還是每隔一個(EOS)都有一個中斷請求

位8(“ePWM_SOCA_SEQ1”)是允許ePWM信號作為“SOCA”用作轉換觸發器的Mask bit。

ADCTRL2的低字節與其上半部分類似:它控制序列發生器SEQ2。

位7使能ADC自動轉換序列,該序列由來自GPIO端口A引腳(GPIO31-0)的信號啟動,該引腳配置為GPIOXINT2SEL寄存器中的XINT2。

位6到位0:ADCTRL2的其餘部分與寄存器上半部分的位14 ... 8相似。但是它們用於初始化SEQ2的操作模式

如果我們不使用排序器雙排的話,因為我們處於“級聯模式”,這些位元可不必在意。

位0選擇採樣模式為順序或同時。回想一下,在同時模式下,兩個模擬輸入信號並行轉換 可參考EX1-1 or EX1-2。

Example:假設您想要並行轉換ADCINA4和ADCINB4的信號。你所要做的就是初始化:

SMODE_SEL = 1 // simultaneous sampling 同時採樣 MAXCONV = 0 // 1 conversion; actually 2, because of SMODE_SEL = 1 1個轉換即可;實際上是2,因為SMODE_SEL = 1 CONV00 = 4 // channel number for ADCINA4

轉換完成後,寄存器RESULT0將包含ADCINA4的值,並將RESULT1寄存器中ADCINB4的值

位4-1用於將FCLK初始化為ADC模塊的基本時鐘

位5是設備內部模擬電路的主電源開關。通過設置此位,我們可以啟動ADC,除了帶隙和參考電路。

位7-6控制內部參考電壓系統的ADC的電壓階細隙(Bandgap)和參考電壓掉電序列。

ADC MAXCONV Register

"MAXCONV“定義了自動排序器的轉換階段的數量。在有效的觸發信號後,自動排序器將自動轉換預定義的通道數量。

MAXCONV = 4 // 表示5次轉換,輸入通道編號在寄存器ADCCHSELSEQ1和ADCCHSELSEQ2的位域CONV00至CONV04中編碼

如果我們使用“雙音序器模式”,寄存器MAXCONV的解釋稍有改變。在此模式下,位0至2用於指定序列發生器SEQ1中的轉換次數,而位4至6用於SEQ2。回想一下,在這種模式下,每個音序器的最大轉換次數為8次,因此MAXCONV中的限制為3個位。

自動排序器作為狀態機運行,從初始狀態開始並在每次轉換到下一個狀態後前進。這個原理一直持續到結束狀態或直到我們將狀態機指針重置回初始狀態(ADCTRL2的位14和位6)。如果我們不重置並且狀態機已達到結束狀態,它將自動回到零狀態。

ADC Input Channel Select Registers

四個寄存器組ADCCHSELSEQ1 ... 4用於通過十六個4位組CONV00 ... CONV15指定輸入通道ADCINA0 ... ADCINB7的二進制數

在自動排序器中最多可以使用16個階段。這些階段對應於CONV00到CONV15。我們所要做的就是填寫模擬輸入通道的正確數字

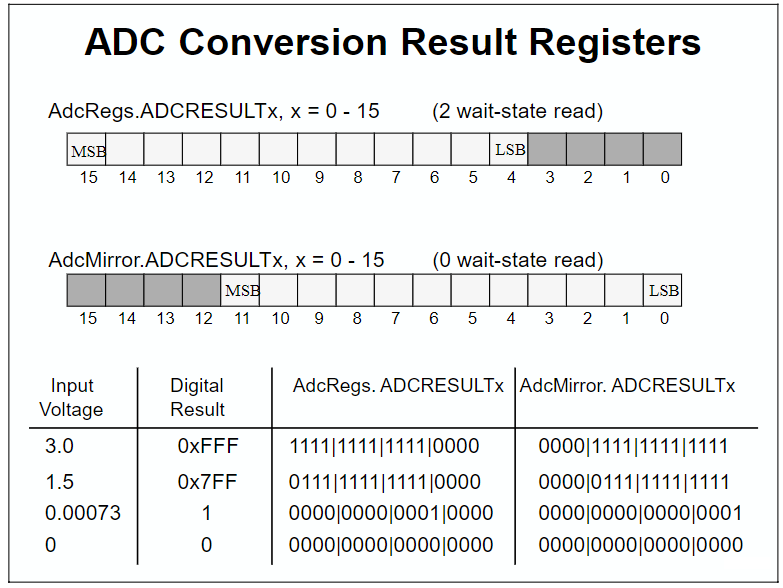

ADC Result Register Set

12位數字結果可用於兩個不同的存儲器部分。

ADCREFSEL Register

要在內部或外部ADC參考電壓之間切換,我們可以使用寄存器ADCREFSEL。

對於我們下一次使用Peripheral Explorer Board的實驗室實驗,我們將保留默認選擇的內部電壓源。

浙公网安备 33010602011771号

浙公网安备 33010602011771号