eMMC颗粒的硬件总线接口介绍

1.eMMC基本概述

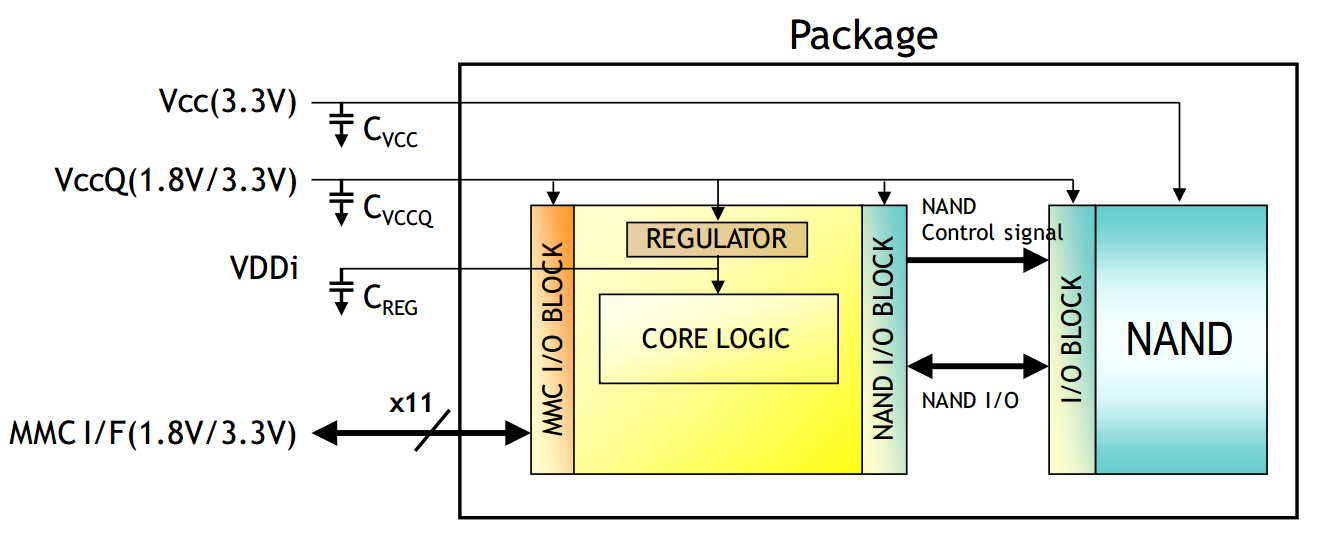

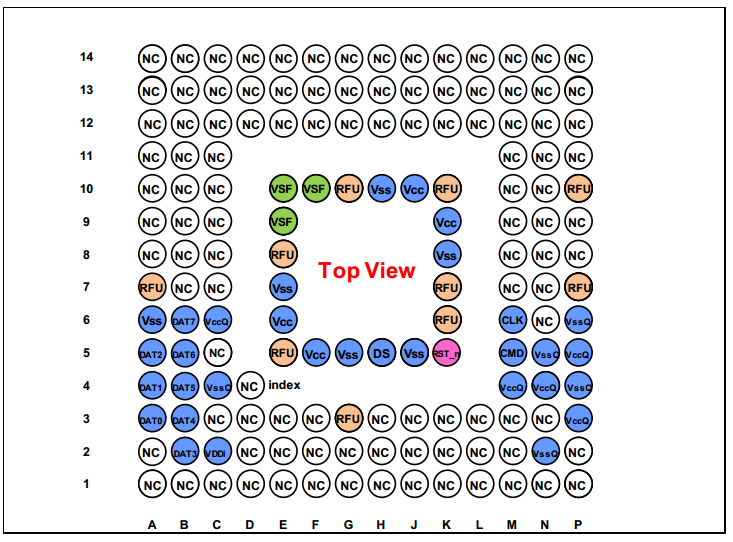

嵌入式多媒体卡(Embedded Multi Media Card)是一种新的存储技术,该架构标准将MMC组件封装在一个IC中,是一种主要针对手机或平板电脑等产品的内嵌式存储器标准规格。 eMMC常见的封装有100,153,169点,并都基于8位并行接口。以东芝的THGBMNG5D1LBAIL 为例,THGBMNG5D1LBAIL是一颗4GB存储容量的e-MMC,NAND存储块和控制单元封装在153 ball BGA,内部结构图见下:

2.eMMC硬件总线接口定义

eMMC颗粒的引脚连接主要分为两组:控制信号和数据信号;

控制信号:

CLK:CLK 信号用于从 Host 端输出时钟信号,进行数据传输的同步和设备运作的驱动。在一个时钟周期内,CMD 和 DAT0-7 信号上都可以支持传输 1 个比特,即 SDR (Single Data Rate) 模式。此外,DAT0-7 信号还支持配置为 DDR (Double Data Rate) 模式,在一个时钟周期内,可以传输 2 个比特。

Host 可以在通讯过程中动态调整时钟信号的频率(注,频率范围需要满足 Spec 的定义)。通过调整时钟频率,可以实现省电或者数据流控(避免 Over-run 或者 Under-run)功能。 在一些场景中,Host 端还可以关闭时钟,例如 eMMC 处于 Busy 状态时,或者接收完数据,进入 Programming State 时。

CMD:CMD信号主要用于 Host 向 eMMC 发送 Command 和 eMMC 向 Host 发送对于的 Response。

DS:DS时钟信号由 eMMC 发送给 Host,频率与 CLK 信号相同,用于 Host 端进行数据接收的同步。在 HS400 模式下配置启用,启用后可以提高数据传输的稳定性,省去总线 tuning 过程。

D7~0:Dx信号主要用于 Host 和 eMMC 之间的数据传输。在 eMMC 上电或者软复位后,只有 DAT0 可以进行数据传输,完成初始化后,可配置 4bit 或者8bit进行数据传输。

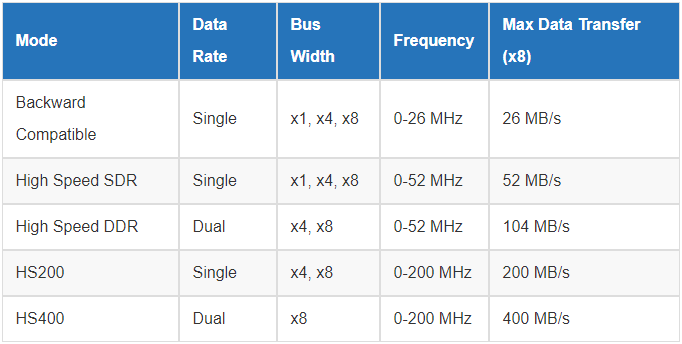

3.eMMC硬件总线接口模式

eMMC 总线上电启动或者 Reset 后,会先进入Backward Compatible Mode。完成 eMMC Devices 初始化后,主机可以通基本配置,让 IC进入其他模式,目前支持以下的几种:

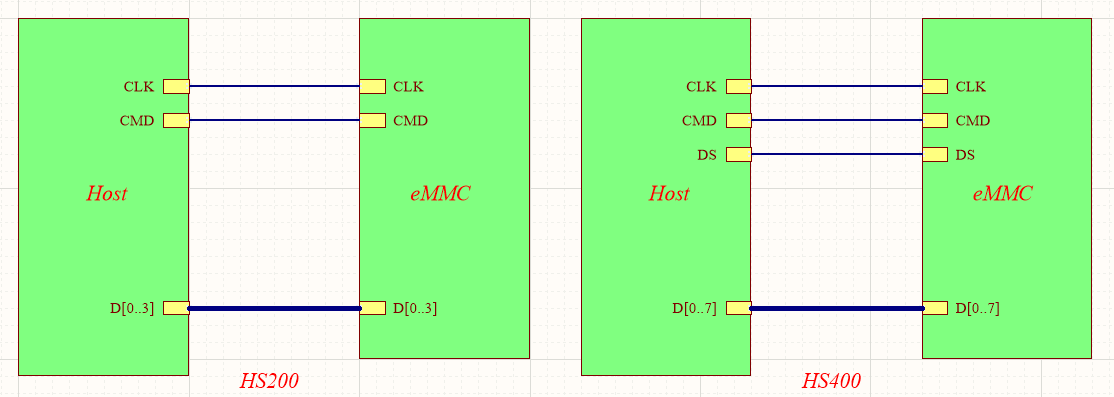

这里重点介绍HS200、HS400模式下总线示意,HS200模式下可配置为4bit、8bit总线传输方式,主要有CLK、CMD、D3~D0;HS400下总线只能配置为8bit,控制线添加DS,连接方式见下:

XC7Z010设计在HS200-4bit模式下,读写时序控制后期待PCB设计完成调试时进一步介绍;

欢迎关注我的微信公众号 NHike

浙公网安备 33010602011771号

浙公网安备 33010602011771号