移位相加乘法器

在硬件设计中,乘法器是非常重要的一个器件,乘法器的种类繁多,常见的有并行乘法器、移位相加乘法器和查找表乘法器,并行乘法器的实现非常简单,在Verilog中只需要通过 * 实现,若要进行有符号的乘法,需使用 系统函数$signed。查找表乘法器实际上是先将乘法的计算结果提前算好,这样就可以在计算时通过查表的方式直接得到结果,一般用于位宽较小的情况。移位相加乘法器是一种耗费较少资源的算法,其思想是将乘法转化为加法和移位运算,缺点是比较耗时,一般用于对性能要求不高的场合。

一、无符号移位相加乘法器

以a=1011和b=1001相乘为例(均为无符号数)

1.b的第0位为1,所以

result = result + b[0] * a<<0;

2.b的第1位为0,result保持不变

result = result + b[1] * a<<1;

3.b的第2位也为0,result保持不变

result = result + b[2] * a<<2;

4.b的第3位为1,则得到最终的计算结果

result = result + b[3] * a<<3;

可以看到, W 位宽的无符号乘法器,需要 W 个周期才能计算完成。

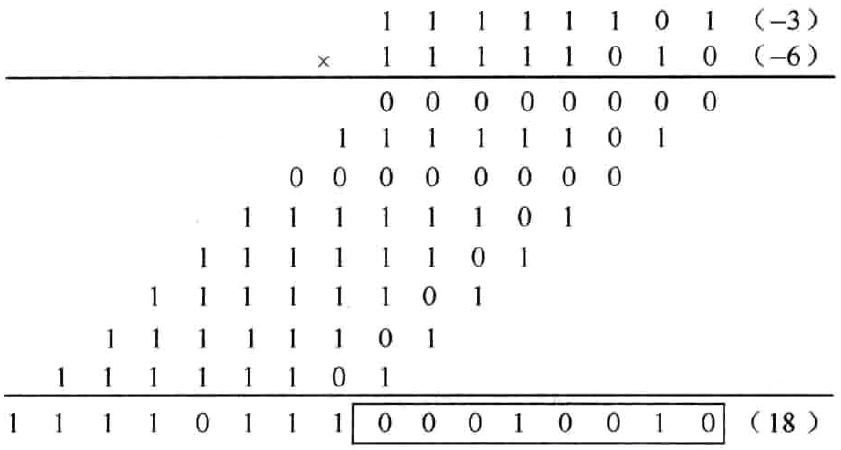

二、有符号移位相加乘法器

以(-3)x(-6)为例,Verilog中有符号数用补码表示,正数的补码是他本身,负数的补码是符号位不变,其他位的反码加1。(-3)的补码是 1101,(-6)的补码是 1010,为了保证结果的正确,首先要将两个数进行符号位扩展,扩展为8bits。有符号位扩展,高位补1,所以(-3)就变为 11111101 ,(-6)就变为 11111010 。然后其计算步骤与无符号移位相加乘法器计算步骤一致。

注意:

1.无论是有符号数相乘还是无符号数相乘,其乘积的位宽必定位a+b;

2.如果被乘数和乘数均为有符号数,那么相乘之前首先要进行符号位扩展,将被乘数和乘数均扩展位a+b位。

3、有符号数乘法的最终结果也是补码形式。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 单线程的Redis速度为什么快?

· SQL Server 2025 AI相关能力初探

· AI编程工具终极对决:字节Trae VS Cursor,谁才是开发者新宠?

· 展开说说关于C#中ORM框架的用法!