电赛总结(二)——AD芯片总结之高速AD9224

一、特性参数

1、12位高速AD

2、高达40MSPS的高速AD芯片

3、噪声小

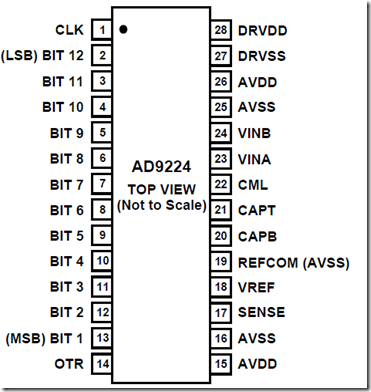

二、芯片管脚图

三、管脚功能说明

| 管脚名称 | 功能 |

| CLK | 参考时钟输入端 |

| BIT12-1 | 数据输出端(1是低位,12是高位) |

| OTR | “1”超出参考电压范围,“0”表示不超出范围 |

| AVDD | 模拟电源输入端 +5V |

| AVSS | 模拟地 |

| SENSE | 参考源选择。“1”选择内部的1.225V参考源,否则使用外接参考源 |

| VREF | 参考源输入端 |

| REFCOM | 参考源地 |

| CAPB | 降噪端 |

| CAPT | 降噪端 |

| CML | Common-Mode Level (Midsupply) |

| VINA | 差分输入正端 |

| VINB | 差分输入负端 |

| DRVSS | 数字地 |

| DRVDD | 数字电源输入端,+5V或者+3V |

本文作者:Blue Mountain

本文链接:https://www.cnblogs.com/BlueMountain-HaggenDazs/p/4741427.html

版权声明:本作品采用知识共享署名-非商业性使用-禁止演绎 2.5 中国大陆许可协议进行许可。

分类:

大学竞赛 / 电赛学习

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步