FGPA 中的计数器Verilog语言(时钟分频器)

在quartusII8.0中为ALTERAFPGA设置一个分频器(计数器)

输入时钟48Mhz

输出时钟9600HZ

1 /* 实验名称: 计数器 2 ** 程序功能: 将48Mhz的时钟分频为9600Hz 3 ** 时钟计算:9600*5000=48000000,,48Mhz的时钟累加5000次获得9600Hz的时钟,由于去的的clk的反向所以最终获得9600Hz的时钟需要累加2500次 4 */ 5 6 module Conter_500 7 ( CLK_48MHz, 8 Reset, 9 CLKout 10 ); 11 12 input CLK_48MHz; //系统时钟50MHZ 13 input Reset; // 全局复位,低电平有效 14 output CLKout; //CLK时钟输出(9600) 15 16 //2500 => 0x9c4 => 4*3 = 12位 17 reg[11:0] cnt; //定义计数器寄存器 18 reg clkout; //定义输出寄存器 19 20 //计数器程序块 21 //always :对某些信号的变化感兴趣 22 //posedge : 表示CLK_48MHz 上升沿会进入程序块 23 //negedge : 表示Reset 下降沿会进入程序块 24 always@(posedge CLK_48MHz or negedge Reset) 25 begin 26 if(1'b0 == Reset) //当Reset引脚低电平表示复位 27 cnt <= 12'd0; //复位时,值计数器的值为0 28 else if(cnt == 12'd2499) //当计数达到500时(因为计数从0开始) 29 begin 30 cnt <= 12'd0; //计数器值置0,避免溢出 31 clkout = ~clkout; //输出clk反向 32 end 33 else 34 cnt <= cnt + 1'b1; //计数器计数(累加) 35 end 36 37 assign CLKout=clkout; //将clkout寄存器输出连接至实际的CLKOUT(引脚) 38 39 endmodule

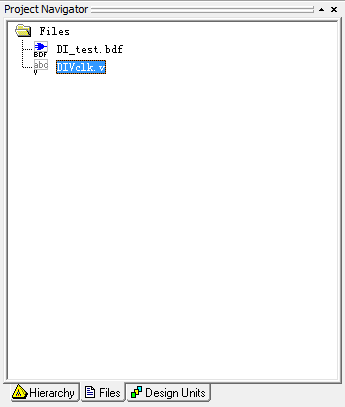

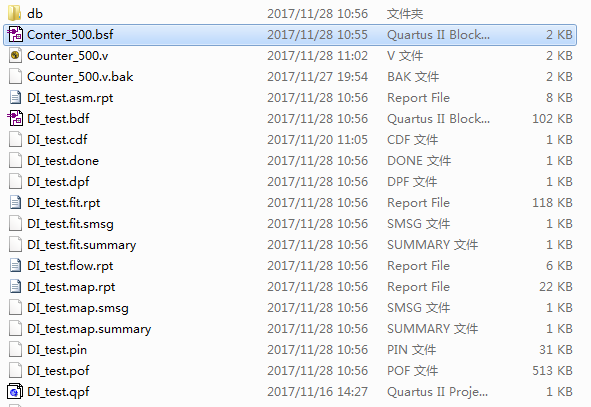

在project Navigator的Files下如图:(现将DIVclk.v添加至Files中,右键Files会有相应的提示)

右键DIVclk.v

在project navigator 中的file 目录下找到源文件,右键点击源文件,选中 create symbol files for current file.

QuartusII会先编译DIVclk.v,无错误后会生成DIVclk的原理图文件,生成的原理图文件在DIVclk的添加的工程中。

浙公网安备 33010602011771号

浙公网安备 33010602011771号