【FPGA】FIR数字滤波器设计心得

【FPGA】FIR数字滤波器设计心得

0 前言

学校的课程设计要求设计FIR滤波器,FPGA芯片是Xilinx的Artix 7,板卡是依元素科技有限公司做的拓展板,2017年的,目前搜不到了,估计是被迭代了。

本文作为课程设计的复盘和总结。

1 FIR滤波器设计

1.1 原理

输入输出特性: FIR(Finite Impulse Response)滤波器是其冲激响应为有限长度的滤波器,针对因果离散时间的N阶滤波器,输出序列的每一个值都是最近输入的加权和:

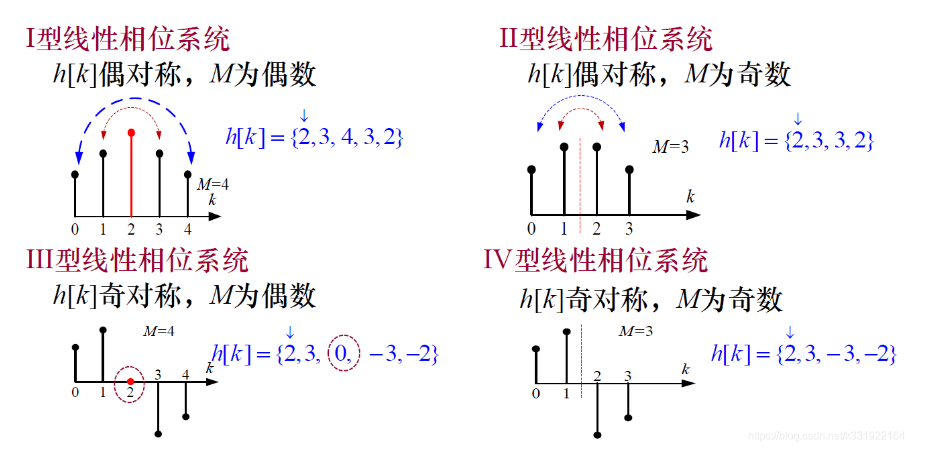

线性相位: 当FIR滤波器的抽头系数具有对称性(奇对称/偶对称)时,FIR滤波器的相频响应具有线性特征,即输入信号的各组份频率之间的相位关系经过滤波器后不发生改变。

线性相位FIR滤波器的系数存在四种情况,如下图(h[k]为抽头系数,M为阶数):

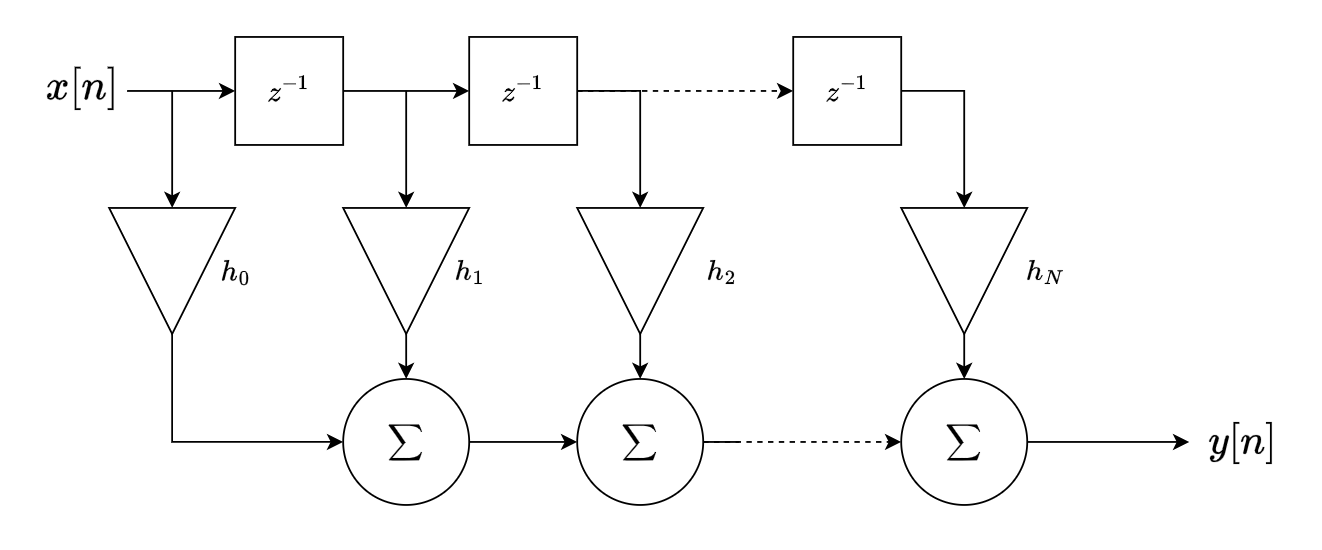

1.1 一般结构框图

1.2 简单分析

FIR滤波器的十分简单,从输入输出方程来看就是系数h和输入x之间的卷积操作,拆解开来就是,存储,相乘,相加。

1.2.1 存储

- 对于M阶FIR滤波器,需要M+1个寄存器来暂存M+1个输入数据,并且这M+1寄存器需要组成一个FIFO。

- 对于M阶FIR滤波器,需要M+1个寄存器来存储M+1个抽头系数,系数决定了滤波器的截止频率,通带特性等等。

1.2.2 相乘

相乘很简单,在verilog中就是两个寄存器值的相乘,值得一提的是,如果系数符合对称特性,我们可以通过对称式结构设计来减少一半的相乘操作,此外,还可以减少一半的抽头系数的存储。

1.2.3 相加

累加操作是比较消耗时间的,需要加的数越多,消耗的时钟周期就越多。一半单纯的累加,x个数据需要消耗x-1个时钟周期来完成,本次使用的是喜闻乐见的所谓多级流水线累加,即增加并行的加法语句,同周期内尽可能增加加法语句来缩短消耗的时间,代价是增加了相关的资源消耗。

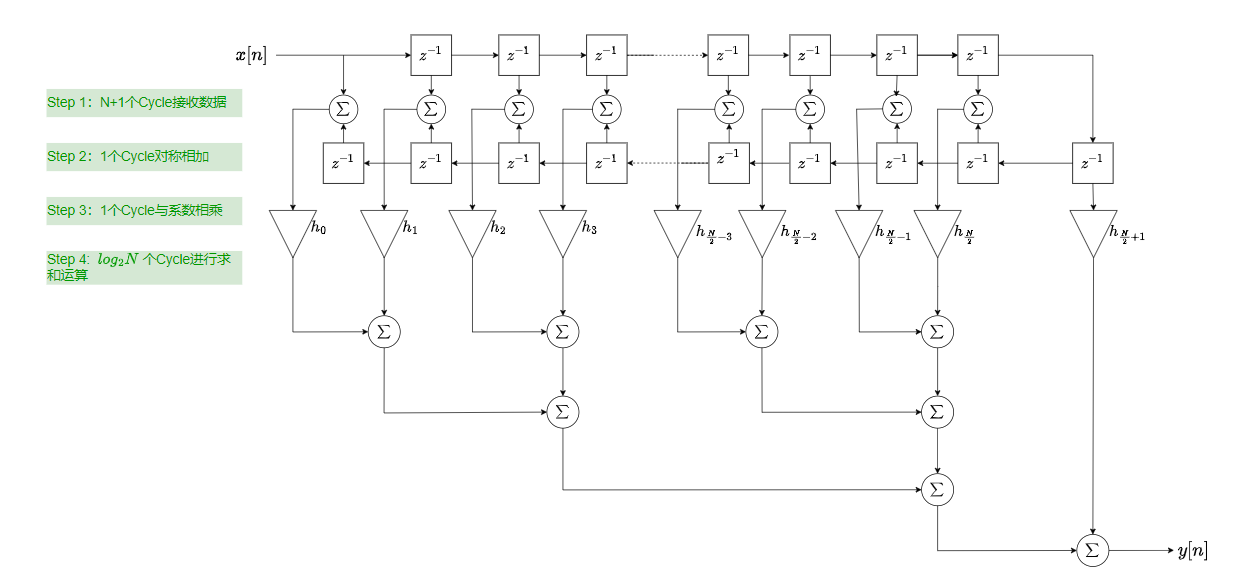

1.3 设计结构框图

以阶数N=16为例,如图

以上是一个16阶的对称式FIR设计图,总的来讲,对于偶数阶N的FIR滤波器设计,需要N+1个移位寄存器暂存连续数据,需要N/2+1个乘法器用于数据相乘运算,以及若干加法器用于数据的累加,累加的结果即为FIR滤波的输出结果。

2 模数转换

2.1 ADC10080

ADC10080是板卡上的ad芯片型号,速率最高80MSPS,数字位宽10bits,并行输出。该芯片的理论输入电压规范是1.45V offset,2.00Vpp,输出数据符合Offset Binary格式,即输出数字为非负数,输入电压最小值对应0000000000,输入电压最大值对应1111111111 。

2.2 DAC900

DAC900是板卡上的da芯片型号,速率最高165MSPS,数字位宽10bits,并行输入。该芯片的理论输入数据是标准正二进制编码。需要留意,该芯片的Bit1管脚数据位是MSB(Most Significant Bit),即最高位。

3 系数生成

系数使用matlab的filter designer辅助设计并量化。

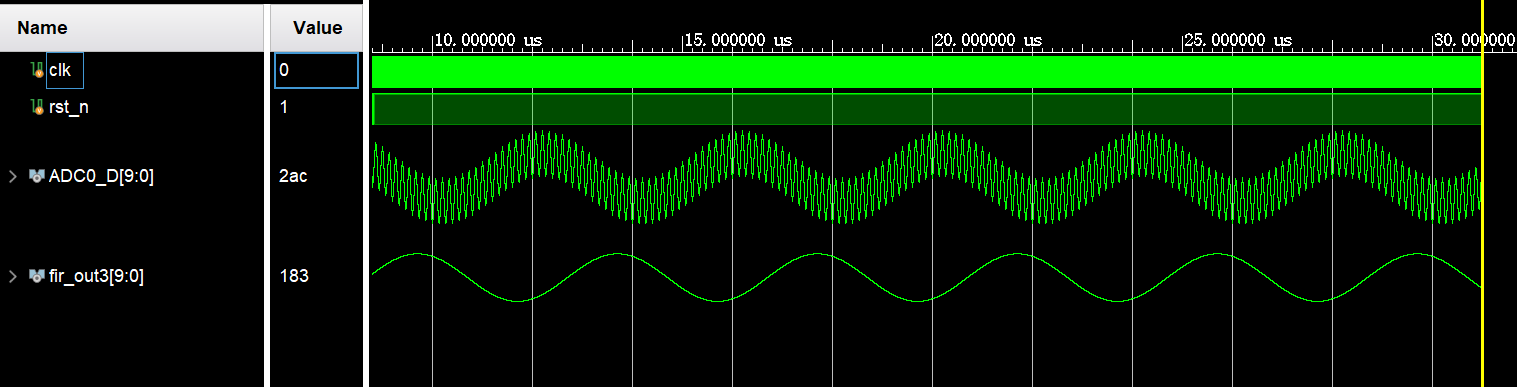

4 仿真

仿真输入数据为7.5MHz和250KHz的叠加波,具体滤波效果如下.

低通:

高通:

5 实测

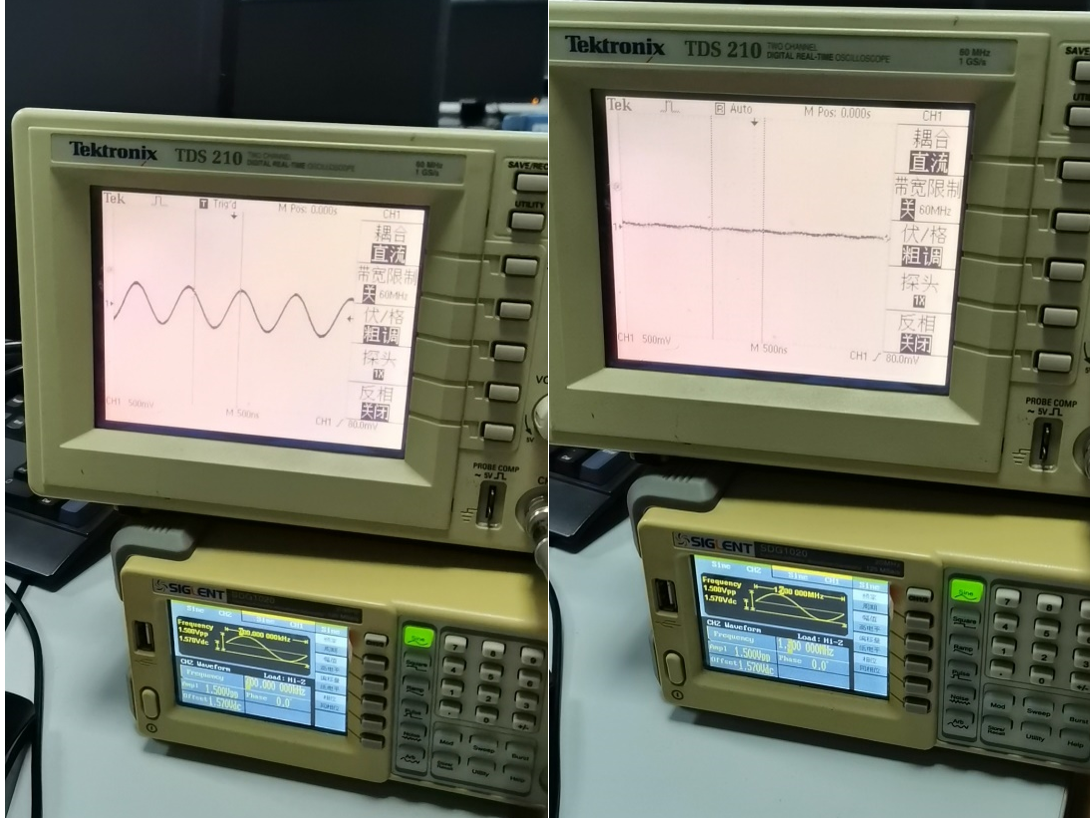

低通:

高通:

6 尚留疑问

对于128阶的FIR滤波器,我发现滤波器的过渡带宽比较大,从通带到阻带大概有几百KHz,在不增加阶数的条件下,如何减小过渡带宽是一个问题。

参考资料:

https://blog.csdn.net/k331922164/article/details/117536723

https://www.runoob.com/w3cnote/verilog-fir.html