DSPIC33CK BLDC 驱动 by Rocky MCS part I

背景:

1,基于microchip的e scooter 方案

https://www.microchip.com/en-us/solutions/motor-control-and-drive/applications-and-reference-designs/e-scooter-reference-design、全部的设计文件,硬件软件都是可以下载的。

2,前期我在STM32上已经实现了简单的驱动,电机正常转起来了。这个STM32的板子是自己做的,所以目前我对这个电机要正常的转起来需要哪些基础的东西是有一个大概的了解的,我觉得这个是很关键的一点。前期不要抠细节,先有个总体的概念,然后一遍一遍的研究,把每个细节都把握到。视频链接https://www.ixigua.com/7080891003573535245?logTag=868b25babc4cafc6a2c6

3,现在使用的平台是DM330031 https://www.microchip.com/en-us/development-tool/DM330031

那为什么又要用microchip这个平台来做呢?

第一点:这个平台是从官方渠道买的,硬件的性能是可以保证的,如果在使用过程中出现问题,那大概率是软件的问题。

第二点:之前做STM32的板子做测试就是想大概把驱动流程熟悉一下,积累一些经验避免烧板子(STM32确实烧过)。

第三点:dspic33ck这个芯片我也不是很熟悉,所以想通过这个实验来熟悉一下细节。本次不使用MCC配置。感觉这个是后期提高效率可以用的工具,初学不太好,虽然可以很快速的配置一个项目,但对于学习帮助感觉不大。还是要从寄存器配置开始。

目标:

1,熟悉,时钟,ADC,PWM,GPIO,串口

2,实现霍尔方波驱动。

//********************************工程配置 开始**********************************************

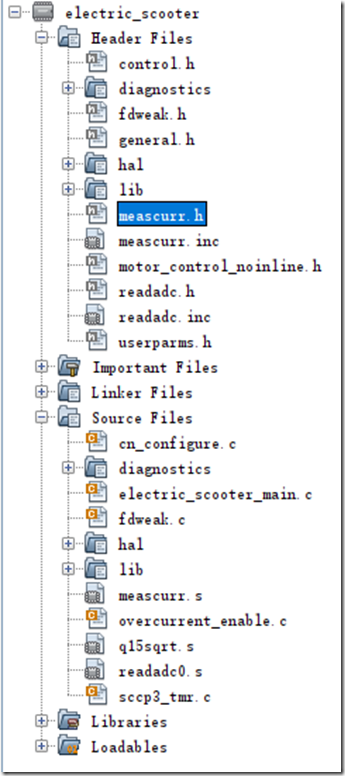

结构就参照官方的这个结构

1,配置位(特殊功能)

这个好像只有microchip出的单片机有这个东西。官方的说法:特殊功能的作用旨在最大限度的提高应用的灵活性和可靠性,并通过减少外部元器件将成本降至最低。可配置的模块如下:

• 灵活的配置

• 看门狗定时器(WDT)

• 代码保护和CodeGuard™安全性

• JTAG边界扫描接口

• 在线串行编程(ICSP)

• 在线仿真

• 欠压复位(Brown-out Reset,BOR)

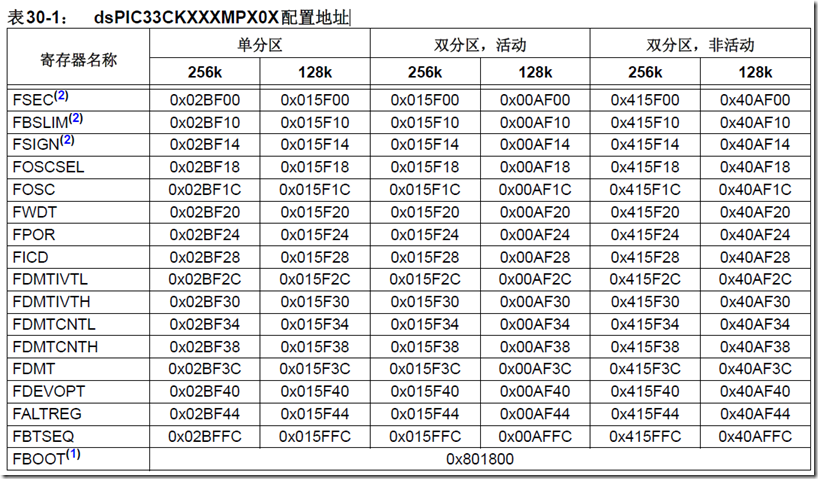

具体操作是通过#pragma 来配置,具体配置地址如下(规格书中有)。

配置字以易失性

存储方式实现。这就意味着每次器件上电时都要将配置

数据从闪存配置字装入易失性存储器。配置数据存储在

片上程序存储空间的末尾,称为闪存配置字。

对程序存储器的最后一页执行页擦除操作会清除闪存配置字。(做bootloader 是不是要注意这一点)

根据容量的不同寄存器地址有相应的变化。具体配置

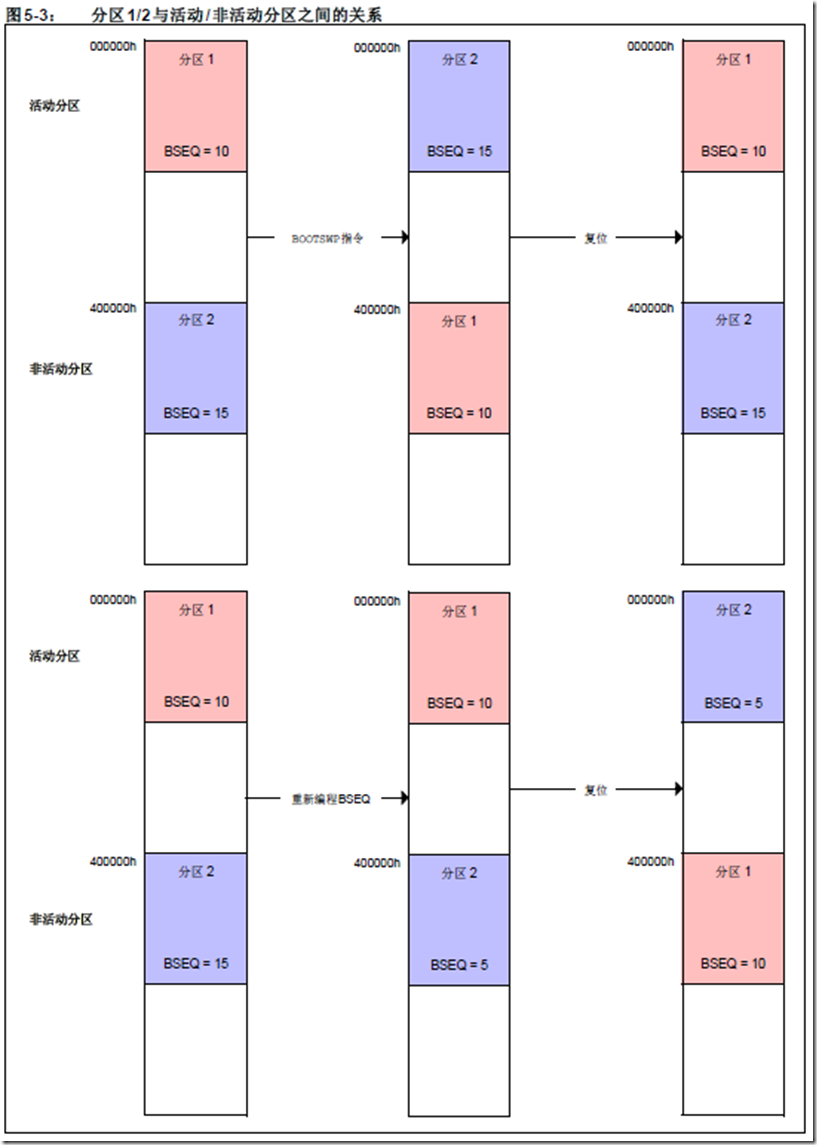

双分区的作用应该是用来做备份OTA的。通过BSEQ位的配置来确定哪个作为活动分区。

可能有些疑问,这么多的配置以及不同模式对应的值在哪里可以找到?在MPLAB的IDE里面有专门配置的地方

window->Target memory views-> configurations bits

1.1,FSEC配置寄存器

默认的配置都是没有任何保护的,可以根据自己的需求进行配置

bit 23-16 未实现:读为1

bit 15 AIVTDIS:备用中断向量表禁止位

1 = 禁止AIVT

0 = 使能AIVT

#pragma config AIVTDIS = OFF // Alternate Interrupt Vector Table bit (Disabled AIVT)

bit 14-12 未实现:读为1

bit 11-9 CSS<2:0>:配置段代码闪存保护级别位

111 = 无保护(CWRP写保护除外)

110 = 标准安全性

10x = 增强安全性

0xx = 高安全性

#pragma config CSS = DISABLED // Configuration Segment Code-Protect Level bits (No Protection (other than CWRP))

bit 8 CWRP:配置段写保护位

1 = 配置段不被写保护

0 = 配置段被写保护

#pragma config CWRP = OFF // Configuration Segment Write-Protect bit (Configuration Segment may be written)

bit 7-6 GSS<1:0>:通用段代码闪存保护级别位

11 = 无保护(GWRP写保护除外)

10 = 标准安全性

0x = 高安全性

#pragma config GSS = DISABLED // General Segment Code-Protect Level bits (No Protection (other than GWRP))

bit 5 GWRP:通用段写保护位

1 = 用户程序存储区不被写保护

0 = 用户程序存储区被写保护

#pragma config GWRP = OFF // General Segment Write-Protect bit (General Segment may be written)

bit 4 未实现:读为1

bit 3 BSEN:引导段控制位

1 = 无引导段

0 = 引导段大小由BSLIM<12:0>决定

#pragma config BSEN = OFF // Boot Segment Control bit (No Boot Segment)

bit 2-1 BSS<1:0>:引导段代码闪存保护级别位

11 = 无保护(BWRP写保护除外)

10 = 标准安全性

0x = 高安全性

#pragma config BSS = DISABLED // Boot Segment Code-Protect Level bits (No Protection (other than BWRP))

bit 0 BWRP:引导段写保护位

1 = 用户程序存储区不被写保护

#pragma config BWRP = OFF // Boot Segment Write-Protect bit (Boot Segment may be written)

从目前的FSEC配置来看是没有对代码进行保护的,如果是面向量产开发的话这点需要考虑一下。

1.2,FBSLIM配置寄存器

这个应该是用来保护引导代码,避免误擦除的,目前还没有用到,就给默认值了。

bit 23-13 未实现:读为1

bit 12-0 BSLIM<12:0>:引导段代码闪存页地址限制位

包含第一个有效的通用段页的页地址。要编程的值为页地址的补码,这样编程额外的0只会增加引导段的大小。

#pragma config BSLIM = 0x1FFF // Boot Segment Flash Page Address Limit bits (Boot Segment Flash page address limit)

1.3 FOSCSEL配置寄存器

双速启动的配置,内部和外部时钟同时启动,做时钟备份???默认是关的

后面是选振荡器的。这里选的事内部时钟FRC。

bit 23-8 未实现:读为1

bit 7 IESO:内/外部时钟源切换位

1 = 使能内/外部时钟源切换模式(使能双速启动)

0 = 禁止内/外部时钟源切换模式(禁止双速启动)

#pragma config IESO = OFF // Two-speed Oscillator Start-up Enable bit (Start up with user-selected oscillator source)

bit 6-3 未实现:读为1

bit 2-0 FNOSC<2:0>:初始振荡器源选择位

111 = 带后分频器的内部快速RC(FRC)振荡器

110 = 备用快速RC(BFRC)

101 = LPRC振荡器

100 = 保留

011 = 带PLL的主振荡器(XTPLL、HSPLL和ECPLL)

010 = 主振荡器(XT、HS和EC)

001 = 带PLL的内部快速RC振

#pragma config FNOSC = FRC // Oscillator Source Selection (Internal Fast RC (FRC))

1.4 FOSC配置寄存器

bit 23-13 未实现:读为1

bit 12 XTBST:振荡器启动编程位

1 = 加快启动

0 = 默认启动

振荡器启动模式,可以选择快速启动。目前没有特殊要求,就选的默认的。可能在一些对时钟的建立有特殊需求的会用到。

#pragma config XTBST = DISABLE // XT Boost (Boost the kick-start)

bit 11-10 XTCFG<1:0>:晶振驱动选择位

振荡器的电流增益编程(输出驱动)。

11 = 增益3(用于24-32 MHz晶振)

10 = 增益2(用于16-24 MHz晶振)

01 = 增益1(用于8-16 MHz晶振)

00 = 增益0(用于4-8 MHz晶振)

振荡器电流增益。这个肯定是增益越大,起震越快,信号越稳定,但电流消耗也是会高的。可以作为低功耗的一个优化点。

#pragma config XTCFG = G3 // XT Config (24-32 MHz crystals)

bit 9 未实现:读为1

bit 8 PLLKEN:PLL锁定状态控制位(1)

1 = 如果锁定丢失,PLL锁定信号将用于禁止PLL时钟输出

0 = 不使用PLL锁定信号;如果锁定丢失,不会禁止PLL时钟输出

PLL锁相环,选锁相环的话需要锁住这个位。

#pragma config PLLKEN = LOCK // PLL Lock source select (Source for PLL Lock signal is lock detect)

bit 7-6 FCKSM<1:0>:时钟切换模式位

1x = 禁止时钟切换,禁止故障保护时钟监视器

01 = 使能时钟切换,禁止故障保护时钟监视器

00 = 使能时钟切换,使能故障保护时钟监视器

从官方的配置来看是,使能时钟切换,禁止故障保护时钟监视器

#pragma config FCKSM = CSECMD // Clock Switching Mode bits (Clock switching is enabled,Fail-safe Clock Monitor is disabled)

bit 5-3 未实现:读为1

bit 2 OSCIOFNC:OSCO引脚功能位(XT和HS模式下除外)

1 = OSCO为时钟输出

0 = OSCO为通用数字I/O引脚

OSC脚可以作为普通IO使用。

#pragma config OSCIOFNC = ON // OSC2 Pin Function bit (OSC2 is general purpose digital I/O pin)

bit 1-0 POSCMD<1:0>:主振荡器模式选择位

11 = 禁止主振荡器

10 = HS晶振模式(10 MHz-32 MHz)

01 = XT晶振模式(3.5 MHz-10 MHz)

00 = EC(外部时钟)模式

内部时钟

#pragma config POSCMD = NONE // Primary Oscillator Mode Select bits (Primary Oscillator disabled)

注1: 当系统时钟切换逻辑请求PLL时钟源且PLL尚未使能时,将发生超时周期。

1.5 FWDT配置寄存器

bit 23-16 未实现:读为1

bit 15 FWDTEN:看门狗定时器使能位

1 = 在硬件中使能WDT

0 = WDT由ON位(WDTCONL<15>)控制

硬件看门狗还是软件看门狗的选择

#pragma config FWDTEN = ON_SW // Watchdog Timer Enable bit (WDT controlled via SW, use WDTCON.ON bit)

bit 14-10 SWDTPS<4:0>:休眠模式看门狗定时器周期选择位

11111 = 分频值为2 ^ 31(= 2,147,483,648)

11110 = 分频值为2 ^ 30(= 1,073,741,824)

...

00001 = 分频值为2 ^ 1(= 2)

00000 = 分频值为2 ^ 0(= 1)

休眠模式看门狗周期选择

#pragma config SWDTPS = PS1048576 // Sleep Mode Watchdog Timer Post Scaler select bits (1:1048576)

bit 9-8 WDTWIN<1:0>:看门狗定时器窗口选择位

11 = WDT窗口为WDT周期的25%

10 = WDT窗口为WDT周期的37.5%

01 = WDT窗口为WDT周期的50%

00 = WDT窗口为WDT周期的75%

#pragma config WDTWIN = WIN25 // Watchdog Timer Window Select bits (WDT Window is 25% of WDT period)

bit 7 WINDIS:看门狗定时器窗口使能位

1 = 看门狗定时器处于非窗口模式

0 = 看门狗定时器处于窗口模式

#pragma config WINDIS = ON // Watchdog Timer Window Enable bit (Watchdog Timer operates in Non-Window mode)

bit 6-5 RCLKSEL<1:0>:看门狗定时器时钟选择位

11 = LPRC时钟

10 = 当WINDIS = 0、系统时钟不是INTOSC/LPRC且器件未处于休眠模式时,使用FRC;否则,使用

INTOSC/LPRC

01 = 当系统时钟不是INTOSC/LPRC 且器件未处于休眠模式时,使用外设时钟;否则,使用INTOSC/LPRC

00 = 保留

#pragma config RCLKSEL = LPRC // Watchdog Timer Clock Select bits (Always use LPRC)

bit 4-0 RWDTPS<4:0>:运行模式看门狗定时器周期选择位

11111 = 分频值为2 ^ 31(= 2,147,483,648)

11110 = 分频值为2 ^ 30(= 1,073,741,824)

...

00001 = 分频值为2 ^ 1(= 2)

00000 = 分频值为2 ^ 0(= 1)

#pragma config RWDTPS = PS1048576 // Run Mode Watchdog Timer Post Scaler select bits (1:1048576)

1.6 FPOR配置寄存器

bit 23-11 未实现:读为1

bit 10 保留:保持为1

bit 9-7 未实现:读为1

bit 6 BISTDIS:存储器BIST功能禁止位(1)

1 = 禁止复位时MBIST功能

0 = 使能复位时MBIST功能

#pragma config BISTDIS = DISABLED // Memory BIST Feature Disable (mBIST on reset feature disabled)

bit 5-4 保留:保持为0b11

bit 3-0 未实现:读为1

注1: 仅适用于上电复位(POR)。

1.7 FICD配置寄存器

bit 23-16 未实现:读为1

bit 15 NOBTSWP:BOOTSWP指令禁止位

1 = 禁止BOOTSWP指令

0 = 使能BOOTSWP指令

#pragma config NOBTSWP = DISABLED // BOOTSWP instruction disable bit (BOOTSWP instruction is disabled)

bit 14-8 未实现:读为1

bit 7 保留:保持为1

bit 6 未实现:读为1

bit 5 JTAGEN:JTAG使能位

1 = 使能JTAG端口

0 = 禁止JTAG端口

#pragma config JTAGEN = OFF // JTAG Enable bit (JTAG is disabled)

bit 4-2 未实现:读为1

bit 1-0 ICS<1:0>:ICD通信通道选择位

11 = 通过PGC1和PGD1进行通信

10 = 通过PGC2和PGD2进行通信

01 = 通过PGC3和PGD3进行通信

00 = 保留;不要使用

#pragma config ICS = PGD3 // ICD Communication Channel Select bits (Communicate on PGEC3 and PGED3)

1.8 FDMTIVTL配置寄存器

bit 23-16 未实现:读为1

bit 15-0 DMTIVT<15:0>:DMT窗口间隔低16位

#pragma config DMTIVTL = 0x0 // Dead Man Timer Interval low word (Lower 16 bits of 32 bitDMT window interval (0-0xFFFF))

1.9 FDMTIVTH配置寄存器

bit 23-16 未实现:读为1

bit 15-0 DMTIVT<31:16>:DMT窗口间隔高16位

#pragma config DMTIVTH = 0x0 // Dead Man Timer Interval high word (Uper 16 bits of 32 bitDMT window interval (0-0xFFFF))

1.10 FDMTCNTL配置寄存器

bit 23-16 未实现:读为1

bit 15-0 DMTCNT<15:0>:DMT指令计数超时值低16位

#pragma config DMTCNTL = 0x0 // Lower 16 bits of 32 bit DMT instruction count time-out value (0-0xFFFF) (Lower 16 bits of 32 bit DMT instruction count time-out value (0-0xFFFF))

1.11 FDMTCNTH配置寄存器

bit 23-16 未实现:读为1

bit 15-0 DMTCNT<31:16>:DMT指令计数超时值高16位

#pragma config DMTCNTH = 0x0 // Upper 16 bits of 32 bit DMT instruction count time-out value (0-0xFFFF) (Upper 16 bits of 32 bit DMT instruction count time-out value (0-0xFFFF))

1.12 FDMT配置寄存器

bit 23-1 未实现:读为1

bit 0 DMTDIS:DMT禁止位

1 = 禁止DMT

0 = 使能DMT

#pragma config DMTDIS = OFF // Dead Man Timer Disable bit (Dead Man Timer is Disabled and can be enabled by software)

1.13 FDEVOPT配置寄存器

bit 23-14 未实现:读为1

bit 13 SPI2PIN:主SPI2快速I/O焊盘禁止位(1)

1 = 主SPI2使用PPS(I/O重映射)与器件引脚建立连接

0 = 主SPI2直接连接指定的器件引脚

#pragma config SPI2PIN = PPS // SPI2 Pin Select bit (SPI2 uses I/O remap (PPS) pins)

bit 12-11 未实现:读为1

bit 10 SMBEN:选择符合SMBus 3.0标准的I2C焊盘输入电压阈值位

1 = 使能SMBus 3.0输入阈值电压

0 = I2C焊盘输入缓冲器操作

#pragma config SMBEN = SMBUS // SM Bus Enable (SMBus input threshold is enabled)

bit 9-8 保留:保持为0

bit 7 保留:保持为1

bit 6 未实现:读为1

bit 5 ALTI2C3:备用I2C3引脚映射位

1 = SCL3/SDA3引脚的默认位置

0 = SCL3/SDA3引脚(ASCL3/ASDA3)的备用位置

#pragma config ALTI2C3 = OFF // Alternate I2C3 Pin bit (I2C3 mapped to SDA3/SCL3 pins)

bit 4 ALTI2C2:备用I2C2引脚映射位

1 = SCL2/SDA2引脚的默认位置

0 = SCL2/SDA2引脚(ASCL2/ASDA2)的备用位置

#pragma config ALTI2C2 = OFF // Alternate I2C2 Pin bit (I2C2 mapped to SDA2/SCL2 pins)

bit 3 ALTI2C1:备用I2C1引脚映射位

1 = SCL1/SDA1引脚的默认位置

0 = SCL1/SDA1引脚(ASCL1/ASDA1)的备用位置

#pragma config ALTI2C1 = OFF // Alternate I2C1 Pin bit (I2C1 mapped to SDA1/SCL1 pins)

bit 2 保留:保持为1

bit 1-0 未实现:读为1

注1: 固定引脚选项仅适用于高引脚数封装(48引脚、64引脚和80引脚)。

1.14 FALTREG配置寄存器

bit 23-15 未实现:读为1

bit 14-12 CTXT4<2:0>:指定备用工作寄存器组4的中断优先级(IPL)位

111 = 未分配

110 = 为备用寄存器组4分配IPL级别7

101 = 为备用寄存器组4分配IPL级别6

100 = 为备用寄存器组4分配IPL级别5

011 = 为备用寄存器组4分配IPL级别4

010 = 为备用寄存器组4分配IPL级别3

001 = 为备用寄存器组4分配IPL级别2

000 = 为备用寄存器组4分配IPL级别1

#pragma config CTXT4 = OFF // Specifies Interrupt Priority Level (IPL) Associated to Alternate Working Register 4 bits (Not Assigned)

bit 11 未实现:读为1

bit 10-8 CTXT3<2:0>:指定备用工作寄存器组3的中断优先级(IPL)位

111 = 未分配

110 = 为备用寄存器组3分配IPL级别7

101 = 为备用寄存器组3分配IPL级别6

100 = 为备用寄存器组3分配IPL级别5

011 = 为备用寄存器组3分配IPL级别4

010 = 为备用寄存器组3分配IPL级别3

001 = 为备用寄存器组3分配IPL级别2

000 = 为备用寄存器组3分配IPL级别1

#pragma config CTXT3 = OFF // Specifies Interrupt Priority Level (IPL) Associated to Alternate Working Register 3 bits (Not Assigned)

bit 7 未实现:读为1

bit 6-4 CTXT2<2:0>:指定备用工作寄存器组2的中断优先级(IPL)位

111 = 未分配

110 = 为备用寄存器组2分配IPL级别7

101 = 为备用寄存器组2分配IPL级别6

100 = 为备用寄存器组2分配IPL级别5

011 = 为备用寄存器组2分配IPL级别4

010 = 为备用寄存器组2分配IPL级别3

001 = 为备用寄存器组2分配IPL级别2

000 = 为备用寄存器组2分配IPL级别1

#pragma config CTXT2 = OFF // Specifies Interrupt Priority Level (IPL) Associated to Alternate Working Register 2 bits (Not Assigned)

bit 3 未实现:读为1

bit 2-0 CTXT1<2:0>:指定备用工作寄存器组1的中断优先级(IPL)位

111 = 未分配

110 = 为备用寄存器组1分配IPL级别7

101 = 为备用寄存器组1分配IPL级别6

100 = 为备用寄存器组1分配IPL级别5

011 = 为备用寄存器组1分配IPL级别4

010 = 为备用寄存器组1分配IPL级别3

001 = 为备用寄存器组1分配IPL级别2

#pragma config CTXT1 = OFF // Specifies Interrupt Priority Level (IPL) Associated to Alternate Working Register 1 bits (Not Assigned)

1.15 FBTSEQ配置寄存器

bit 23-12 IBSEQ<11:0>:引导序列号取反位(仅限双分区模式)

#pragma config IBSEQ = 0xFFF // The one's complement of BSEQ; must be calculated by the user and written during device programming. (Inverse Boot Sequence Number bits)

BSEQ<11:0>的二进制反码;必须由用户计算并写入器件编程。

bit 11-0 BSEQ<11:0>:引导序列号位(仅限双分区模式)

#pragma config BSEQ = 0xFFF // Relative value defining which partition will be active after device Reset; the partition containing a lower boot number will be active (Boot Sequence Number bits)

定义器件复位后哪个分区有效的相对值;包含较小引导序列号的分区将处于活动状态。

1.16 FBOOT配置寄存器

bit 15-2 未实现:读为1

bit 1-0 BTMODE<1:0>:器件分区模式配置状态位

11 = 单分区模式

10 = 双分区模式

01 = 受保护的双分区模式(分区1处于不活动状态时受写保护)

00 = 保留;不要使用

1.17 DEVREV:器件版本寄存器

bit 23-16 未实现:读为1

bit 15 保留:保持为0

bit 14-4 未实现:读为1

bit 3-0 DEVREV<3:0>:器件版本位

1.18 DEVID:器件ID寄存器

bit 23-16 未实现:读为1

bit 15-8 FAMID<7:0>:器件系列标识符位

0111 1100 = dsPIC33CK256MP508系列

bit 7-0 DEV<7:0>:单个器件标识符位(1)

实际配置的时候是不需要自己去写的,通过 window->Target memory views-> configurations bits 这个工具可以快速选择然后生成代码,把代码复制或者直接嵌入到工程里就可以了。

//********************************工程配置 结束**********************************************