计算机组成原理:存储器实验

实验名称: 2 存储器实验

实验目的

- 掌握静态随机存储器RAM工作特性及数据的读写方法。

- 基于信号时序图,了解读写静态随机存储器的原理。

- 掌握Cache的原理及其设计方法。

- 熟悉FPGA应用设计及EDA软件的使用。

实验设备

PC机一台,TDX-CMX实验系统一套。

实验预习

静态随机存储器实验

1、阅读实验指导书,然后回答问题。

实验所用的静态存储器由一片 6116(2K X 8bit)构成(位于 MEM 单元),6116 有三个控制线:CS(片选有效信号),OE(读操作有效信号),WE(写操作有效信号),其功能如表 2-1-1 所示,当片选有效CS= (0) 时, OE=(0) 时进行读操作,WE=(0) 时进行写操作,本实验将 CS 常接地。

2、根据SRAM 6116集成电路的管脚图回答问题。

(1)地址线的管脚号:(1 - 8,22,23,19)

(2)数据线的管脚号:(9 - 11,13 - 17)

(3)片选线管脚号:(18)

(4)读线管脚号:(20)

(5)写线管脚号:(21)

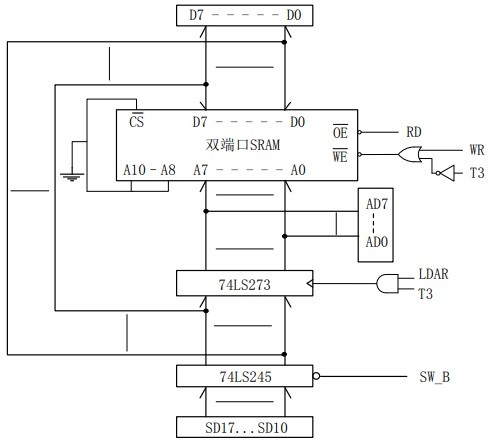

3、根据存储器实验原理图回答问题。

(1)74LS273的作用:(8位地址锁存器,存储地址)

(2)74LS245的作用:(三态门,分时输入地址和数据)

(3)信号LDAR的作用:(地址锁存器门控信号,打开时写入)

(4)信号SW_B的作用:(三态门的开关,低电平时输入有效)

Cache映射机制模拟实验

1、Cache的地址映像方式有哪些?直接映像方式的特点是什么?

答:Cache 的地址映像方式:直接映射、全相联映射、组相联映射。

直接映射的特点:每个主存块只与一个缓存块相对应;这种变换方式简单而直接,硬件实现很简单,访问速度也比较快;但是块的冲突率比较高,且不够灵活,容易使缓存的存储空间不能得到充分的利用。

2、简述直接地址映像方式的地址变换过程。

把主存按Cache 的大小分成区,一般主存容量为 Cache容量的整数倍,主存每一个分区内的块数与 Cache的总块数相等。直接映象方式把主存各个区中相对块号相同的那些块映象到 Cache 中同一块号的那个特定块中。

3、在实验连接图中,开关K7的作用是什么?H2指示灯、L7…L0指示灯和L15… L8指示灯分别表示什么含义?

K7连接Cache的RD,模拟给出CPU访问主存的读信号。

H2对应FPGA芯片中的Mo,亮表示Cache失效,灭表示命中。 L15…L8 指示灯上显示的是当前主存数据。

L7…L0上显示的值即为 Cache 送往 CPU 的数据。

实验内容

静态随机存储器实验

(一)本机运行

1、给存储器的00H和01H地址单元写入数据(数值自定义)。

(6) 0000_0000 (7) 1 (8) 1 (9) 0 (10) 1

(11) 0001_0001 (12) 0 (13) 1 (14) 0 (15) 0

(16) 0001_0001 (17) 0 (18) 1 (19) 0 (20) 0

(1) 0000_0001 (2) 1 (3) 1 (4) 0 (5) 1

(6) 0000_0001 (7) 1 (8) 1 (9) 0 (10)1

(11) 0100_0100 (12) 0 (13) 1 (14) 0 (15) 0

(16) 0100_0100 (17) 0 (18) 1 (19) 0 (20) 0

2、从存储器的00H和01H地址单元读出数据。

(1) 0000_0000 (2) 1 (3) 1 (4) 0 (5) 1

(6) 0000_0000 (7) 1 (8) 1 (9) 0 (10) 1

(11) xxxx_xxxx (12)1 (13)0 (14)1 (15) 0

(16) 0000_0001 (17) 1 (18) 0 (19) 1 (20) 0

(1) 0000_0001 (2) 1 (3) 1 (4) 0 (5) 1

(6) 0000_0001 (7) 1 (8) 1 (9) 0 (10)1

(11) xxxx_xxxx (12) 1 (13) 0 (14) 1 (15) 0

(16) 0100_0100 (17) 1 (18) 0 (19) 1 (20) 0

(二)联机运行

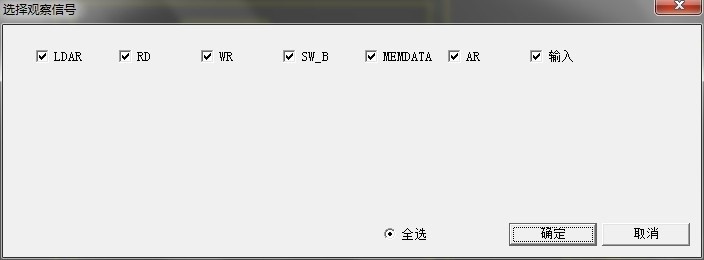

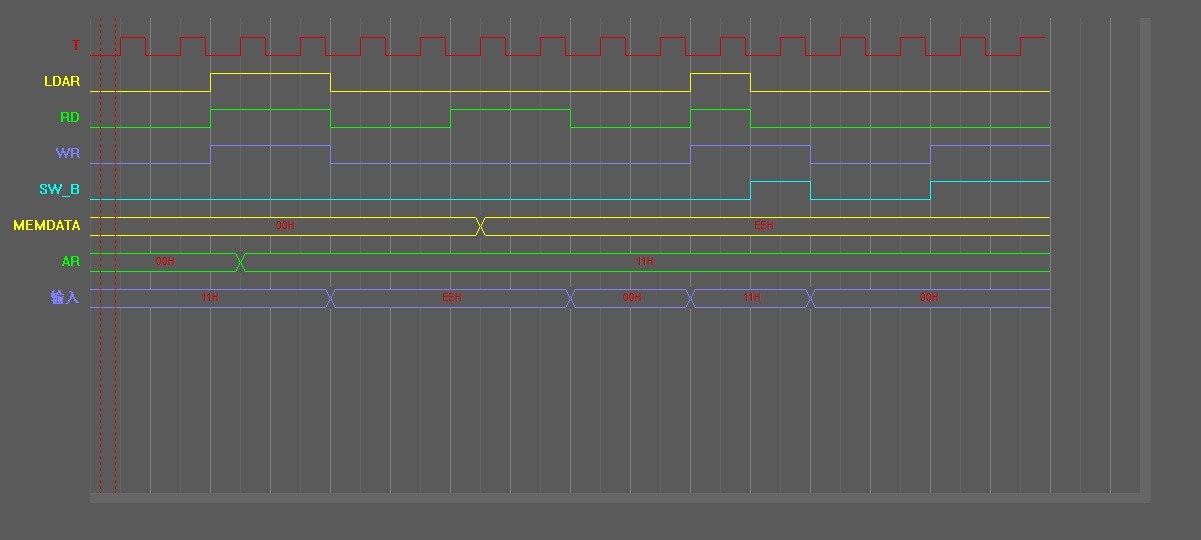

点击波形图按钮,打开选择观察信号窗口,或者选择联机软件的“【调试】-【时序观测图】”,选择想要观察的信号,如图2-1,点击确定。

将得到的时序图记录如下:

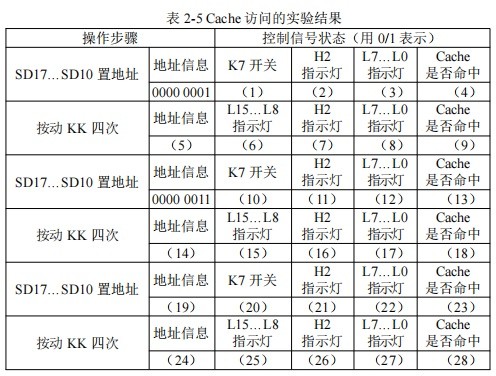

Cache映射机制模拟实验

将Cache的访问结果记录到表2-5中。

(1)0 (2)1 (3)0010_0010 (4)0 (5) 0000_0001

(6)01000100 (7)0 (8)00100010 (9)1 (10)0

(11) 0 (12)0100_0100 (13)1 (14)0000_0011 (15)0100_0100

(16)0 (17)0100_0100 (18)1 (19) 0000_0100 (20)0

(21)1 (22)01010101 (23)0 (24)0000_0100 (25)1000_1000

(26)0 (27)01010101 (28)1

实验结果及分析

实验思考题

思考题:

- 截取向存储器写入数据的时序图,观察数据何时被写入存储器,受哪些信号影响?

- 实验指导书图2-2-4中的Cache table 模块其输入的地址线是A[7..2],为什么不包括地址线A[1]和A[0]?这两根地址线的作用是什么?

- 写入数据,首先需要WR信号为低电平,其次需要将输入的开关打开,即SW_B为低电平,还需要产生T3脉冲,还需要LDAR为0。

- 区表存储器输入的是 区号+块号 这个数据,根据块号,取出对应的数据,检查有效位是否为1,对比标志位和区号是否相等。所以不需要块内地址,也就是A[0] 和 A[1],这两根线,在cache命中后,会有效输出,作为块内偏移寻址。

实验总结

掌握了静态随机存储器RAM工作特性及数据的读写方法。基于信号时序图,了解了读写静态随机存储器的原理。掌握了Cache的原理及其设计方法。

本文来自博客园,作者:江水为竭,转载请注明原文链接:https://www.cnblogs.com/Az1r/p/17418473.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号