计算机组成原理:阵列乘法器设计实验

实验名称: 1.2 阵列乘法器设计实验

实验目的

- 了解运算器的组成结构。

- 基于数据通路图,观测并分析运算器的工作原理。

- 基于信号时序图,观测并分析运算器的工作原理。

实验设备

PC机一台,TDX-CMX实验系统一套。

实验预习

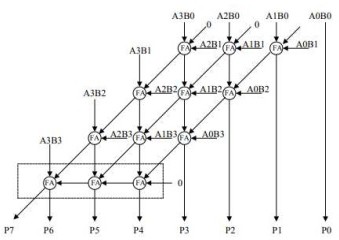

- 画出4*4阵列乘法器原理图,分析延迟与哪些因素有关。答:(上传图片)

(1)FA级数 (2)并行度 (3)FA的延迟

2. 简述Quartus环境下载sof文件到FPGA的操作流程。答

编写好Verilog HDL程序,并进行综合(Analysis & Synthe sis) ;

在Assignments -> Pin Planner中分配管脚,然后进行整体编译(Compile All) ;

连接好JTAG调试接口,接通电源;

在Tools -> Programmer中选择硬件设置(Hardware Set up),选择JTAG模式和对应的设备;

在Programmer界面中添加要下载的sof文件,并勾选Program/Con figure和Verify栏;

点击Start按钮开始下载程序到FPGA。

实验步骤

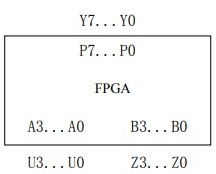

(1)根据上述阵列乘法器的原理,使用Quartus软件编辑相应的电路原理图并

进行编译,其在FPGA芯片中对应的引脚如图1所示,框外文字表示连线标号,框内文字表示该引脚的含义(本实验例程见‘安装路径FPGAMultiplyMultiply

.qpf’工程)。

图1 FPGA引脚分配

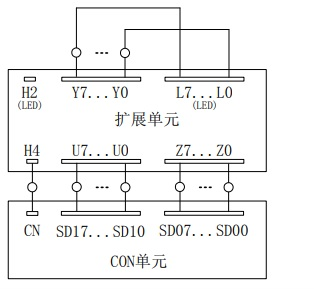

(2)关闭实验系统电源,按接线图连接实验电路。图中将用户需要连接的信号用圆圈标明。

图2 阵列乘法器连接图

(3)打开实验系统电源,将下载电缆插入扩展单元的E_JTAG口,把生成的文件下载到扩展单元中去。

(4)以CON单元中的SD10…SD13四个二进制开关为乘数A,SD03…SD00四个二进制开关为被乘数B,而相乘的结果在扩展单元的L7…L0八个LED灯显示。

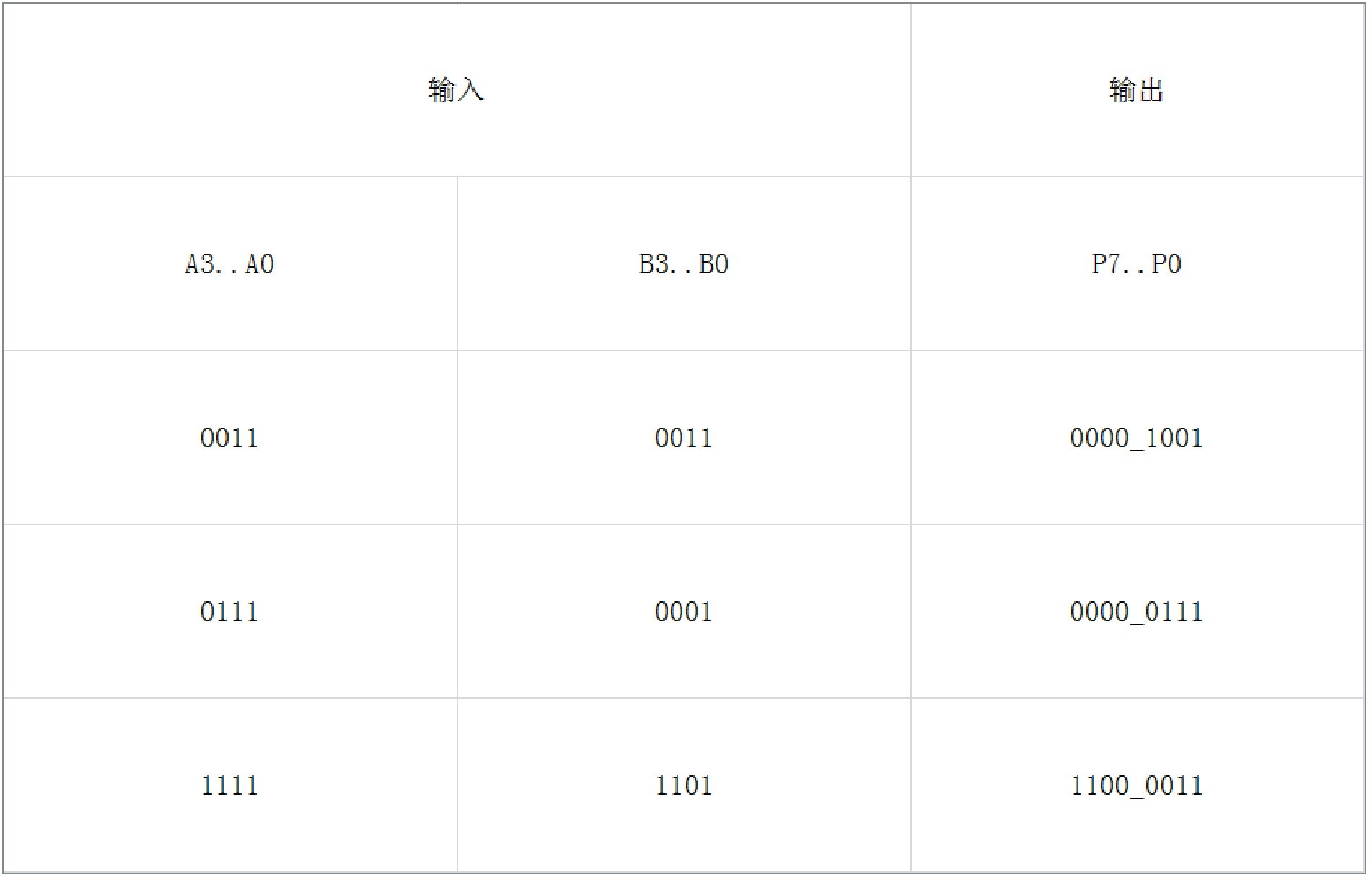

(5)给A和B 置不同的数,观察相乘的结果。 完成实验报告表格。记录被乘数、乘数和乘积:

SD17~SD10 输入数据:(0000_0011)SD07~SD00 输入数据:( 0000_0011)L7~L0:(0000_1001)

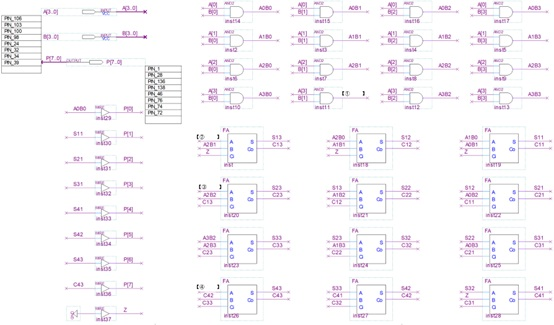

下面是该阵列乘法器实现逻辑图,补充括号内缺失的信号名称。

答案: 1. A3B1 2. A3B0 3. A3B1 4.A3B3

实验结果及分析

实验思考题

唐朔飞计算机组成原理这本书中无符号原码一位乘(4位)的时间延迟是由加法器和移位寄 存器决定的,每一步需要进行一次加法和一次移位操作,共需进行4步,所以总的时间延迟是4倍的加法器和移位寄存器的时间延迟;

TDX一CMX实验中阵列乘法器的时间延迟是由半加器、全加器和选择器决定的,每一层

需要经过一个半加器、一个全加器和一个选择器,共需经过4层,所以总的时间延迟是4倍的半加器、全加器和选择器的时间延迟;

比较两者的时间延迟,需要知道具体的电路参数和实现方式,一般来说,阵列乘法器比无符号原码一位乘更快,因为它可以并行地进行部分积的计算。

实验总结

了解了运算器的组成结构,了解了Quartus环境下FPGA的部署,了解了4*4阵列乘法器,分析了时间延迟。

本文来自博客园,作者:江水为竭,转载请注明原文链接:https://www.cnblogs.com/Az1r/p/17418467.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号