[Vivado] 用ILA采集低速信号

Low frequency debug with ILA cores and Logic Analyzer in Vivado

问题

FPGA驱动AD7606进行信号采集,想用ILA看看采回来的信号是多少,奈何主时钟是50 MHz,默认的情况下ILA会以50 MHz的采样率去采样并记录。但是AD7606的采样率只有200kHz,如果用50MHz的ILA的采样率去查看AD7606的信号,会有大部分的采用是重复的点,因此急需让ILA的采样率降低到200kHz。但是ILA要求ILA的时钟频率是JTAG的2倍以上,这样就意味着不能靠降低ILA输入时钟的方法来降低ILA的速率。

Capture control

在设置ILA ip core的时候,有一个Capture control的选择,可以勾选,使得ILA在trigger为1的时候进行采用。这样可以利用AD7606的数据有效信号(data valid)来实现低频率采样,具体操作如下。

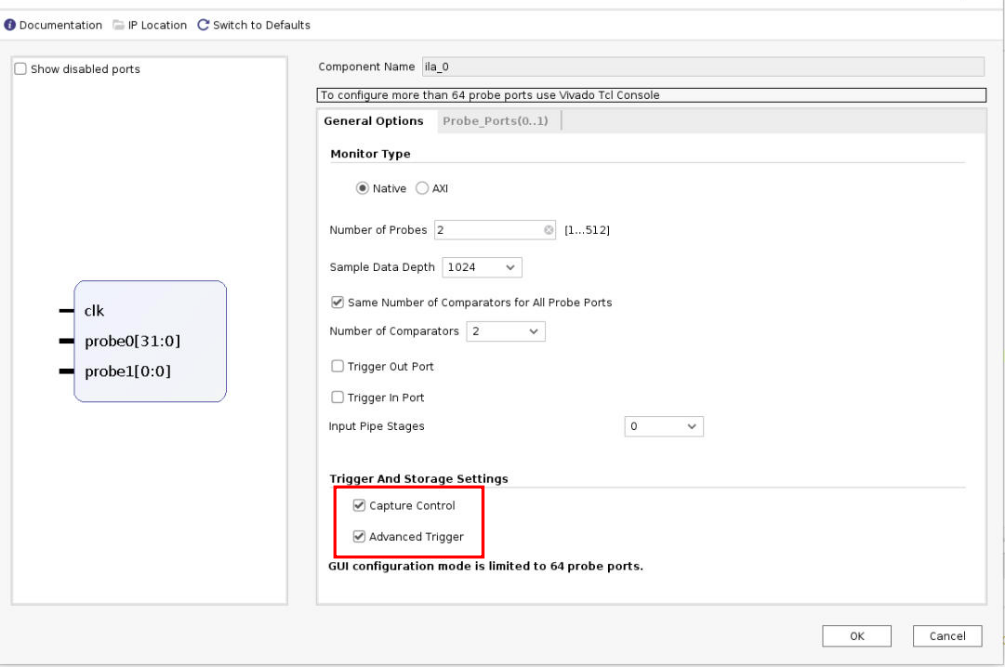

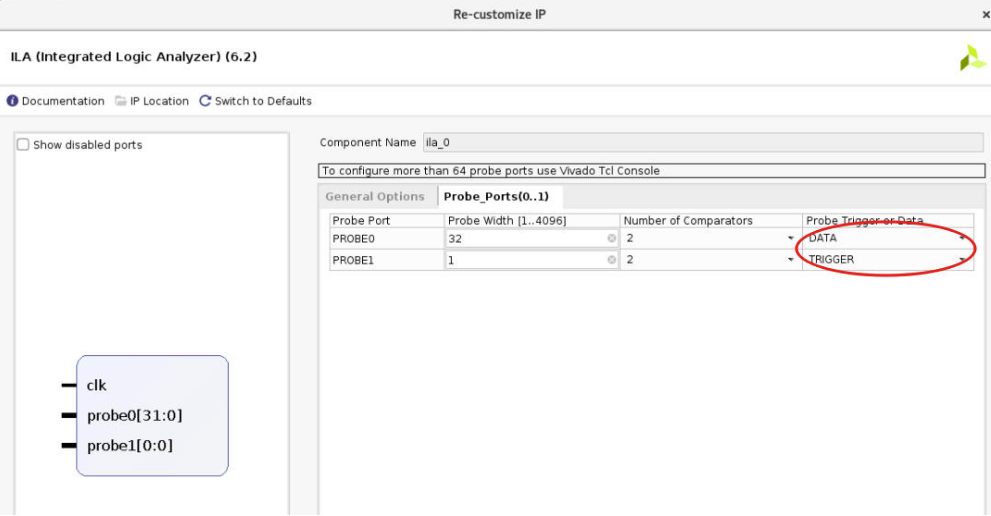

首先要勾选Capture Control 和 Advanced Trigger

之后需要两个输入,一个是32位的数据线,一个是1位的触发线

手中暂时没有AD7606,我就简单写了个demo,来测试效果。

点击查看代码

module led(

input sys_clk_p,

input sys_clk_n,

input rst,

output reg[3:0] led

);

reg[31:0] timer_cnt;

wire sys_clk;

clk cl(sys_clk_p, sys_clk_n, sys_clk);

always@(posedge sys_clk or negedge rst)

begin

if(rst)

begin

led <= 4'd0;

timer_cnt <= 32'd0;

end

else if(timer_cnt >= 32'd49_999_999)

begin

led <= ~led;

timer_cnt <= 32'd0;

end

else

begin

led <= led;

timer_cnt <= timer_cnt + 32'd1;

end

end

wire trigger;

reg [31:0] trigger_cnt;

always@(posedge sys_clk or negedge rst)begin

if(rst) begin;

trigger_cnt <= 32'd0;

end

else if(trigger_cnt >= 32'd700) begin

trigger_cnt <= 32'd0;

end

else begin

trigger_cnt <= trigger_cnt + 32'd1;

end

end

assign trigger = (trigger_cnt==32'd700);

ila_0 your_instance_name (

.clk(sys_clk), // input wire clk

.probe0(timer_cnt), // input wire [31:0] probe0

.probe1(trigger) // input wire [0:0] probe1

);

endmodule

module clk(

input clk_p,

input clk_n,

wire clk

);

begin

IBUFGDS CLK_U(

.I(clk_p),

.IB(clk_n),

.O(clk)

);

end

endmodule

用ILA来检测计数器的值,其中trigger每700个时钟高电平一周期,所以用来做trigger信号。

效果

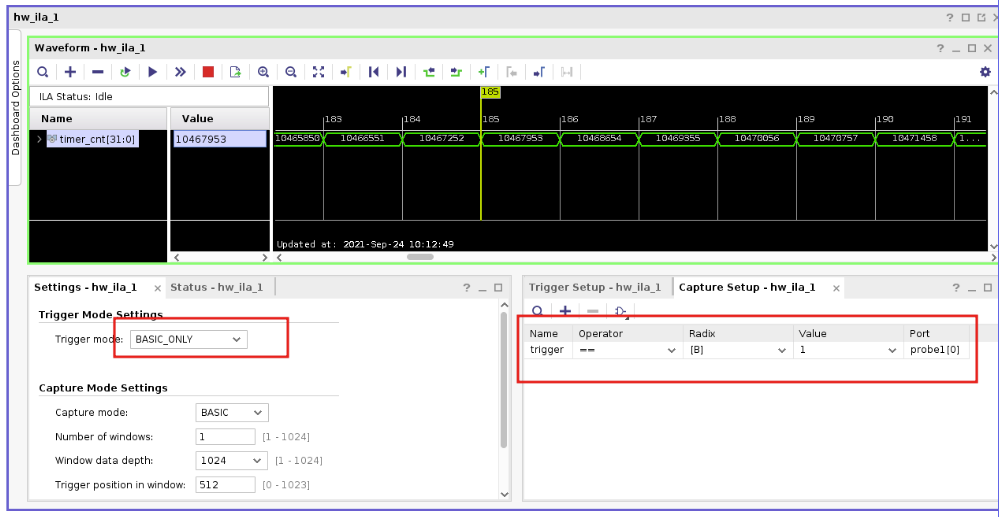

在Vivado中调用ILA,需要配置触发模式与Capture信号

之后可以看到采用是隔700个时钟采样一次。

AD7606的实验之后补上。