Vivado 2019.1 与 Questasim 联合仿真

背景

最近做一个光栅尺信号数据并行处理的项目(大概40路信号),加上了各种处理组件之后,vivado自带的仿真的速度特别慢,大部分时间在等待仿真结果。听过modelsim仿真的速度较快,因此就计划做联合仿真。另外我的开发环境在Ubuntu 18.04下进行。

安装

参考eetop论坛的安装方法,LINUX-x64系统安装Questasim-10.7c的详细流程 求CRACK

最近刚好装上,下面的路径需要修改自己的路径,只安装32位的程序把下面linux_x86_64改成linux就行了,目前在Linux Mint 19.3下测试成功

1.安装必要包

sudo apt-fast install default-jre default-jdk ia32-libs lsb dos2unix

2.必要设置

sudo mkdir /usr/tmp

sudo touch /usr/tmp/.flexlm

3. 安装Questasim-10.7c

sudo chmod 755 install.linux64

sudo ./install.linux64

进入图形化安装界面根据需要安装64还是32位的

安装结束

4.Crack

将sfk文件拷贝到<安装目录>/linux_x86_64/mgls/lib

sudo chmod 755 sfk #sfk文件权限为755

sudo ./sfk rep -yes -pat -bin /5589E557565381ECD00000008B5508/31C0C357565381ECD00000008B5508/ -bin /5589E557565381ECD8000000E8000000005B81C3/33C0C357565381ECD8000000E8000000005B81C3/ -bin /41574989FF415641554154554889CD534489C3/33C0C389FF415641554154554889CD534489C3/ -dir .

如果出现./sfk: error while loading shared libraries: libstdc++.so.5: cannot open shared object file: No such file or directory 则说明少安装了包,这里需要安装32位的包

sudo dpkg --add-architecture i386

sudo apt-get update

sudo apt-get install libstdc++5:i386

6. license文件生成

在windows环境下进行下面操作

-- 修改修改license.src文件

- 第一行:修改成自己主机名和mac地址 mac地址没有冒号

- 第二行:mgcld <安装目录>/linux_x86_64

- 全文:修改一下过期时间!

具体可以参考这个demo license.src demo

运行 run_me.bat 文件

将生成的mentor.dat文件拷贝到linux 的home目录

执行dos2unix ./mentor.dat

7. 环境变量设置

vim ~/.bashrc

添加下面几行

export LM_LICENSE_FILE=/home/test/mentor.dat

#修改路径

export PATH=$PATH:<安装目录>/linux_x86_64

alias licm="lmgrd -c /home/test/mentor.dat"

8. 开启license验证

执行 licm

9. 打开Questasim

执行 vsim

联合仿真配置

本节参考 vivado与modelsim的联合仿真(一), 但是这个文章中的图片都不见了。

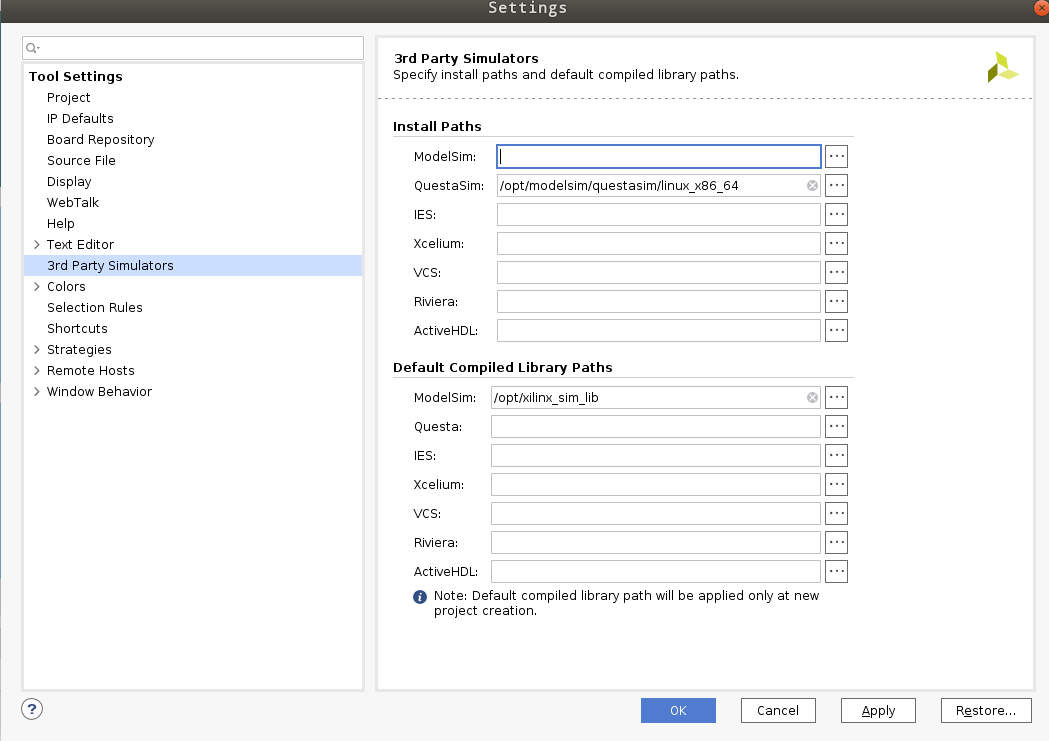

设置 Questasim 路径

在vivado菜单中选择“Tools”——>“Settings...”,在"Tool Setings"下的"3rd Party Simulators"中设置QuestaSim路径。

编译器件库

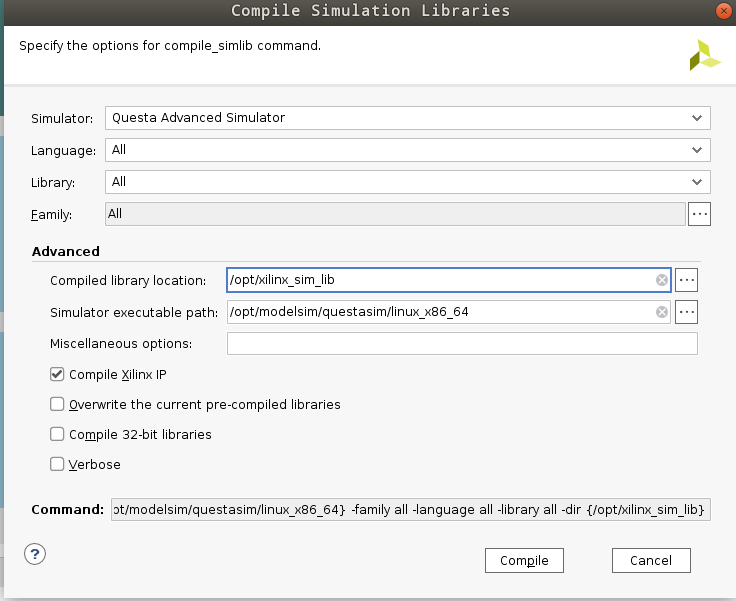

新建一个文件夹来保存,我选择/opt/xilinx_lib

接着选择vivado菜单“Tools”——>“Compile Simulation Libraries...”命令。

在弹出的对话框中设置器件库编译参数,仿真工具“Simulator”选为Questasim,语言“Language”、库“Library”、器件家族“Family”都为默认设置All(当然也可以根据自己的需求进行设置),然后在“Compiled library location”栏设置编译器件库的路径,这里选前面新建的xilinx_lib文件夹,此外在“Simulator executable path”栏设置Questasim执行文件的路径,其他参数默认,

着重注意"Simulator executable Path"

设置好参数后点击“Compile”按钮开始器件库的编译。图5所示为正在编译器件库的过程中。器件库编译结束后给出编译报告。如果结果中有错误,如果不是特别常用的IP可以忽略。

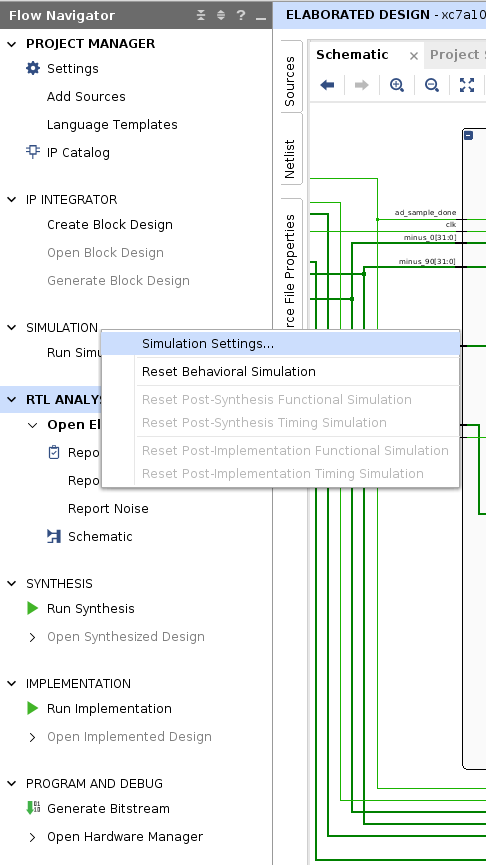

在工程中设置第三方仿真工具

在工程中的Flow Navigator中右键Simulation选择Simulation settings

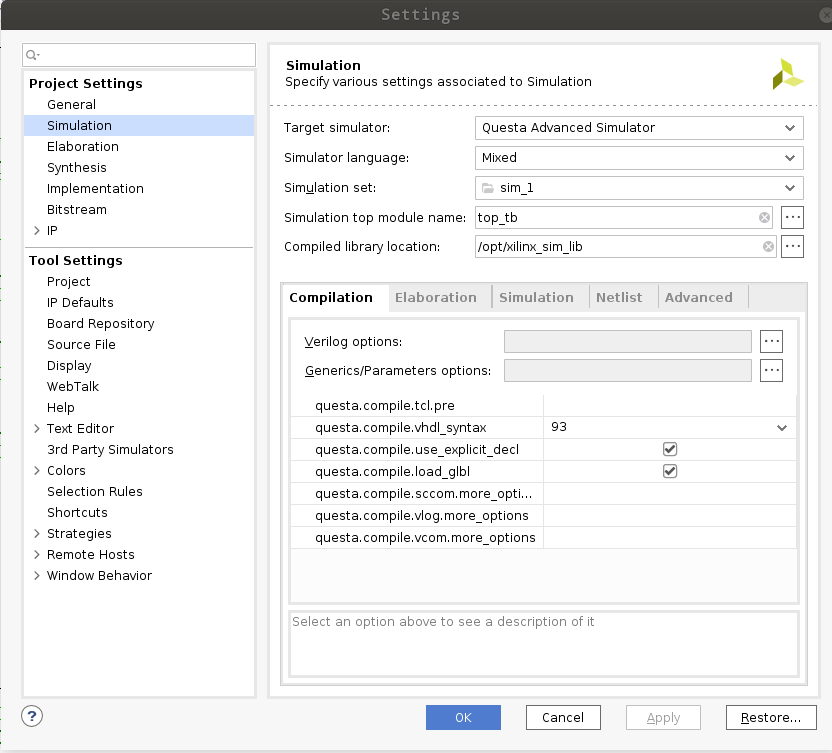

在弹出的对话框中,设置仿真工具为 Questasim、仿真语言为混合,当设计中用到vivado中自带的仿真工具时,还要指定器件库的路径,

设置好仿真参数后,如果设计文件和仿真文件也准备好,那么就可以开始对设计的功能进行仿真了。选择菜单“Flow”——>“Run Simulation”——>选相应的仿真类型或点击流程向导中的“Run Simulation”——>选相应的仿真类型进行仿真,

联合仿真

不知道为什么,我按照上面的配置完成之后,并不会出现仿真的界面,但是看log中应该是完成了全部的仿真流程的。

INFO: [Opt 31-138] Pushed 0 inverter(s) to 0 load pin(s).

Netlist sorting complete. Time (s): cpu = 00:00:00 ; elapsed = 00:00:00 . Memory (MB): peak = 8909.766 ; gain = 0.000 ; free physical = 127 ; free virtual = 2014

INFO: [Project 1-111] Unisim Transformation Summary:

A total of 1 instances were transformed.

IBUFGDS => IBUFDS: 1 instances

RTL Elaboration Complete: : Time (s): cpu = 00:00:15 ; elapsed = 00:00:10 . Memory (MB): peak = 8992.863 ; gain = 460.945 ; free physical = 143 ; free virtual = 1887

52 Infos, 156 Warnings, 0 Critical Warnings and 0 Errors encountered.

synth_design completed successfully

synth_design: Time (s): cpu = 00:00:17 ; elapsed = 00:00:13 . Memory (MB): peak = 8992.863 ; gain = 615.141 ; free physical = 142 ; free virtual = 1887

这时不会出现仿真界面。暂时还没找到什么好的解决办法。下面记录一下我临时的解决办法吧。

打开 Questasim

首先,vivado会把仿真相关的脚本,生成在<project_home>/<project_name>.sim/sim_1/behav/questa路径下,该路径下会存在三个关键脚本

# top_tb_compile.do

# top_tb_elaborate.do

# top_tb_simulate.do

# top_tb.udo

# top_tb_wave.do

在这个路径下在shell中输入vsim来启动仿真。

在打开的 Questasim 下方的console中输入

do top_tb_compile.do

返回

# ** Warning: (vlib-34) Library already exists at "questa_lib/work".

# ** Warning: (vlib-34) Library already exists at "questa_lib/msim".

# ** Warning: (vlib-34) Library already exists at "questa_lib/msim/xil_defaultlib".

# QuestaSim-64 vmap 10.7c Lib Mapping Utility 2018.08 Aug 17 2018

# vmap xil_defaultlib questa_lib/msim/xil_defaultlib

# Modifying modelsim.ini

# QuestaSim-64 vlog 10.7c Compiler 2018.08 Aug 17 2018

# Start time: 10:27:04 on Jun 16,2021

# vlog -64 -incr -work xil_defaultlib "+incdir+../../../../user_code/ip/pll" ../../../../user_code/ip/fifo_synchronize/sim/fifo_synchronize.v

# -- Skipping module fifo_synchronize

#

# Top level modules:

# fifo_synchronize

# End time: 10:27:04 on Jun 16,2021, Elapsed time: 0:00:00

# Errors: 0, Warnings: 0

# QuestaSim-64 vcom 10.7c Compiler 2018.08 Aug 17 2018

# Start time: 10:27:04 on Jun 16,2021

# vcom -64 -93 -work xil_defaultlib ../../../../user_code/ip/fir_LPF/sim/fir_LPF.vhd

# -- Loading package STANDARD

# -- Loading package TEXTIO

# -- Loading package std_logic_1164

# -- Loading package NUMERIC_STD

# -- Compiling entity fir_LPF

# -- Compiling architecture fir_LPF_arch of fir_LPF

# End time: 10:27:04 on Jun 16,2021, Elapsed time: 0:00:00

# Errors: 0, Warnings: 0

# QuestaSim-64 vlog 10.7c Compiler 2018.08 Aug 17 2018

# Start time: 10:27:04 on Jun 16,2021

# vlog -64 -incr -work xil_defaultlib "+incdir+../../../../user_code/ip/pll" ../../../../user_code/ip/pll/pll_clk_wiz.v ../../../../user_code/ip/pll/pll.v ../../../../user_code/adc.v ../../../../user_code/adc_top.v ../../../../user_code/delay_driver_syn.v ../../../../user_code/fir_ip_top.v ../../../../user_code/phase_difference_measure.v ../../../../user_code/sync_fsm.v ../../../../user_code/synchronize.v ../../../../user_code/top.v ../../../../user_code/top_tb.v

# -- Skipping module pll_clk_wiz

# -- Skipping module pll

# -- Skipping module adc

# -- Skipping module adc_top

# -- Skipping module delay_driver_syn

# -- Skipping module fir_ip_top

# -- Skipping module phase_difference_measure

# -- Skipping module ff_zero_

# -- Skipping module Phase_sample_clk

# -- Skipping module ForeheadJudgment

# -- Skipping module sync_fsm

# -- Skipping module synchronize

# -- Skipping module top

# -- Skipping module top_tb

#

# Top level modules:

# top_tb

# End time: 10:27:04 on Jun 16,2021, Elapsed time: 0:00:00

# Errors: 0, Warnings: 0

# QuestaSim-64 vlog 10.7c Compiler 2018.08 Aug 17 2018

# Start time: 10:27:04 on Jun 16,2021

# vlog -work xil_defaultlib glbl.v

# -- Compiling module glbl

#

# Top level modules:

# glbl

# End time: 10:27:04 on Jun 16,2021, Elapsed time: 0:00:00

# Errors: 0, Warnings: 0

因为之前在vivado生成仿真文件的时候,会自动执行一遍,所以log里面有大量的skip,可以节约时间。

再输入

do top_tb_simulation.do

熟悉的仿真界面就会出现。

结尾

挖坑,有时间研究一下这个调用的具体流程,看能不能更加方便一些。

浙公网安备 33010602011771号

浙公网安备 33010602011771号