MIG IP学习笔记

一、DDR3基础知识介绍

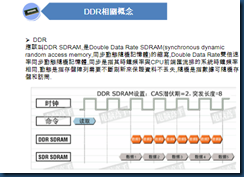

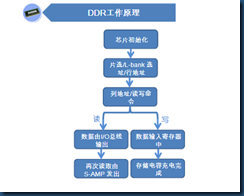

1、DDR基本原理介绍

参考文档:《DDR3基础知识介绍》

2、关键时序参数的介绍

参考文档:《DDR3详解(以Micron MT41J128M8 1Gb DDR3 SDRAM为例)》

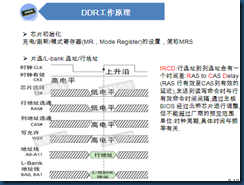

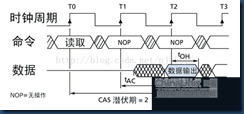

1)tRCD的概念:

在实际工作中,Bank地址与相应的行地址是同时发出的,此时这个命令称之为“行激活”(Row Active)。在此之后,将发送列地址寻址命令与具体的操作命令(是读还是写),这两个命令也是同时发出的,所以一般都会以“读/写命令”来表示列寻址。根据相关的标准,从行有效到读/写命令发出之间的间隔被定义为tRCD,即RAS to CAS Delay(RAS至CAS延迟,RAS就是行地址选通脉冲,CAS就是列地址选通脉冲),我们可以理解为行选通周期。tRCD是DDR的一个重要时序参数,广义的tRCD以时钟周期(tCK,Clock Time)数为单位,比如tRCD=3,就代表延迟周期为两个时钟周期,具体到确切的时间,则要根据时钟频率而定,DDR3-800,tRCD=3,代表30ns的延迟。

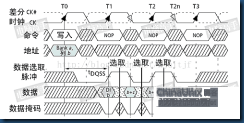

图中显示的是tRCD=3

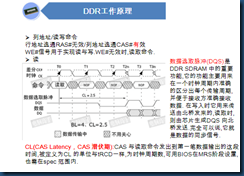

2)CL和tAC的概念

接下来,相关的列地址被选中之后,将会触发数据传输,但从存储单元中输出到真正出现在内存芯片的 I/O 接口之间还需要一定的时间(数据触发本身就有延迟,而且还需要进行信号放大),这段时间就是非常著名的 CL(CAS Latency,列地址脉冲选通潜伏期)。CL 的数值与 tRCD 一样,以时钟周期数表示。如 DDR3-800,时钟频率为 100MHz,时钟周期为 10ns,如果 CL=2 就意味着 20ns 的潜伏期。不过CL只是针对读取操作。

由于芯片体积的原因,存储单元中的电容容量很小,所以信号要经过放大来保证其有效的识别性,这个放大/驱动工作由S-AMP负责,一个存储体对应一个S- AMP通道。但它要有一个准备时间才能保证信号的发送强度(事前还要进行电压比较以进行逻辑电平的判断),因此从数据I/O总线上有数据输出之前的一个时钟上升沿开始,数据即已传向S-AMP,也就是说此时数据已经被触发,经过一定的驱动时间最终传向数据I/O总线进行输出,这段时间我们称之为 tAC(Access Time from CLK,时钟触发后的访问时间)。

图中标准CL=2,tAC=1

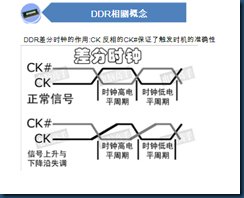

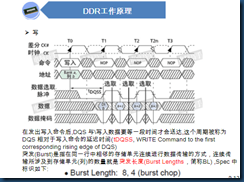

3)DQS的概念

DQS 是DDR中的重要功能,它的功能主要用来在一个时钟周期内准确的区分出每个传输周期,并便于接收方准确接收数据。每一颗芯片都有一个DQS信号线,它是双向的,在写入时它用来传送由北桥发来的DQS信号,读取时,则由芯片生成DQS向北桥发送。完全可以说,它就是数据的同步信号。

在读取时,DQS与数据信号同时生成(也是在CK与CK#的交叉点)。而DDR内存中的CL也就是从CAS发出到DQS生成的间隔,DQS生成时,芯片内部的预取已经完毕了,由于预取的原因,实际的数据传出可能会提前于DQS发生(数据提前于DQS传出)。由于是并行传输,DDR内存对tAC也有一定的要求,对于DDR266,tAC的允许范围是±0.75ns,对于DDR333,则是±0.7ns,有关它们的时序图示见前文,其中CL里包含了一段DQS 的导入期。

DQS 在读取时与数据同步传输,那么接收时也是以DQS的上下沿为准吗?不,如果以DQS的上下沿区分数据周期的危险很大。由于芯片有预取的操作,所以输出时的同步很难控制,只能限制在一定的时间范围内,数据在各I/O端口的出现时间可能有快有慢,会与DQS有一定的间隔,这也就是为什么要有一个tAC规定的原因。而在接收方,一切必须保证同步接收,不能有tAC之类的偏差。这样在写入时,芯片不再自己生成DQS,而以发送方传来的DQS为基准,并相应延后一定的时间,在DQS的中部为数据周期的选取分割点(在读取时分割点就是上下沿),从这里分隔开两个传输周期。这样做的好处是,由于各数据信号都会有一个逻辑电平保持周期,即使发送时不同步,在DQS上下沿时都处于保持周期中,此时数据接收触发的准确性无疑是最高的。

3、内存频率和容量

1)关于内存频率的介绍

参考文档:《内存工作频率与带宽》

链接:https://wenku.baidu.com/view/065565ad9b6648d7c0c7464b.html

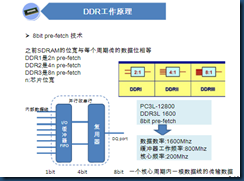

以DDR3 1600为例

1)颗粒核心频率:Fcore=200Mhz

2)工作频率:Fwork=Fcorex2 = 400Mhz

3)等效频率:Feq=Fworkx4= 1600Mhz

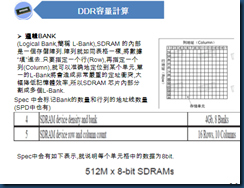

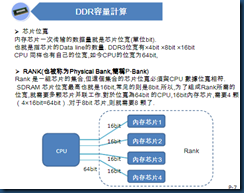

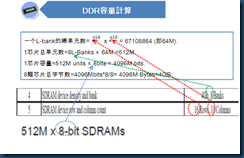

2、内存容量

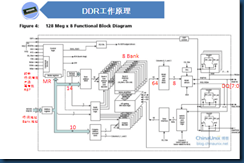

参考文档《MT41K256M16 Datasheet - Micron Technology》

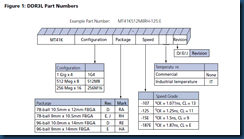

1)DDR型号介绍

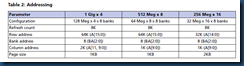

2)寻址介绍

、

、

上图中Meg的意思是M(兆,也就是1K*1K)

128 Meg x 4 x 8 banks 意思是一个BANK有128M个单元,每个单元为4bit,

总共8个bank,因此总存储量为4Gb。

二、DDR3仿真学习

1、在ISE中仿真

参考文档:《xilinx平台DDR3设计教程之仿真篇》

1)使用ISE新建工程ddrex,然后打开工程添加MIG ip,如教程配置.

2)然后打开ipcore文件夹下面由ISE软件自动生成的example工程:migex

3)然后添加以下路径的文件,使其成为一个可综合的example工程

4)然后添加以下路径的verilog文件,进行仿真

5)运行仿真

差不多运行1.1ms后初始化才成功,也就是init_calib_complete才拉高

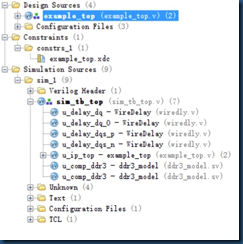

2、在Vivado中仿真DDR3

1、在IP核配置界面会默认选择AXI Interface,而且不可以被用户取消。

2、要先配置好参数,生成IP核后,再使用open example design这样example design才会按照你所配置的参数进行工作

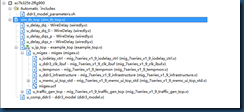

3、在vivado中进行打开example design后直接就可以运行仿真,不需要手动添加文件,如下图所示,图片来自《米联客ZYNQ FPGA修炼秘籍-基于MIZ7035 开发板-第七季MIG 内存控制器的使用》

三、参考资料

1、《DDR3基础知识介绍》

2、《内存工作频率与带宽》

3、《MT41K256M16 Datasheet - Micron Technology》

4、《xilinx平台DDR3设计教程之仿真篇》

5、《第七季MIG 内存控制器的使用》

6、《米联客ZYNQ FPGA修炼秘籍-基于MIZ7035 开发板-第七季MIG 内存控制器的使用》