计算机组成原理

计算机五大部件为控制器、运算器CPU、存储器RAM ROM、输入设备、输出设备。

一定不属于冯•诺依曼机体系结构必要组成部分的是()(单选) A、ROM B、CPU C、Cache D、RAM

参考答案:C

第二章-数据的表示和运算

CPU的性能指标

评价计算机性能指标

- MIPS——每秒处理的百万级的机器语言指令数,这是衡量CPU速度的一个指标 =CPI/主频

- CPI——计算机执行一条指令所需的时钟周期数,用于衡量计算机的运算速度

- IPC——CPU每一时钟周期内所执行的指令多少 =1/CPI

- 字长——决定了CPU的数据处理能力和寻址范围

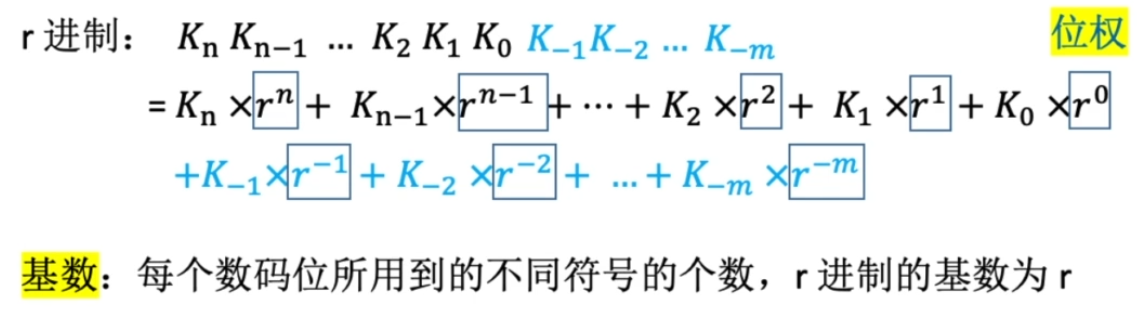

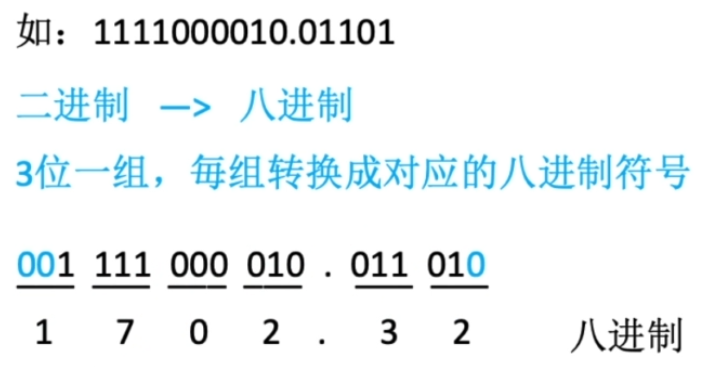

进制转换

如果某系统15*4=112成立,则系统采用的进制是6

(p + 5) * 4 = p^2 + p + 2

二进制是Binary,简写为B。

八进制是Octal,简写为O。

十进制为Decimal,简写为D。

十六进制为Hexadecimal,简写为H。

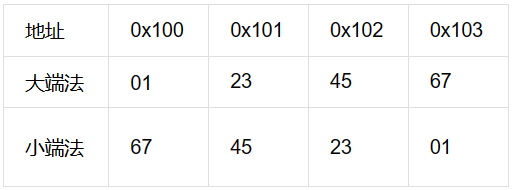

大端存储和小段存储

假设变量x类型为int,位于地址0x100处,x = 0x01234567.地址范围为0x100~0x103的字节 左边为数据高位,右边为低位

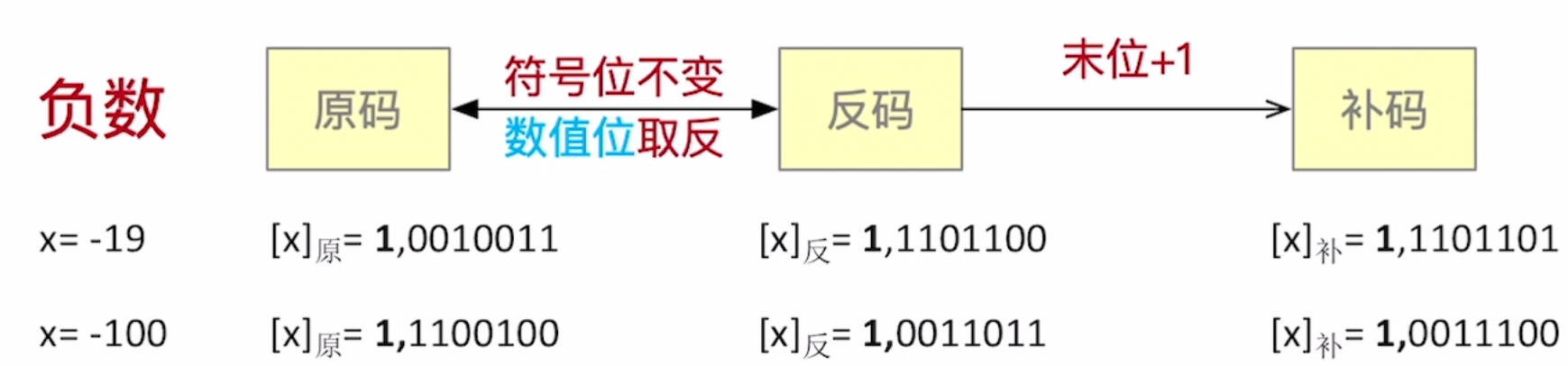

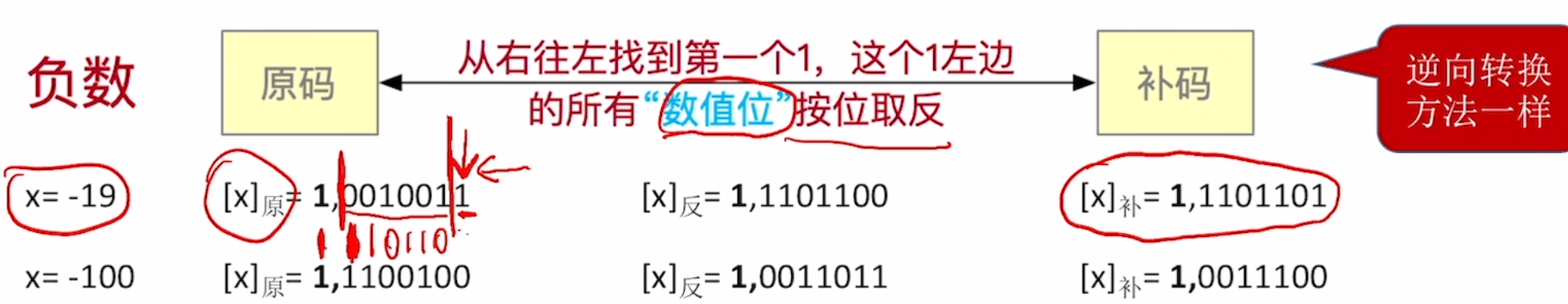

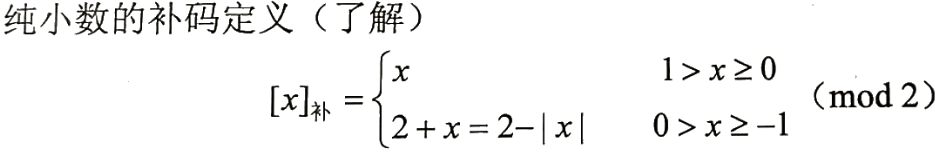

原反补码

1.

正数原反补码相同

负数 反码:符号位不变,数值位取反 补码:反码末位+1

2.*原码补码速换

8bit原码范围[-127,+127] 补码[-128,+127]

3.

算数逻辑移位

原码:正负数补0 反码:正数补0,负数补1 补码:正数补0,负数右移补1,左移补0

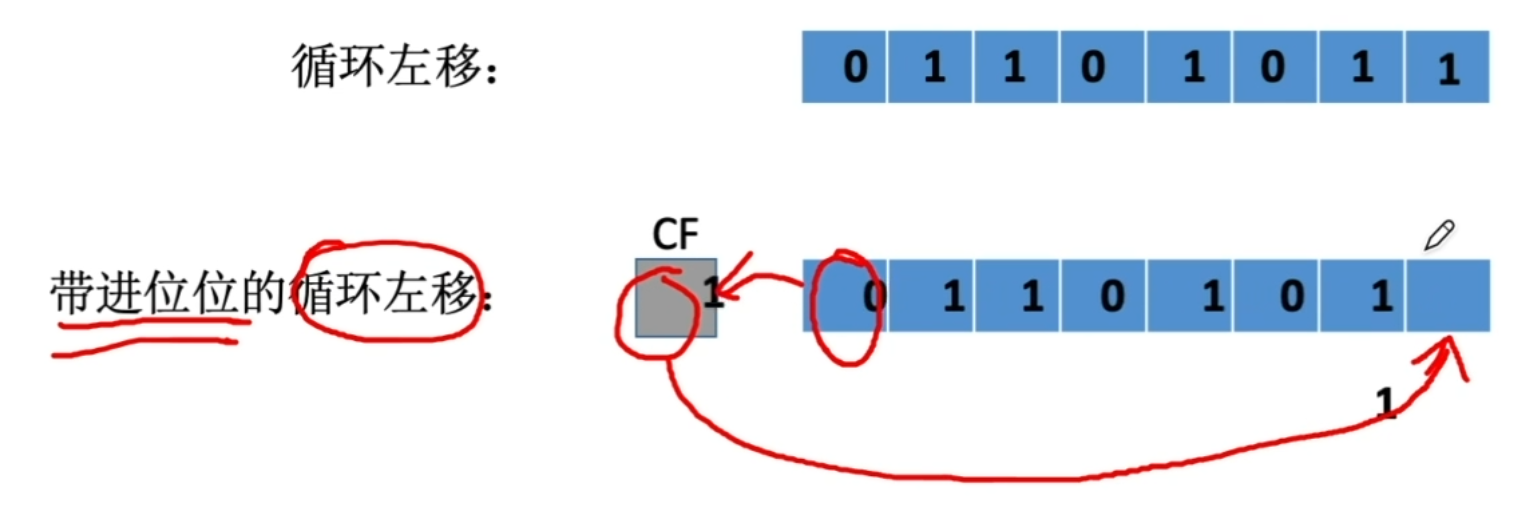

循环移位:

在 CPU 中执行算术右移指令的操作过程采用 操作数的符号位保持不变,各位顺次右移1位,最低位移至进位标志位中。

执行逻辑右移指令的操作过程是 操作数的符号位填0,各位顺次右移1位,最低位移至进位标志位中。

执行算术左移指令和逻辑左移指令的操作过程是 最低位填0,各位顺次左移1位,操作数的符号位移至进位标志位中

乘法运算

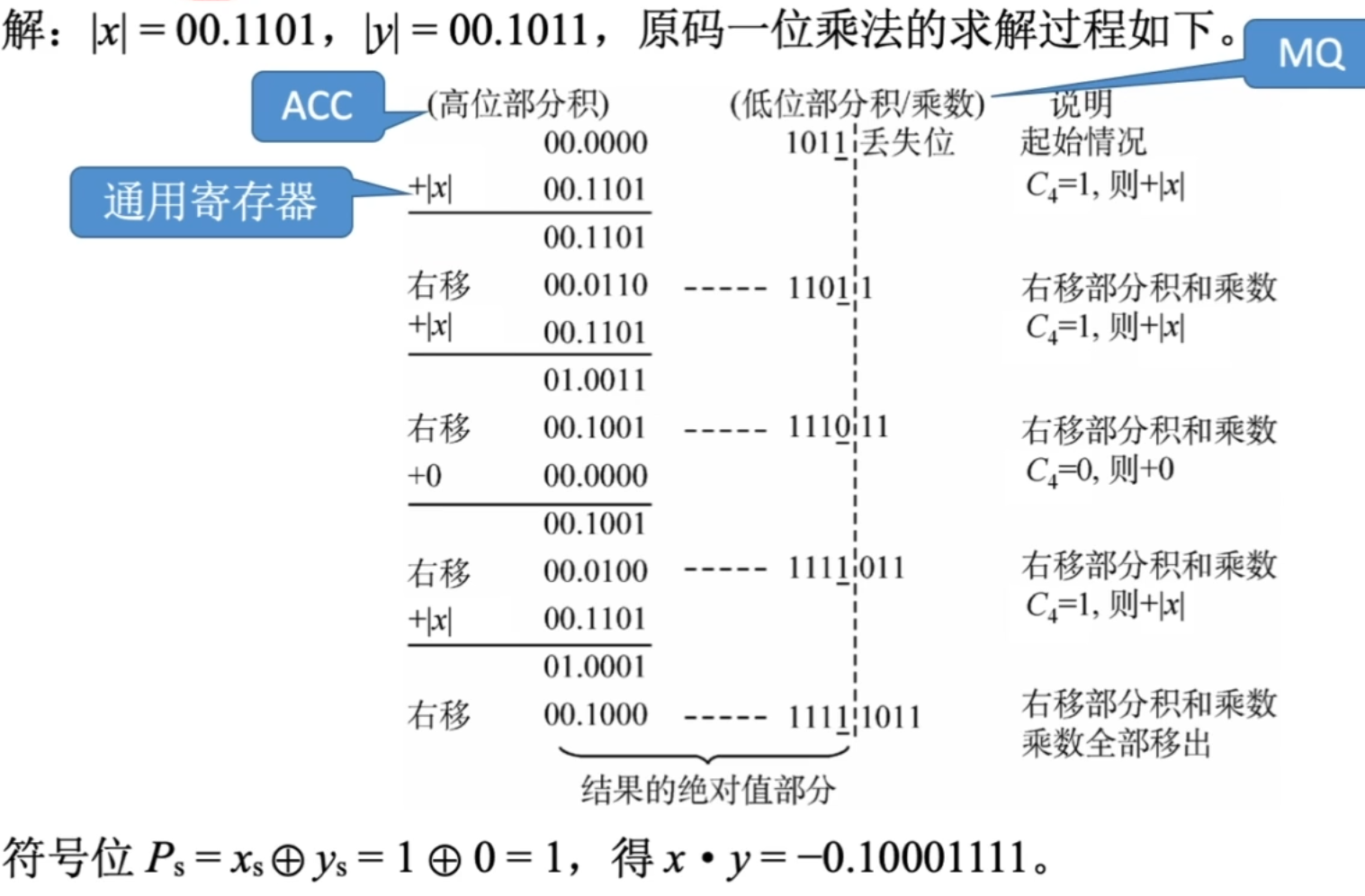

原码一位乘法

乘法过程中共执行 n -1次算术右移和 n-1 次加法运算

两个原码数相乘,其乘积的符号为两数符号的异或值,数值为两数绝对值之积

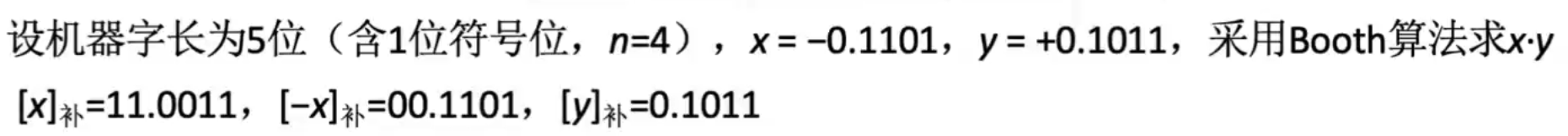

补码一位乘法

乘法过程中共执行n 次加法和n-1 部分积右移

算到符号位参与运算(多一次运算,不移位)

01 +[x]补 10 +[-x]补(前一位为MQ中“最低位”,后一位为辅助位) 00/11 +0

除法运算

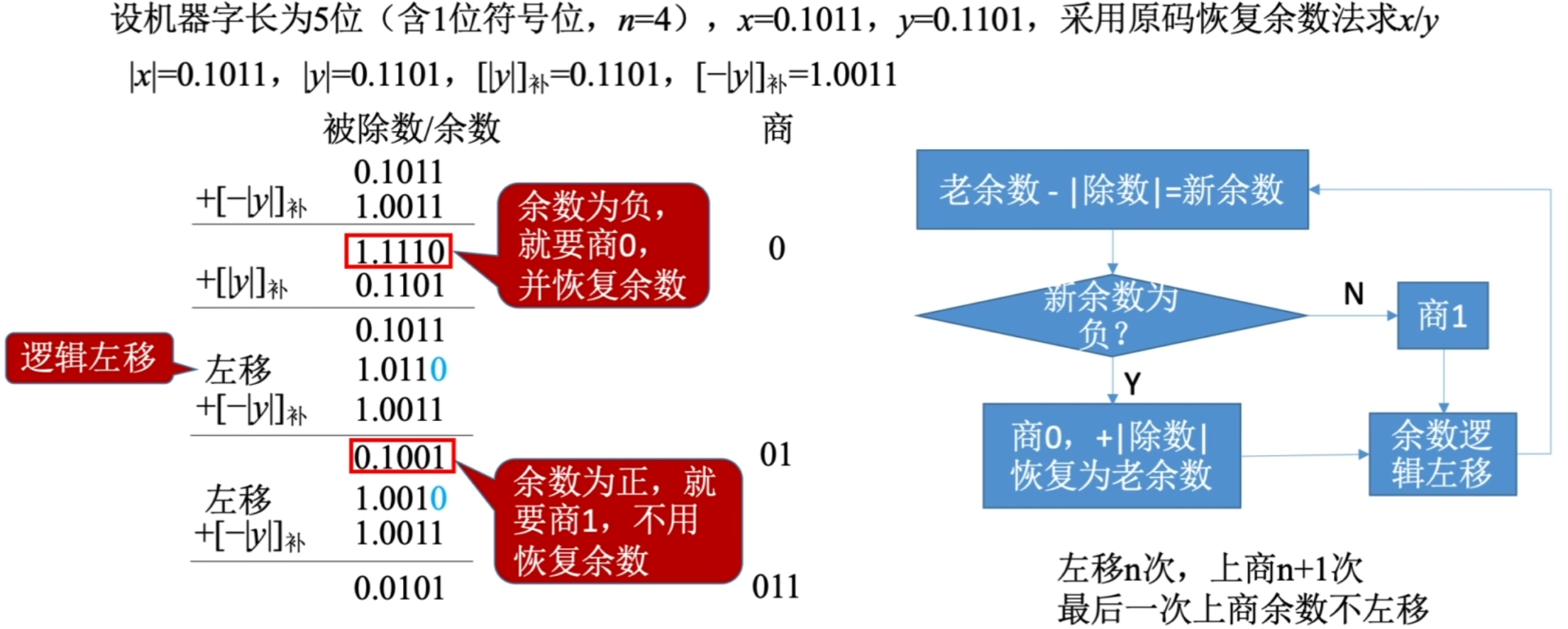

原码除法:恢复余数法

两个原码数相除,其商的符号为两数符号的异或值,数值为两数绝对值相除后的结果

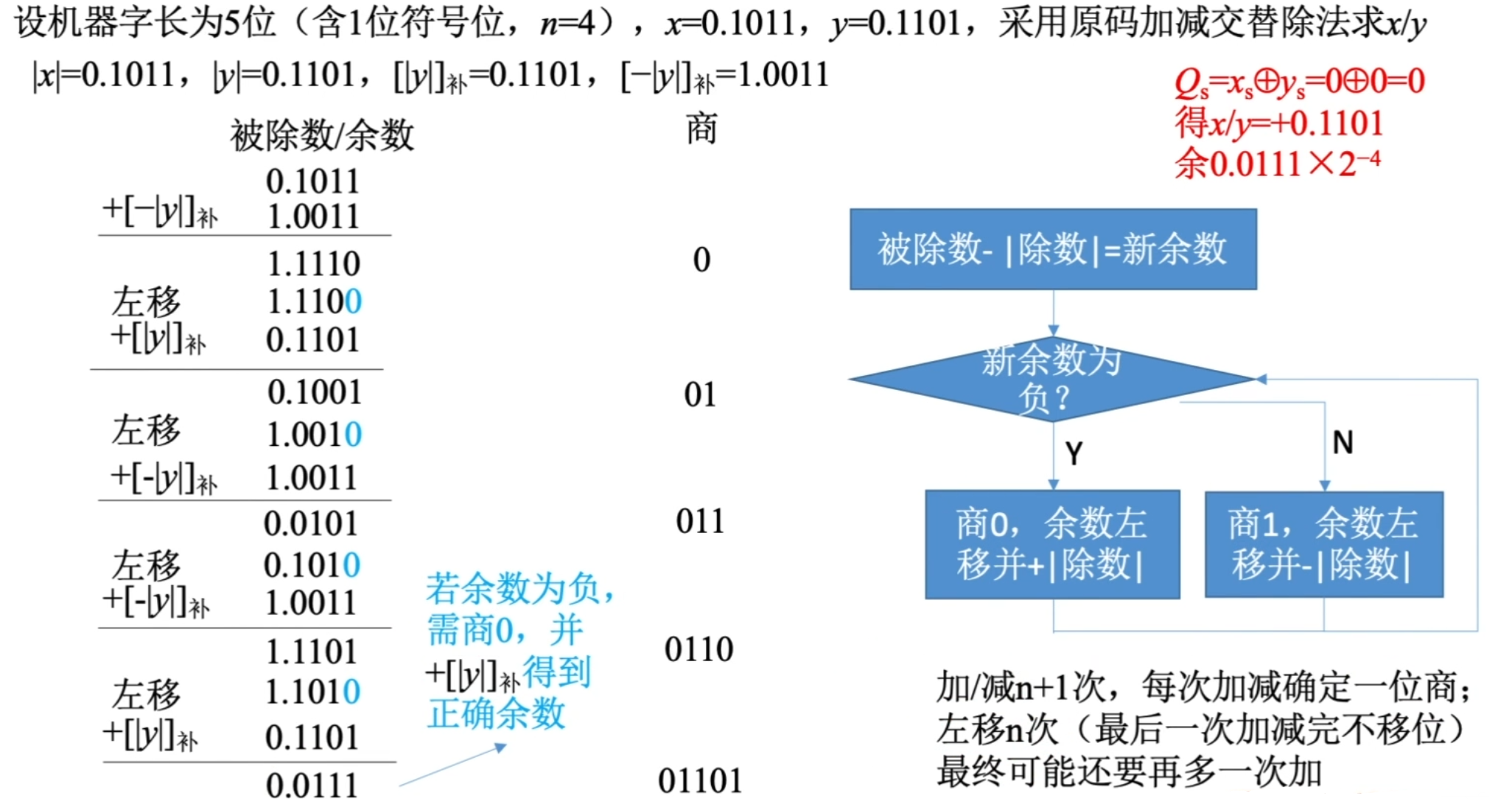

原码除法:加减交替法

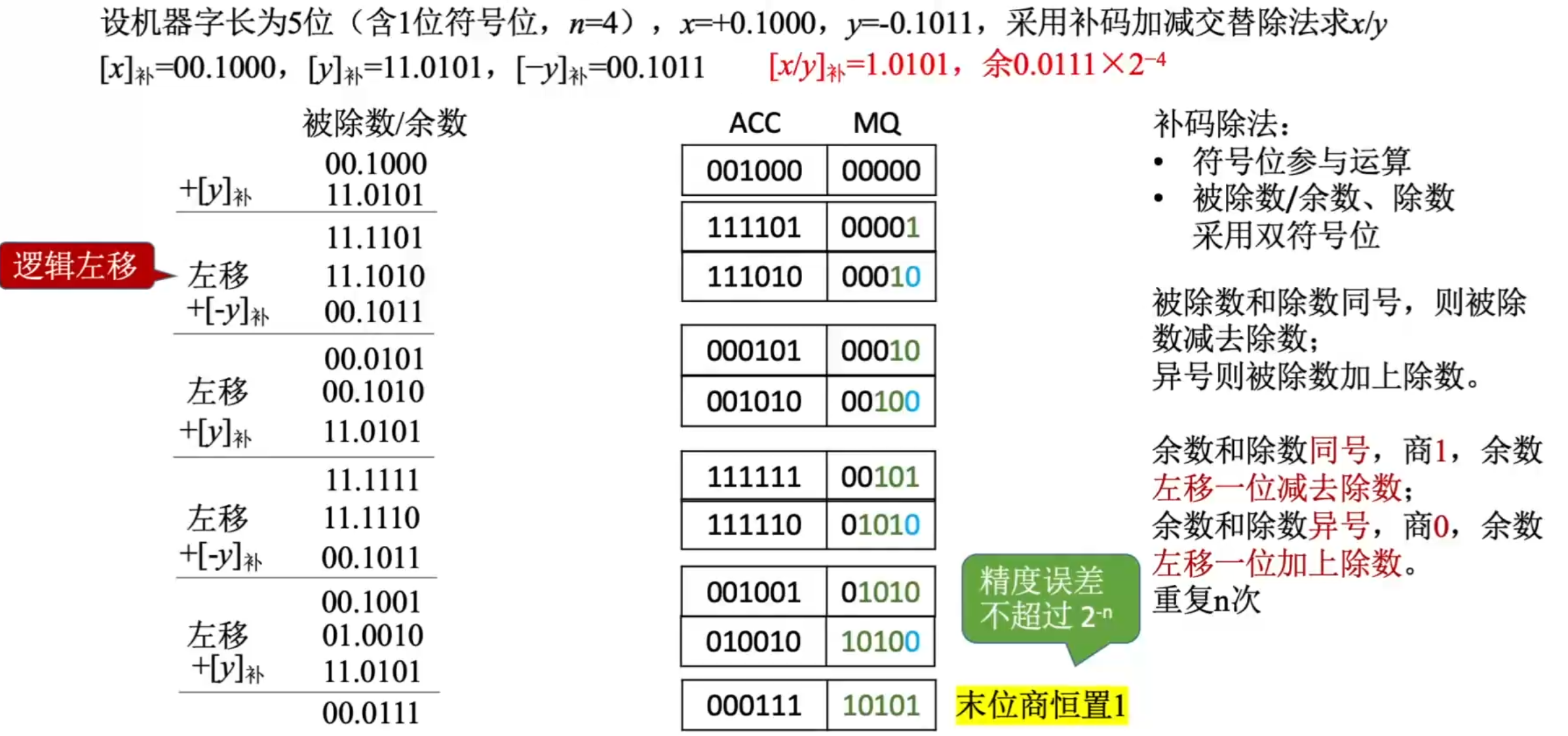

补码除法:加减交替法

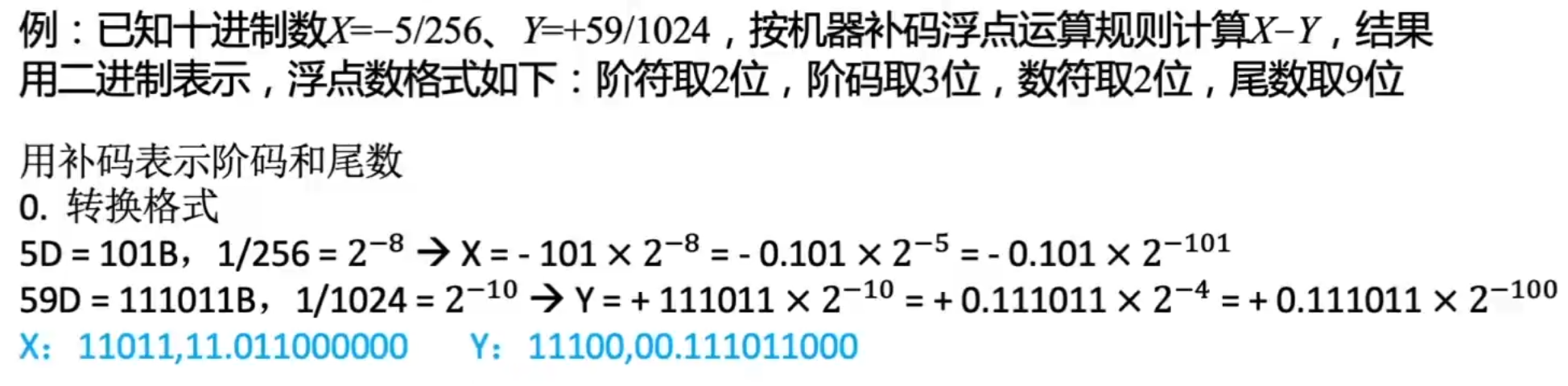

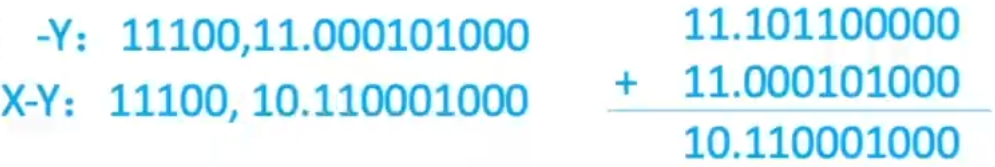

5浮点数加减运算

①对阶

小阶向大阶看齐

![]()

②尾数加减

10下溢,01上溢

③规格化

右规:尾数过大,导致两个符号位不同——尾数右移1位,阶码加一

左规:尾数最高数值位与符号位相同(0.0xxx/1.1xxx)——连续左移直至最高符号位与符号位不同,阶码相应相减

![]()

右移,阶码加1

④舍入

0舍1入 因规格化右移舍末尾尾数,若非0,则进1

若尾数再次溢出,则再次右规

⑤判溢出

阶码不能超过2位

m表示符号位是否进位(进位为1,否则为0)

n表示最高数值位是否进位(进位为1,否则为0)

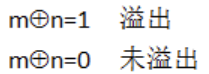

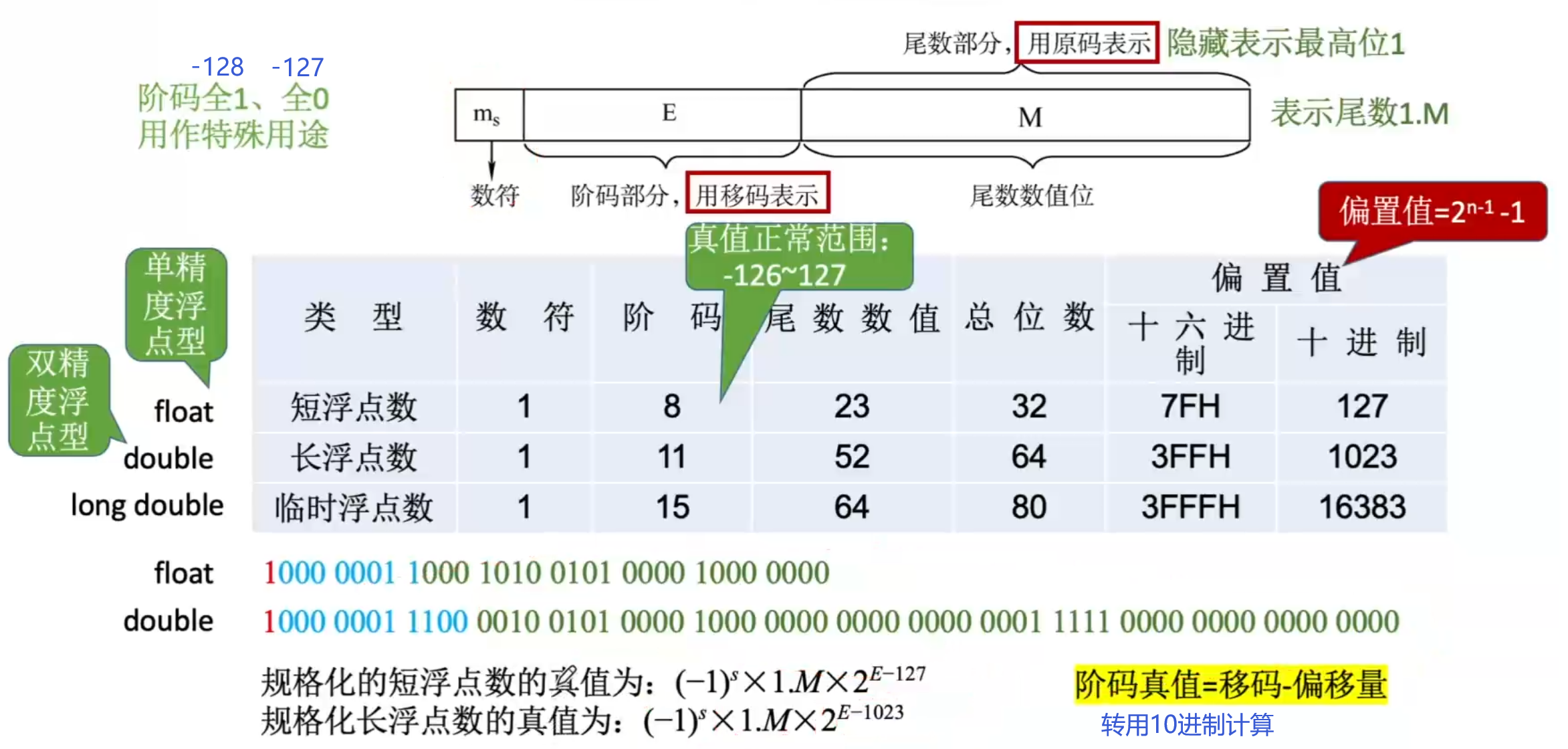

移码 IEEE754浮点数

与补码范围相同补码[-128,+127]

移码:补码符号取反 (真值+偏置值(此处为1000 0000B))

IEEE754标准 偏置值为原偏置值-1(1000 0000→ 0111 1111)

阶码用移码 尾数用原码

原移码-1

一个32位的二进制数分为三个部分:

- 符号位S:最高位,表示正负号,0为正,1为负。

- 阶码E:中间8位,表示指数部分,偏移量为127。

- 尾数M:最低23位,表示小数部分,采用隐含最高位为1的方法。

x = (-1)^S * (1.M) * 2^(E-127)

e.g.

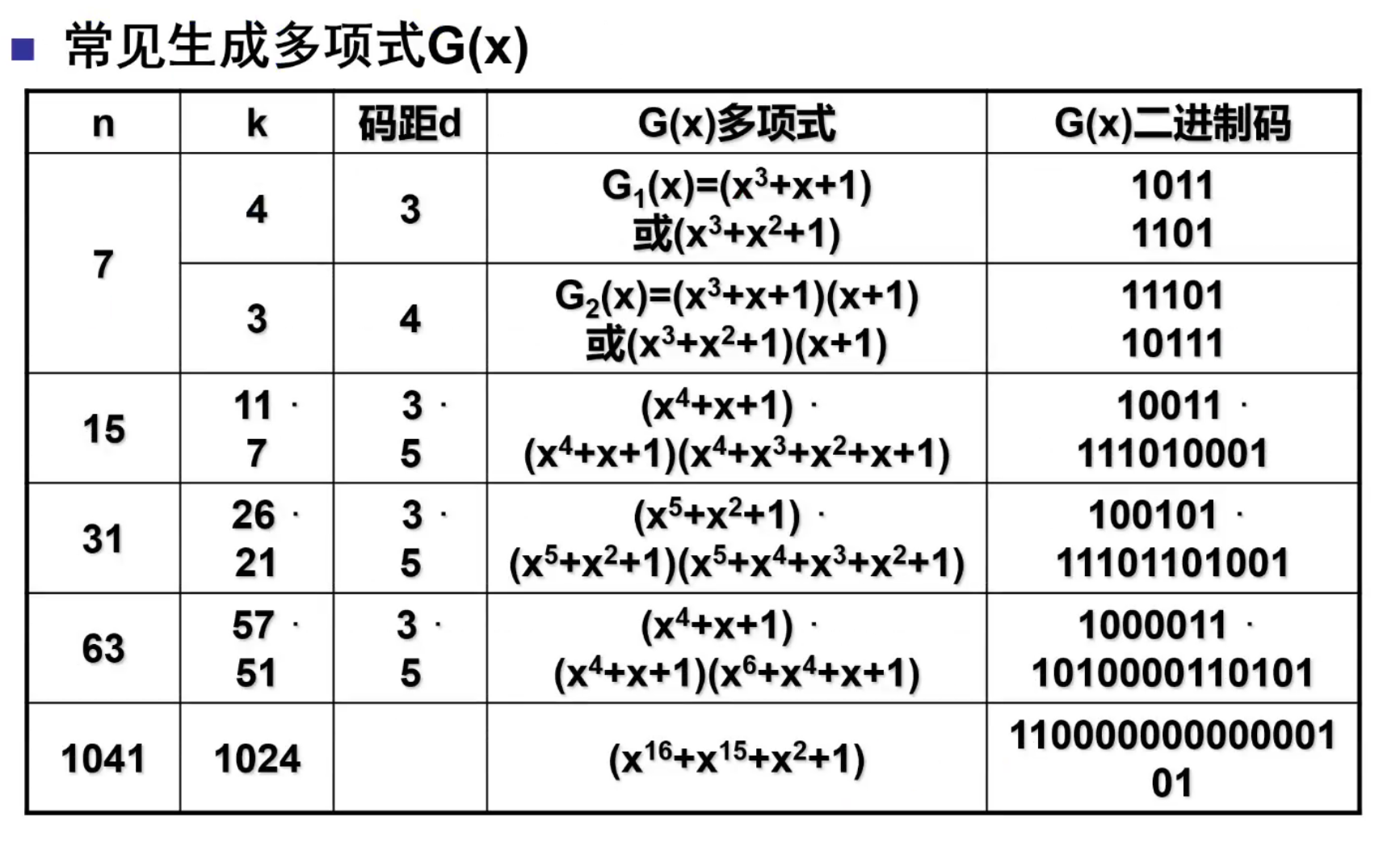

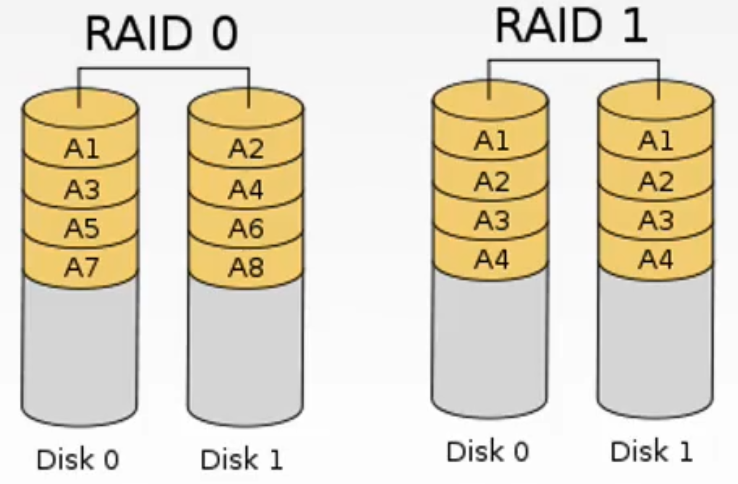

6数据校验码

将有效信息按某种规律分成若干组,每组安排一个校验位,做奇偶测试,就能提供多位检错信息,以指出最大可能是哪位出错,从而将其纠正。实质上,海明校验是一种多重校验增加校验的同时也增大了码距分成r组时,可以得到r位指误码,因此可以区分(2^r-r)种只有1位出错的情况

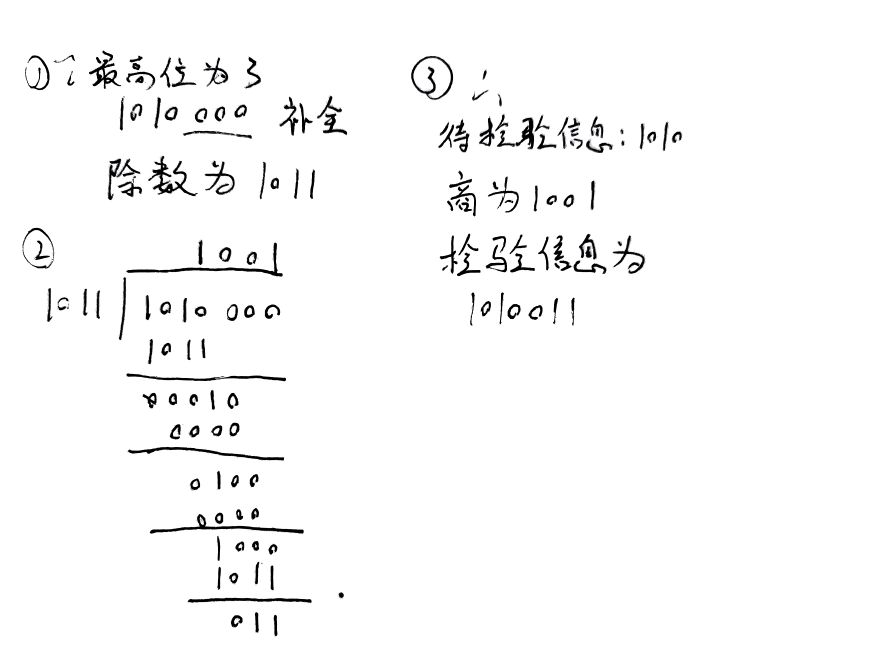

CRC循环冗余校验码

2^r ≥ k + r + 1

已知被检信息为1010,选择的生成多项式是G(X)为X3+X1+ X0,求CRC校验码(多项式和被检信息由题目给定

第三章-存储系统

ROM外存 RAM内存

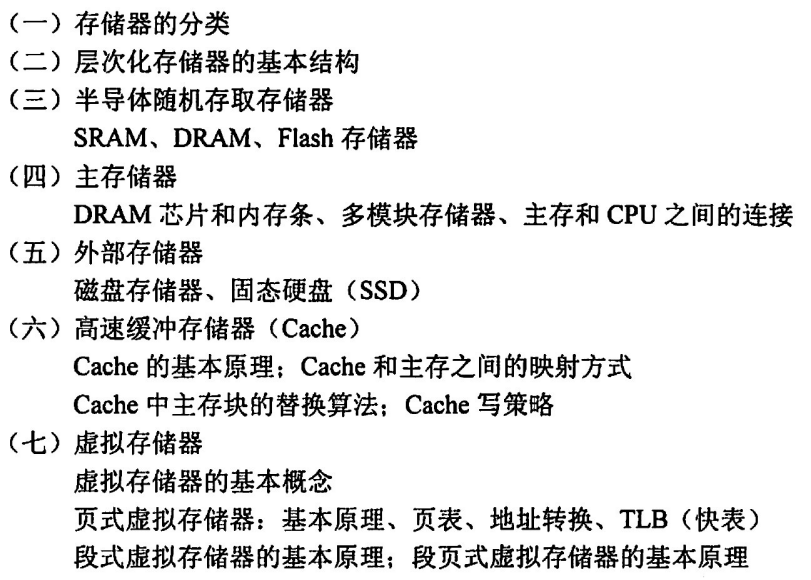

1主存储器的基本组成

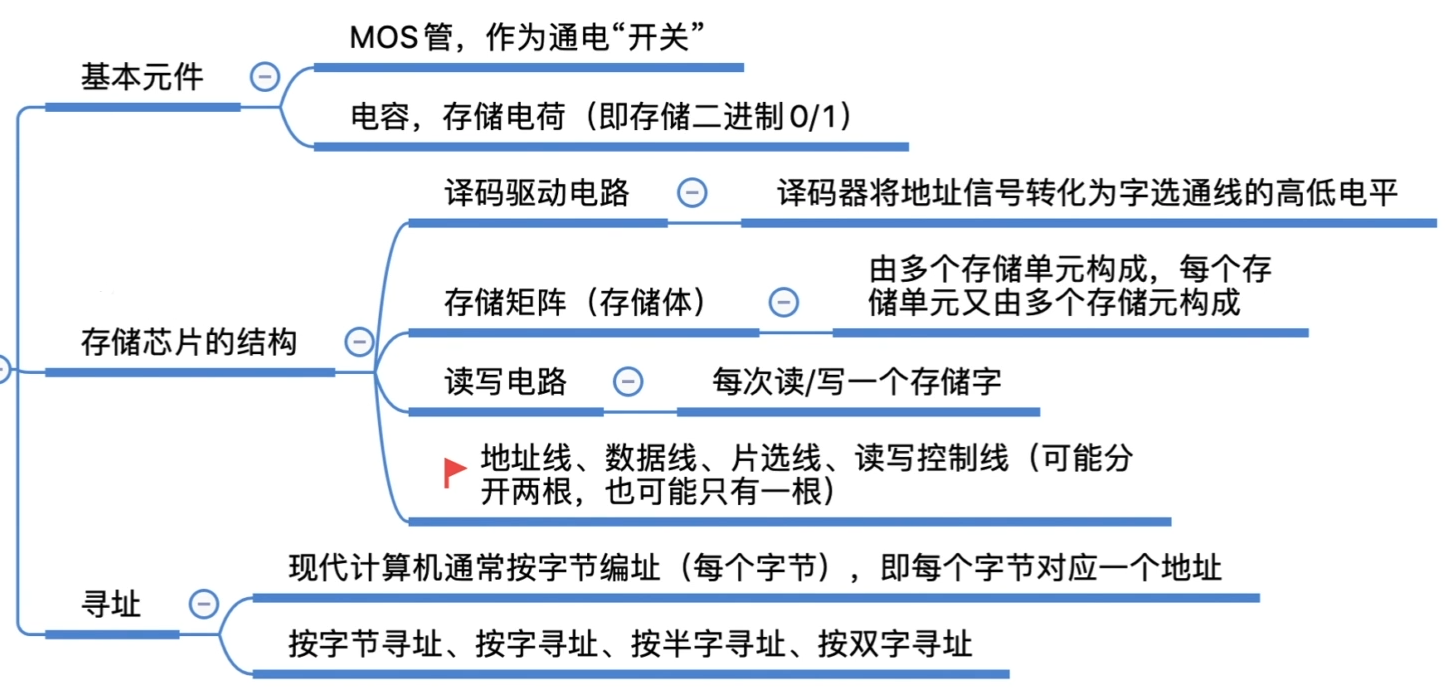

2 SRAM&DRAM

DRAM-主存 SRAM-Cache

64K*8位的动态存储器DRAM存储芯片,数据线为8,地址线行列共用为16/2,之和为16

16K*32位的静态储存器SRAM存储芯片,其数据线和地址线之和为46 其内部采用位数相同的行列地址译码器,则其内部译码输出线的总量为2^7+2^7=2^8

DRAM 比SRAM慢的原因

- DRAM需要刷新操作

- DRAM读写过程中其地址分行、列分时传送

- DRAM读操作前先要进行预充操作

- DRAM存储单元采用了双译码结构

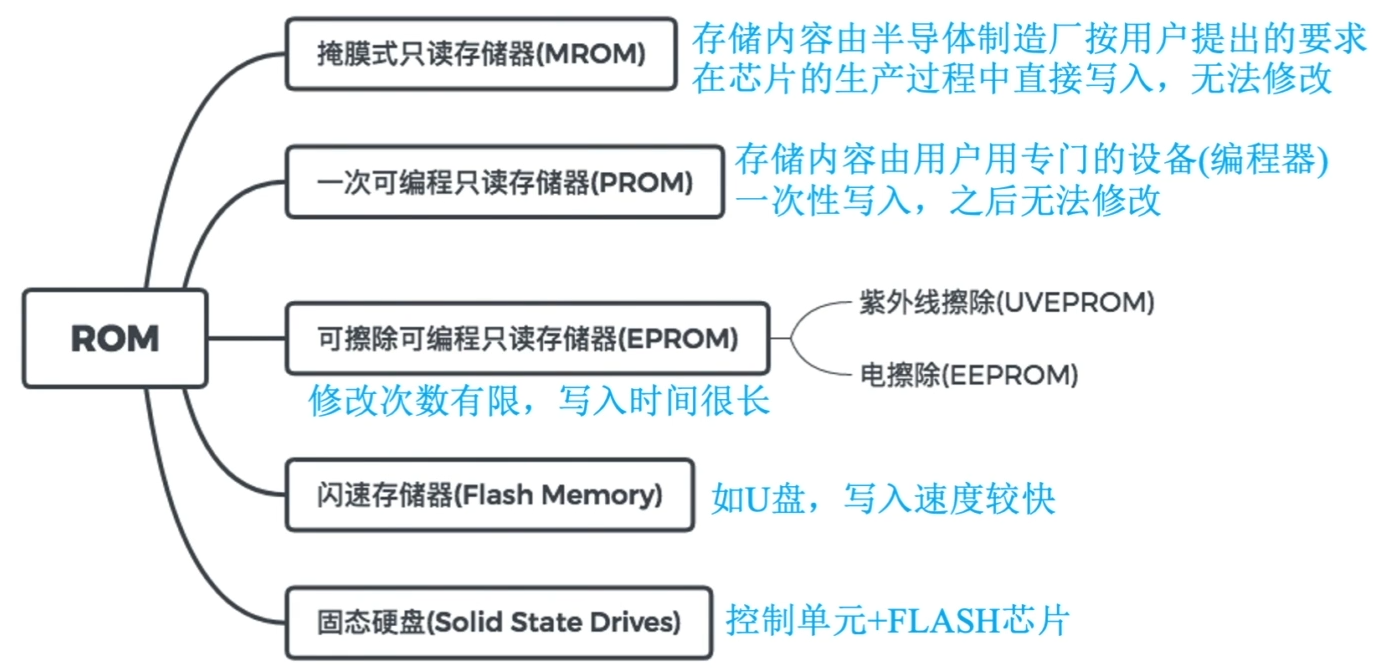

3 ROM只读储存器

可随机存取

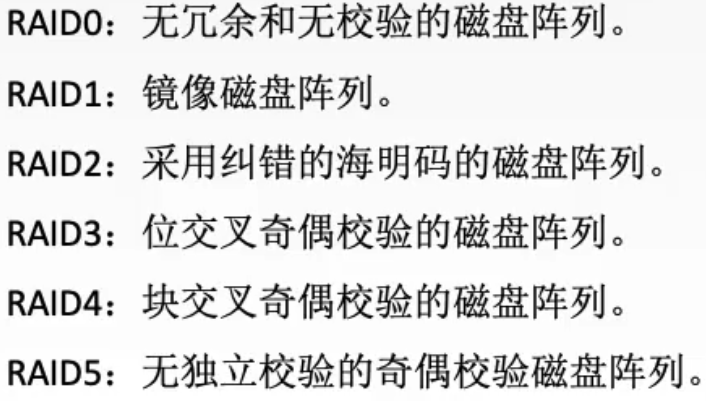

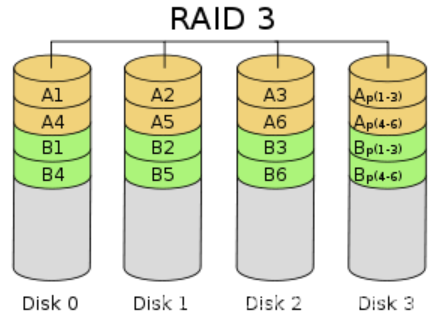

磁盘阵列RAID

至少磁盘数:

- 2:RAID0、RAID1、RAID4

- 3:RAID3、RAID5

- 4:RAID10

RAID 10(又叫RAID 1+0)特点:

- 最少需要4块磁盘

- 先按RAID 0分成两组,再分别对两组按RAID 1方式镜像

- 兼顾冗余(提供镜像存储)和性能(数据条带形分布)

- 在实际应用中较为常用

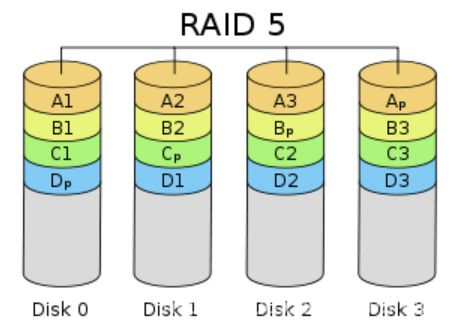

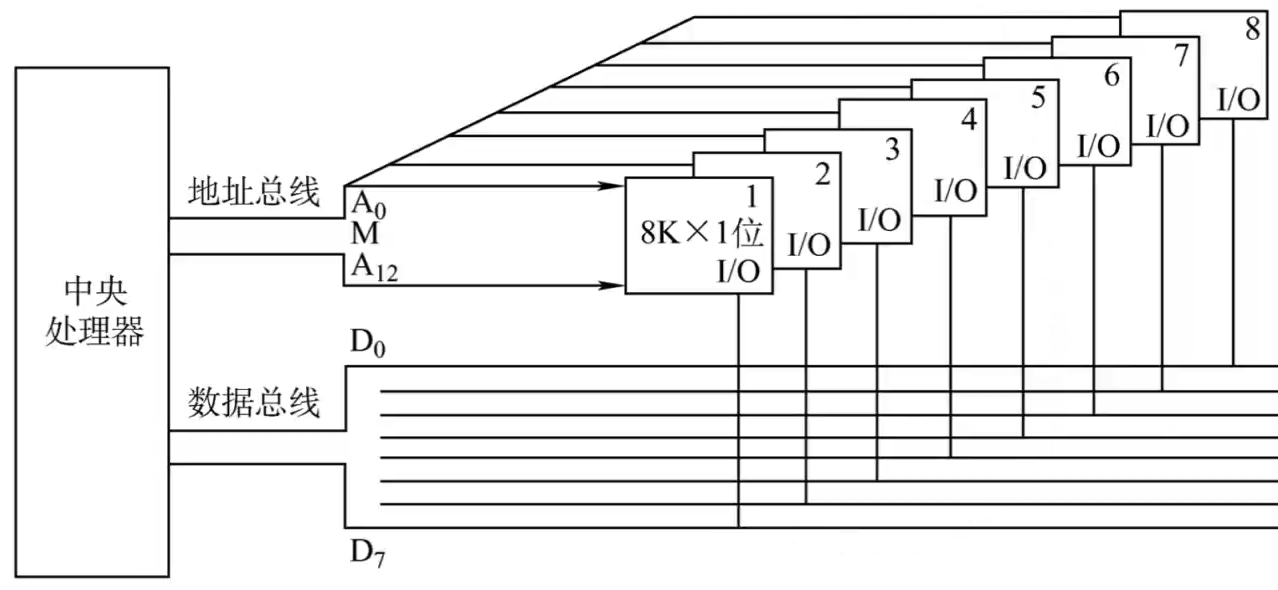

4主存储器与CPU的连接

字扩展

扩展寻址能力

用片选信号(接译码器)进行选择不同芯片

位扩展

扩展位数

字位同时扩展

位扩展4*2=8位 字扩展16*8=128K

5 Cache基本概念和原理

CPU-CaChe-内存-外存

Cache集成在CPU内,用SRAM实现 主存与Cache之间以“块”为单位进行数据交换

局部性原理

- 空间局部性——未来使用的信息可能是与现在正在使用的信息在空间上邻近的信息,数组

- 时间局部性——未来使用的信息可能是现在正在使用的信息,for循环

性能分析

- 命中率H——CPU访问的信息在Cache中的比率

- 缺失率M——1-H

- 平均访问时间——t = H*访问一次Cache时间+(1-H)(访问一次Cache时间*访问一次主存时间)

- 或t = H*访问一次Cache时间+(1-H)*访问一次主存时间

先访问Cache,未命中再访问主存

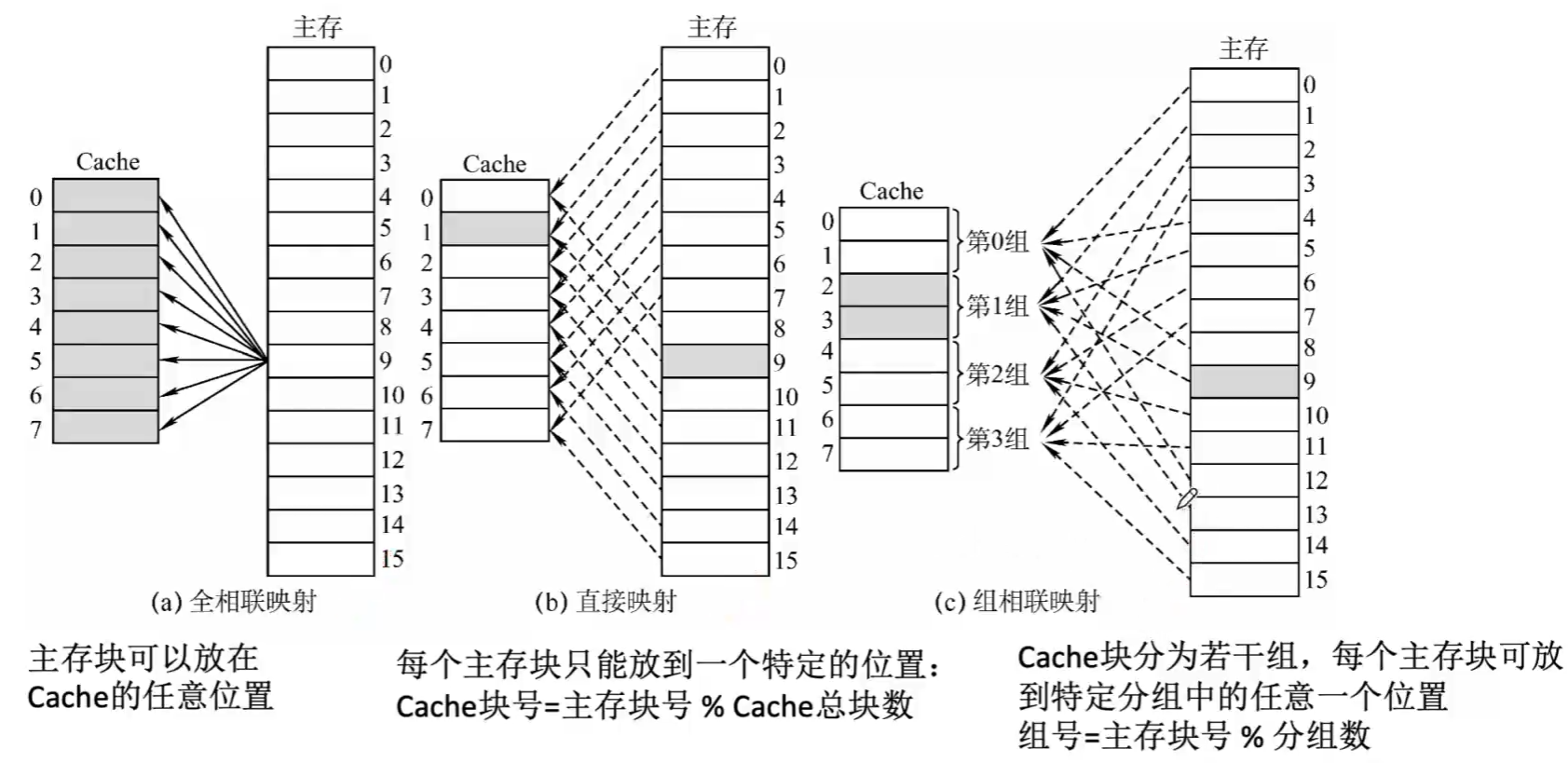

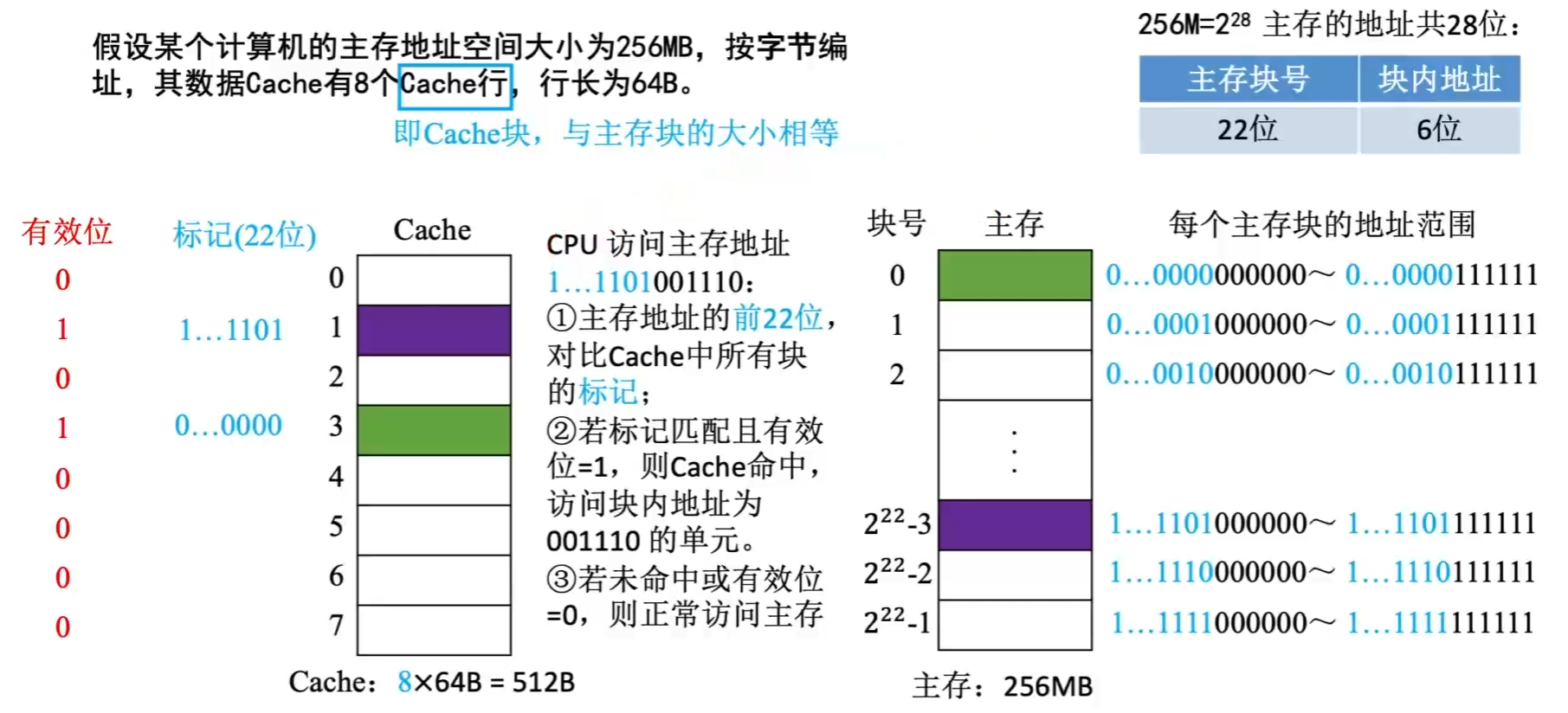

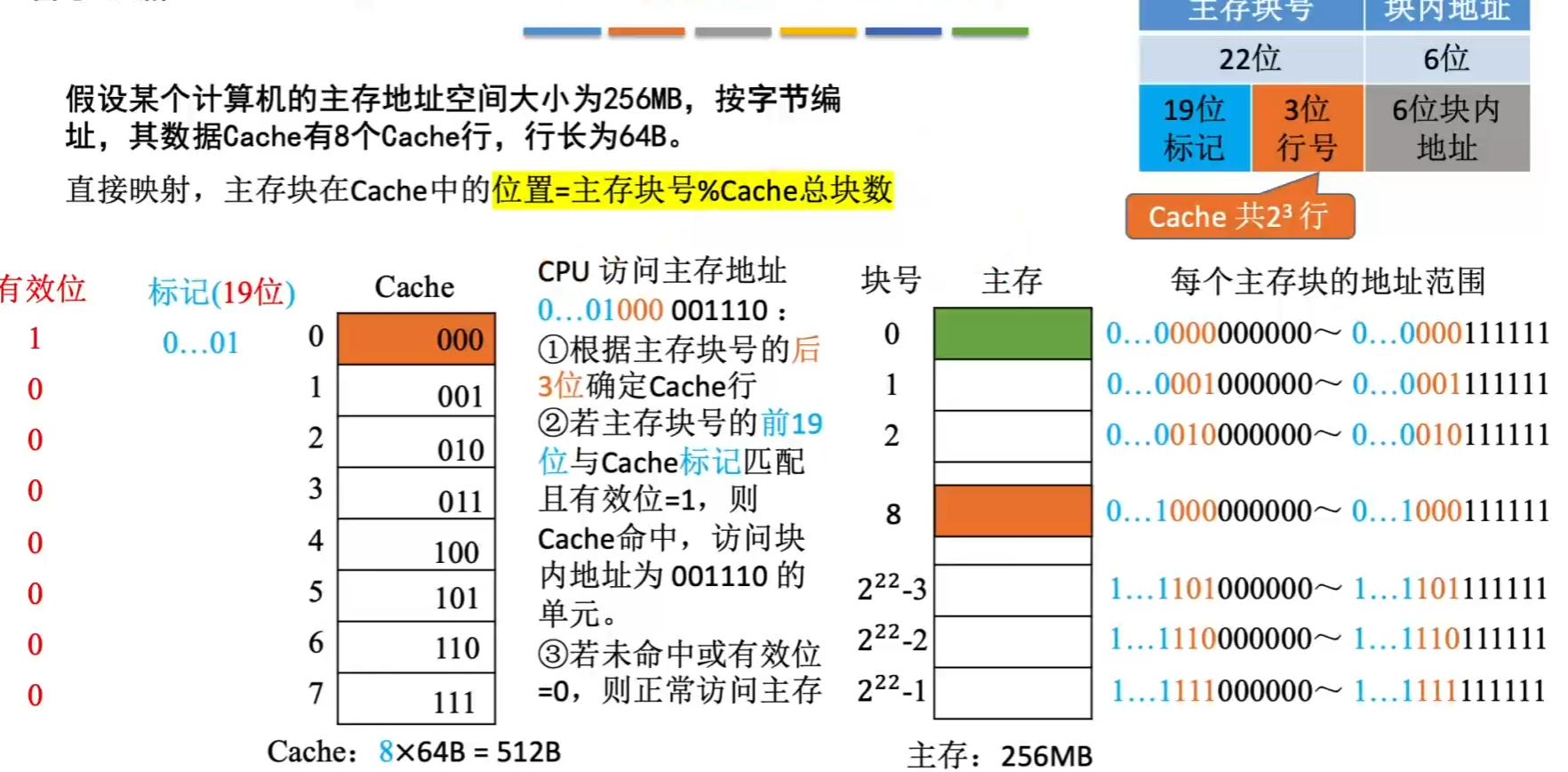

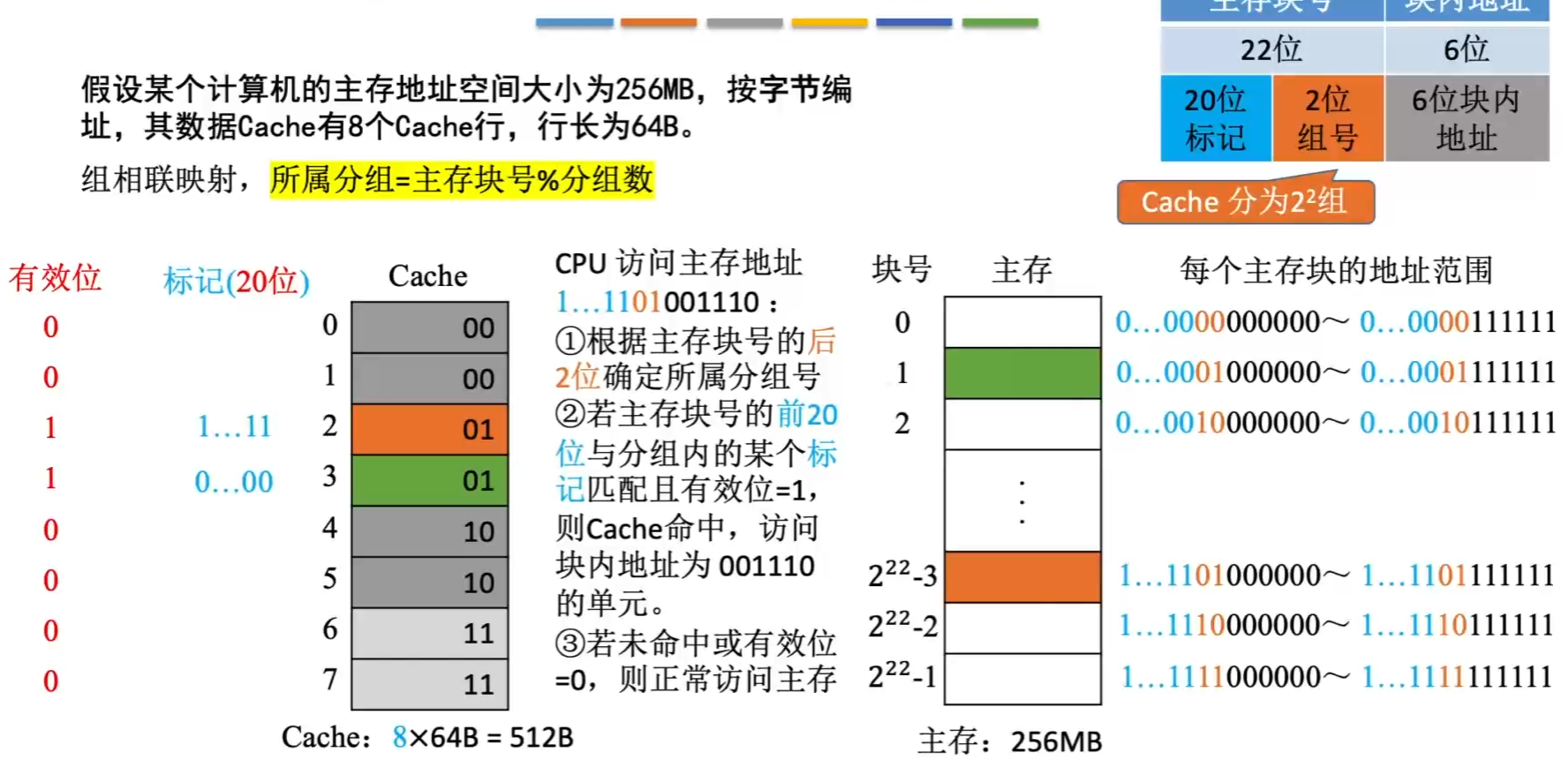

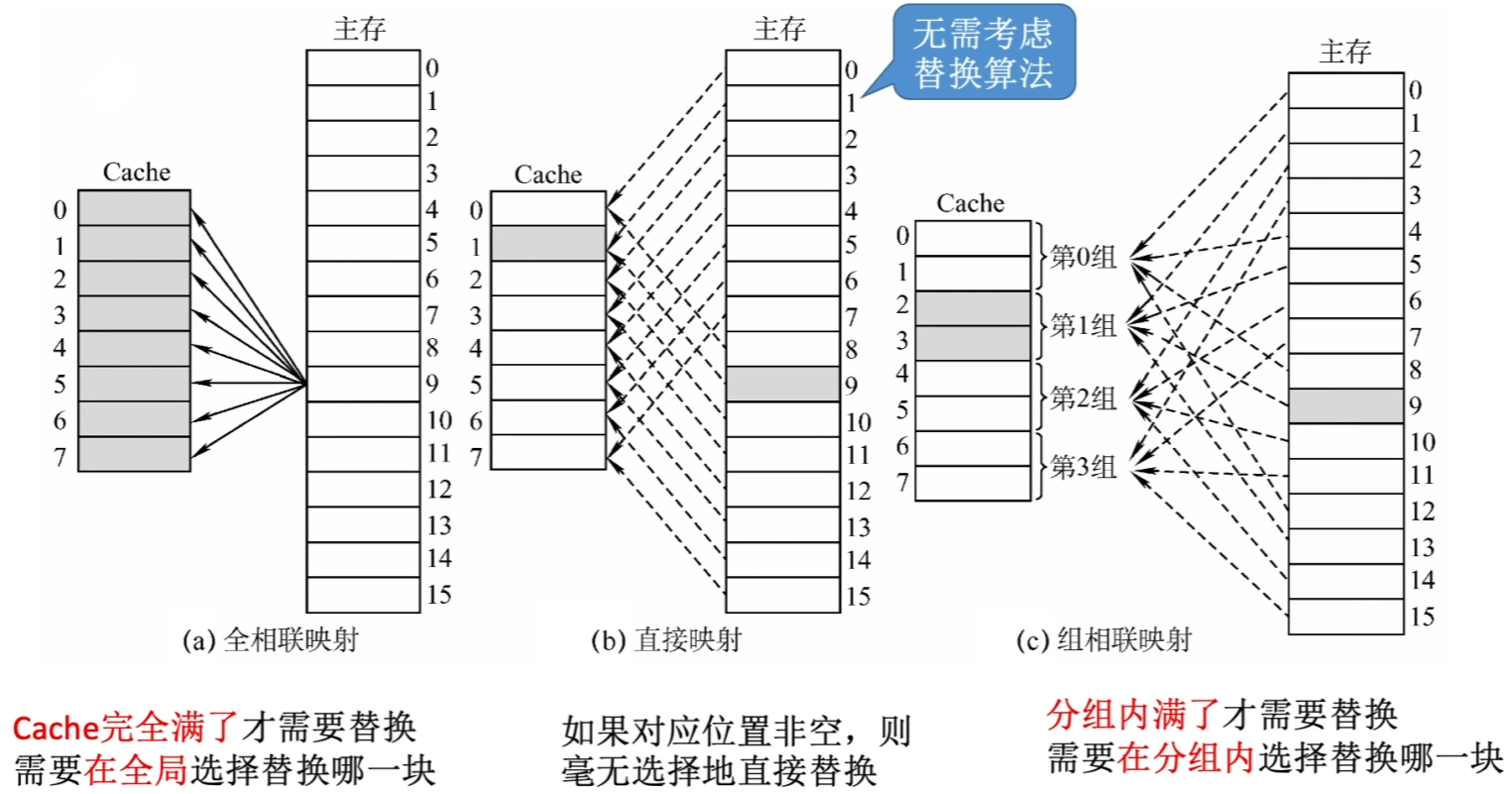

6 Cache与主存的映射关系

全相联映射

直接映射

组相联映射

2路组相联映射——2块分一组,分四组(假设8个Cache行

分为8组降级为直接映射 分为1组降级为全相联映射

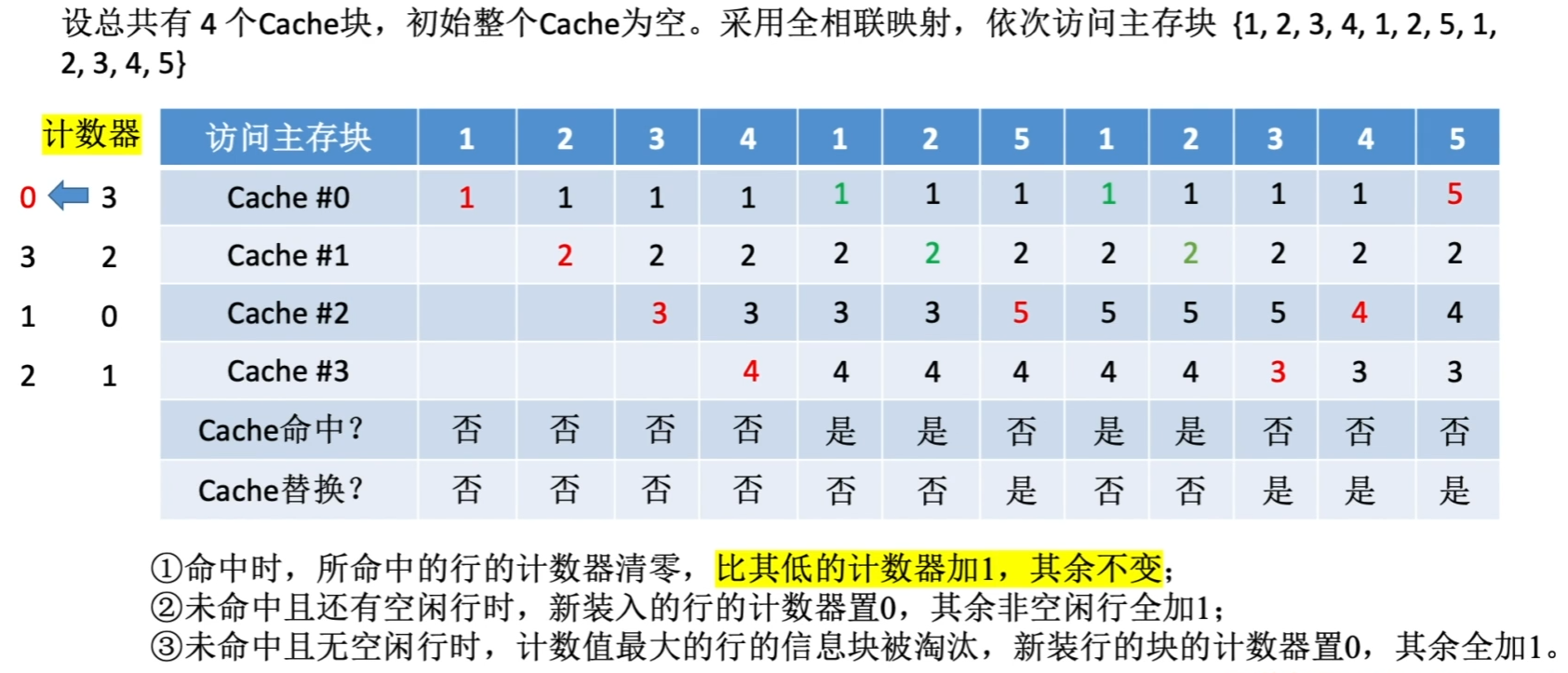

7 Cache替换算法

- 随机算法RAND

- 先进先出算法FIFO

- 近期最少使用LRU

- 最近不经常使用LFU

先进先出算法FIFO

近期最少使用LRU(最优秀的

为每一个Cache块设置一个“计数器”,用于记录每个Cache块已经有多久没被访问了。当Cache满后替换“计数器”最大的 从后往前看

最近不经常使用LFU

为每一个Cache块设置一个“计数器”,用于记录每个Cache块被访问过几次。当Cache满后替换“计数器”最小的

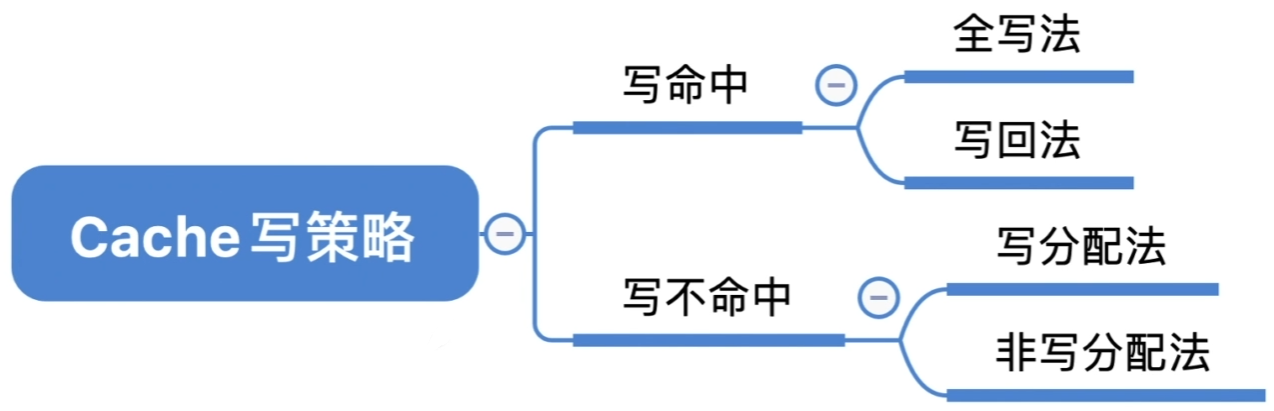

8 Cache写入策略

读操作不会导致Cache和主存的数据不一致

- 全写法(写直通法,写穿策略,write-through)——当CPU对cache写命中时,必须把数据同时写入Cache和主存,一般使用写缓冲(write buffer) 写操作频繁会阻塞

- 写回法(write-back)——当CPU对Cache写命中时,只修改Cache的内容(修改后增加标记 脏位),而不立即写入主存,只有当此块被换出时才写回主存

- 写分配法(write-allocate)——当CPU对Cache写不命中时,把主存中的块调入Cache,在Cache中修改。通常搭配写回法使用。

- 非写分配法(not-write-allocate)———当CPU对Cache写不命中时只写入主存,不调入Cache。搭配全写法使用。

现代计算机常采用多级Cache

离CPU越近的速度越快,容量越小 离CPU越远的速度越慢,容量越大

协助Cache工作所需的部件或功能:

- 相联存储器

- 调度替换算法

- 脏位和有效位比较电路

- 标记比较电路

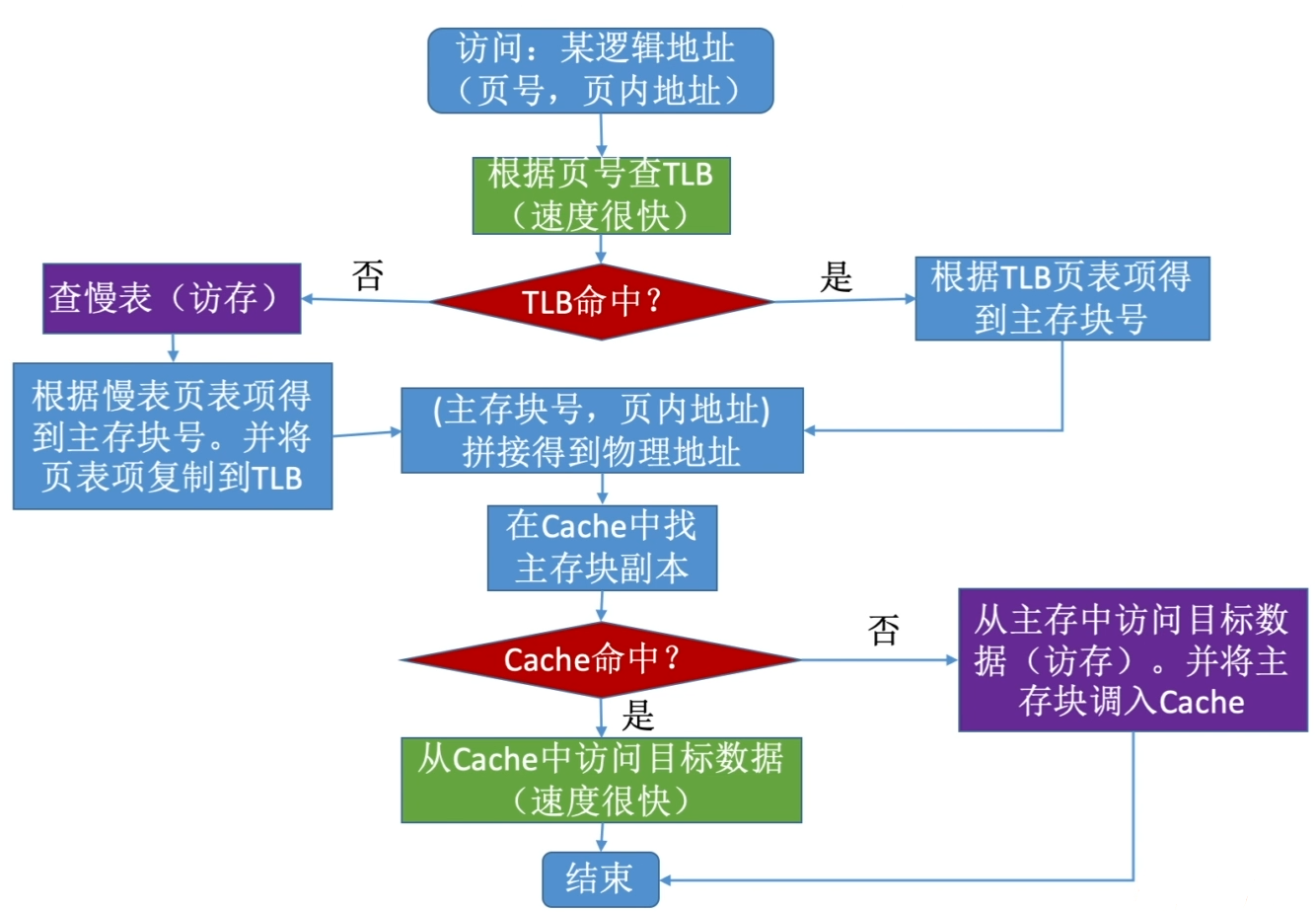

9页式存储器

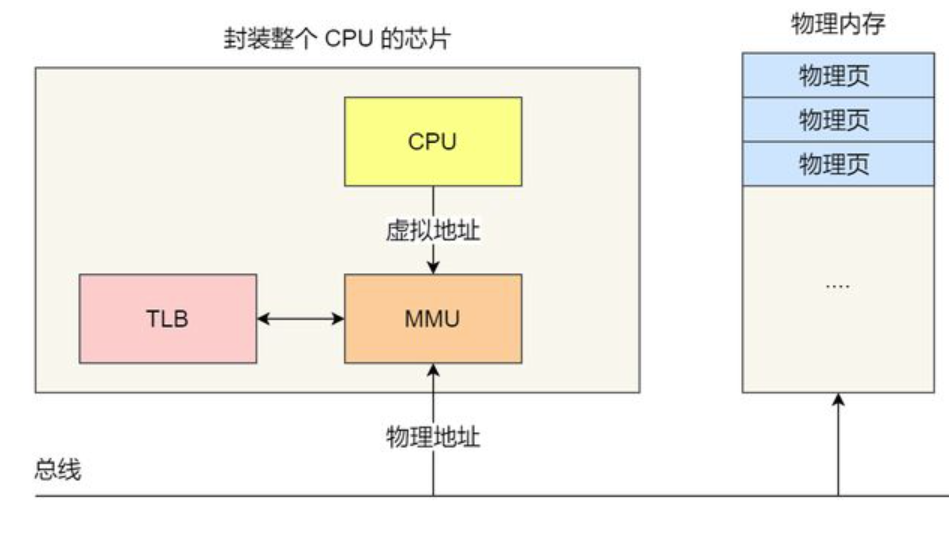

操作系统将进程分页,分为![]() ,映射到主存块号(物理地址)

,映射到主存块号(物理地址)

则建立页表 逻辑页号--(→先Cache 未命中再主存)--主存块号

引入快表TLB

- TLB中存放的是页表项

- TLB的工作原理是局部性原理

- 引入TLB的目的快速实现虚实地址转换

- TLB中采用了类似Cache的映射方法

逻辑地址→快表 未命中再慢表

快表中存储的是页表项的副本; Cache中存储的是主存块的副本

10虚拟存储器

某页式虚拟存储器容量为4G ,主存容量为512M,页大小为8K

- 虚拟地址为32位——4G

- 物理地址29位——512M

- 页表中的页表项数为 2^19项——32-13(4G-8K

- 页内偏移地址为13位——8K

在虚存、内存之间进行地址变换时,功能部件MMU和操作系统配合将地址从虚拟(逻辑)地址空间映射到物理地址空间

TLB - Cache - Page命中关系

- Cache命中,Page必然命中

- TLB命中,Page必然命中

- Page命中,TLB&Cache不一定命中

- Page不命中,Cache不命中

- 没说就是不一定命中

- TLB O⇒Page O

- Cache O⇒Page O

- Page O⇏TLB O&Cache O

- Page X⇒Cache X

第四章-指令系统

1指令格式

x86架构-PC ARM架构-手机

①按地址码数目分类

零地址指令

OP

空操作、停机、关中断等指令

一地址指令

OP-A1

三次访存:取指→读A1(主存地址)→写A1(内容)

两个操作数,其中一个操作数隐含在某寄存器中

二地址指令

![]()

常用于需要两个操作数的算术运算、逻辑运算相关指令

指令含义:(A1)OP(A2)→A1

完成一条指令需要访存4次,取指→读A1→读A2→写A1

R:寄存器 S:内存

- RR——最快

- RS

- SS——最慢

三地址指令

![]()

常用于需要两个操作数的算术运算、逻辑运算相关指令

指令含义:(A1)OP(A2)→A3

完成一条指令需要访存4次,取指→读A1→读A2→写A3

四地址指令

![]()

指令含义:(A1)OP(A2)→A3,A4=下一条将要执行指令的地址

完成一条指令需要访存4次,取指→读A1→读A2→写A3

正常情况下:取指令之后PC+1,指向下一条指令

四地址指令:执行指令后,将PC的值修改位A4所指地址

②按指令长度分类

- 定长指令字结构:指令系统中所有指令的长度都相等

- 变长指令字结构:指令系统中各种指令的长度不等

- 定长操作码:指令系统中所有指令的操作码长度都相同

- 可变长操作码:指令系统中各指令的操作码长度可变

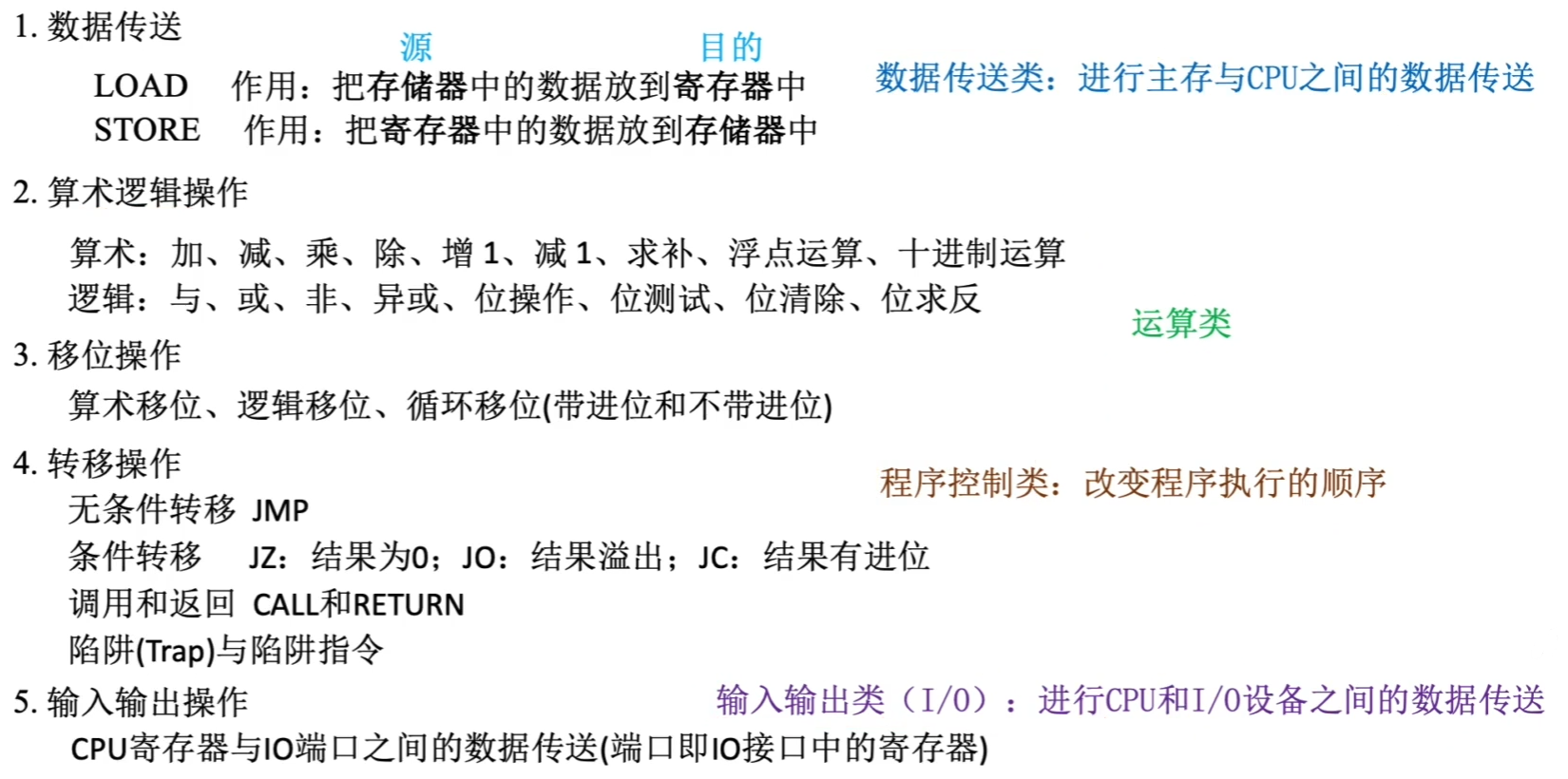

③按操作类型分类

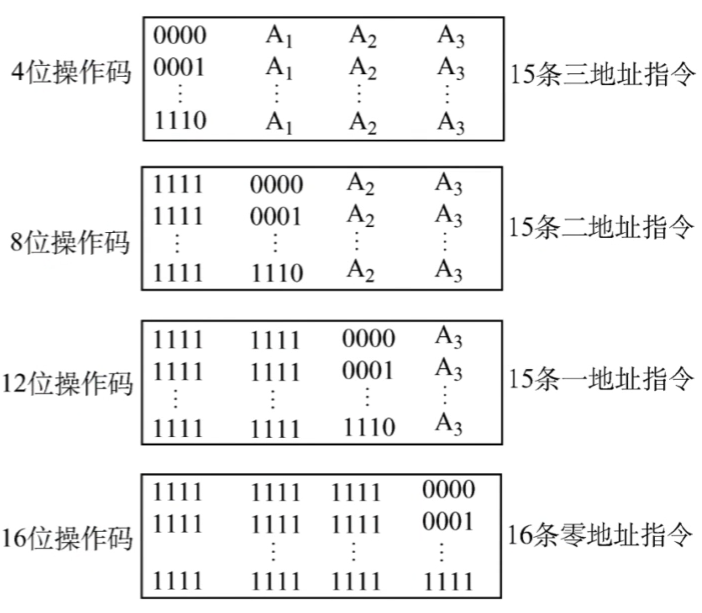

2扩展操作码指令格式

定长指令字结构+可变长操作码

假设指令字长为16位,地址长度为4 ![]()

假设指令字长为16位,地址长度为4

3指令寻址

顺序寻址

由程序计数器PC给出

PC+指令字长→PC

跳跃寻址

直接改变PC的值 JMP、CALL

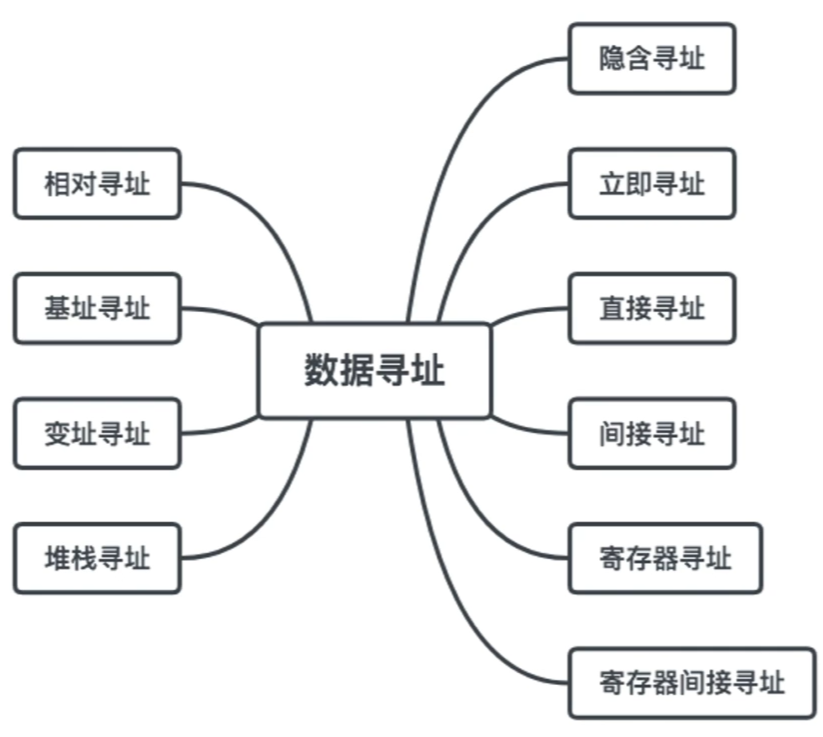

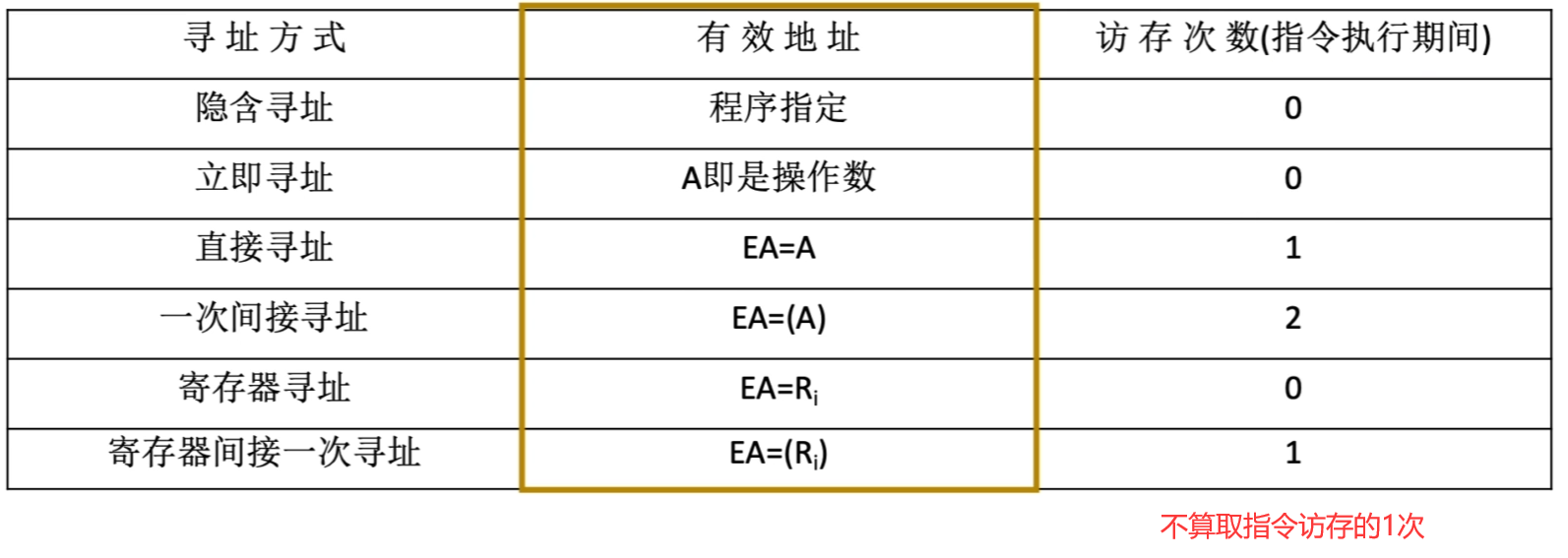

4数据寻址

本条指令的地址码指明的真实地址

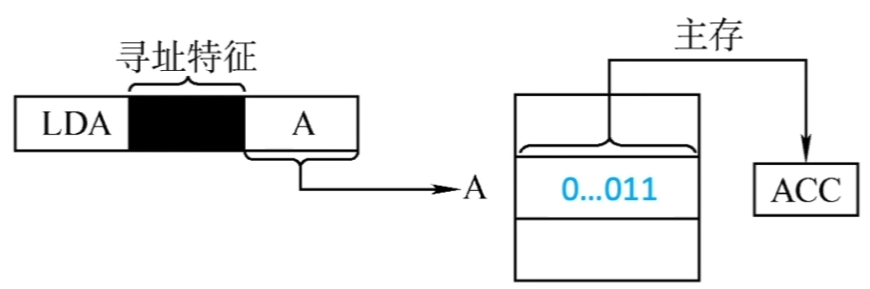

直接寻址

指令字中的形式地址A就是操作数的真实地址EA,即EA=A 。

- 优点:简单,指令执行阶段仅访问一次主存,不需专门计算操作数的地址。

- 缺点:A的位数决定了该指令操作数的寻址范围。操作数的地址不易修改。

两次访存:取指令;执行指令

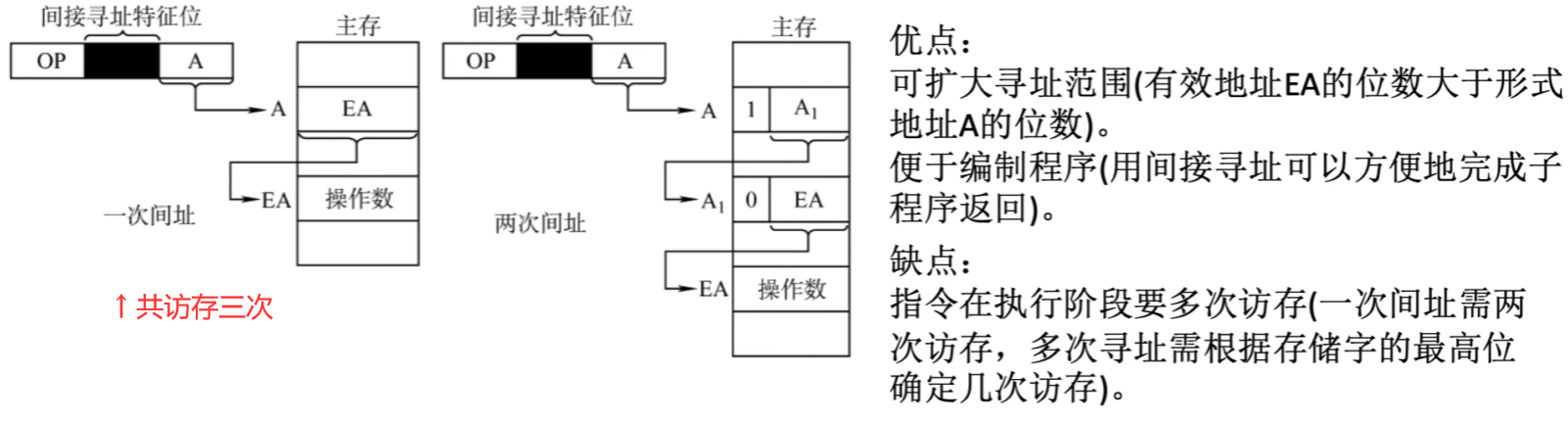

间接寻址

指令的地址字段给出的形式地址不是操作数的真正地址,而是操作数有效地址所在的存储单元的地址,也就是操作数地址的地址,即EA=(A)。

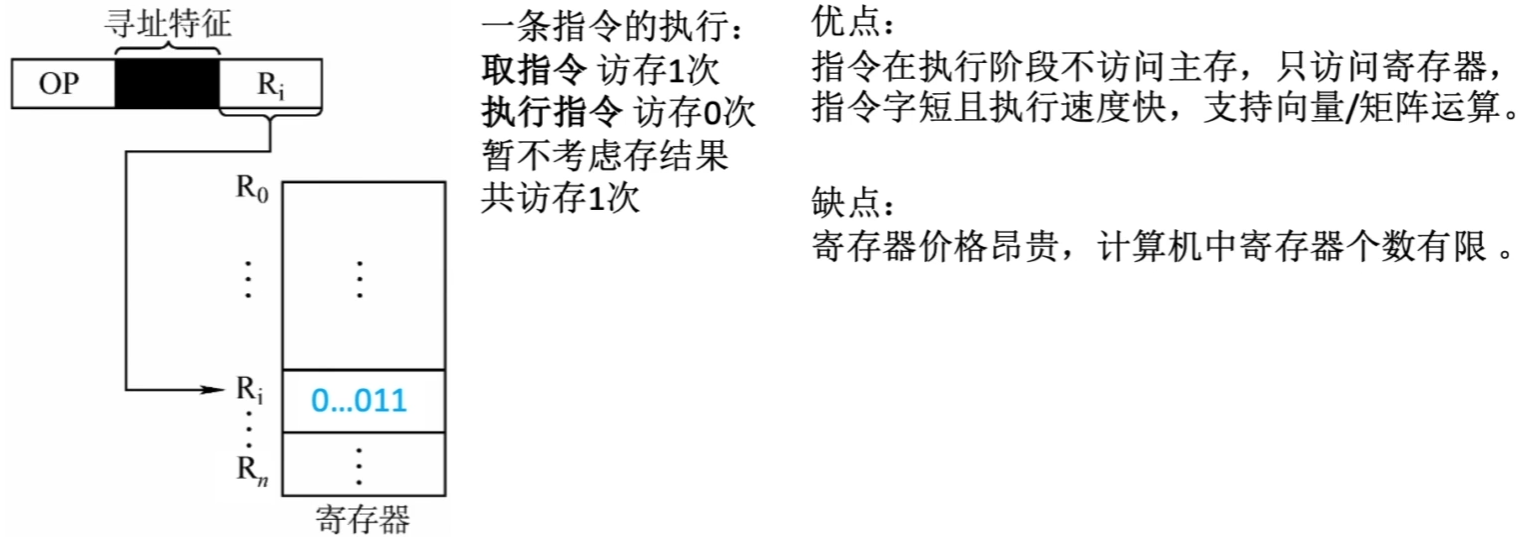

寄存器寻址

在指令字中直接给出操作数所在的寄存器编号,即EA =Ri,其操作数在由R,所指的寄存器内。

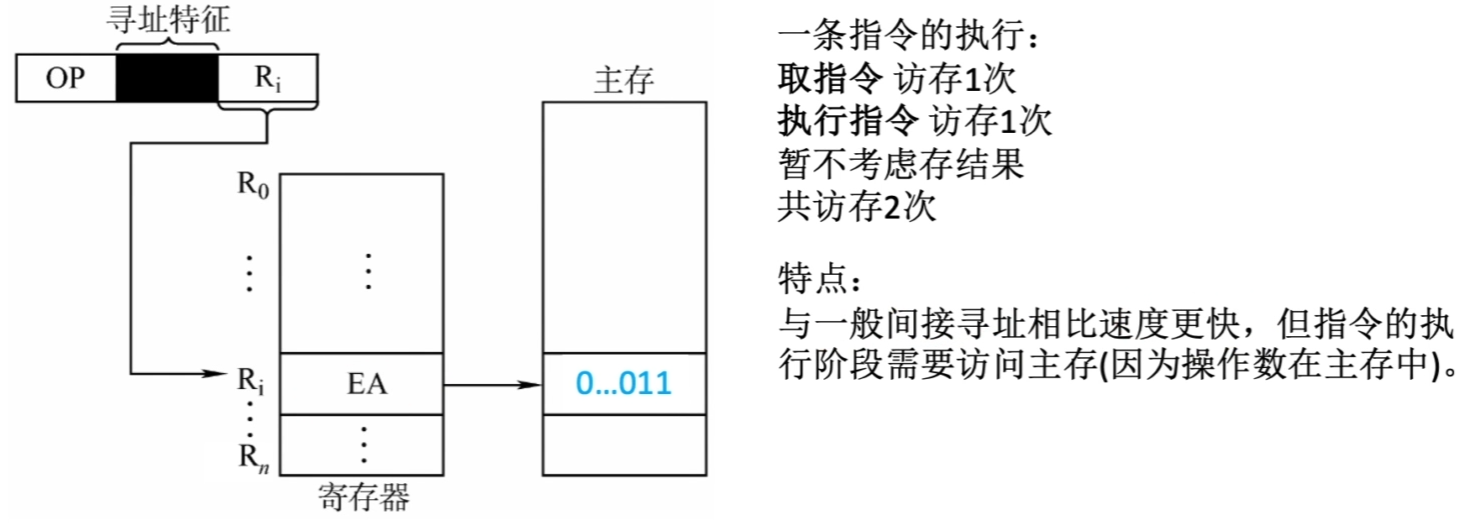

寄存器间接寻址

寄存器Ri中给出的不是一个操作数,而是操作数所在主存单元的地址,即EA=(Ri)。

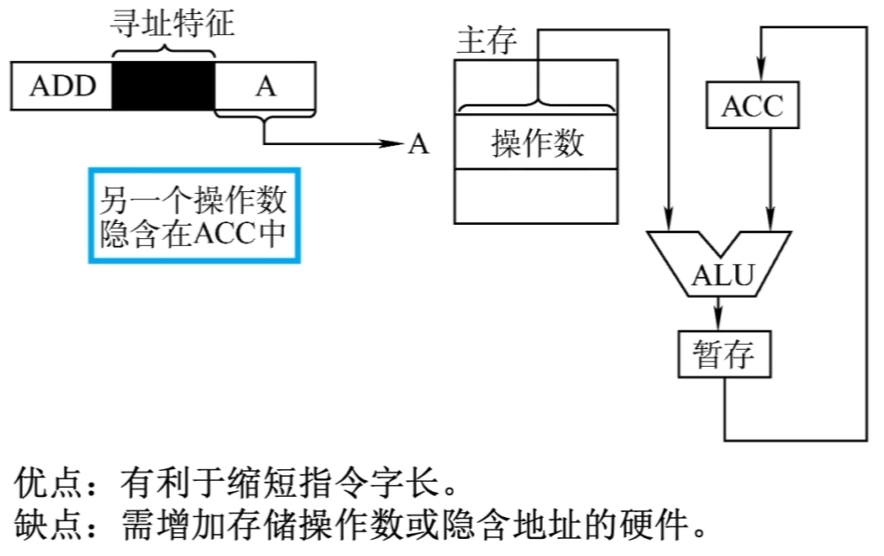

隐含寻址

不是明显地给出操作数的地址,而是在指令中隐含着操作数的地址

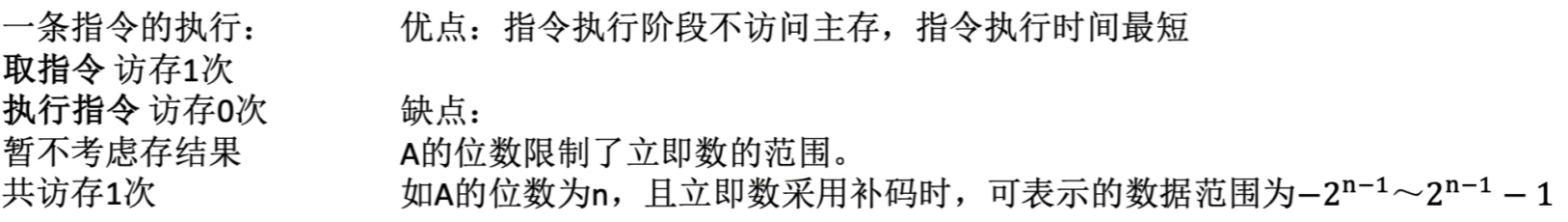

立即寻址

形式地址A就是操作数本身,又称为立即数,一般采用补码形式。#表示立即寻址特征。

![]()

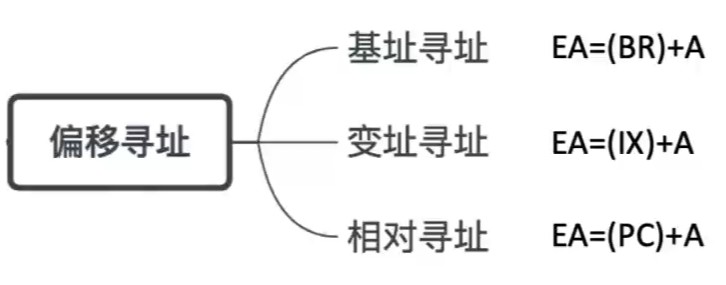

5数据寻址2-偏移寻址

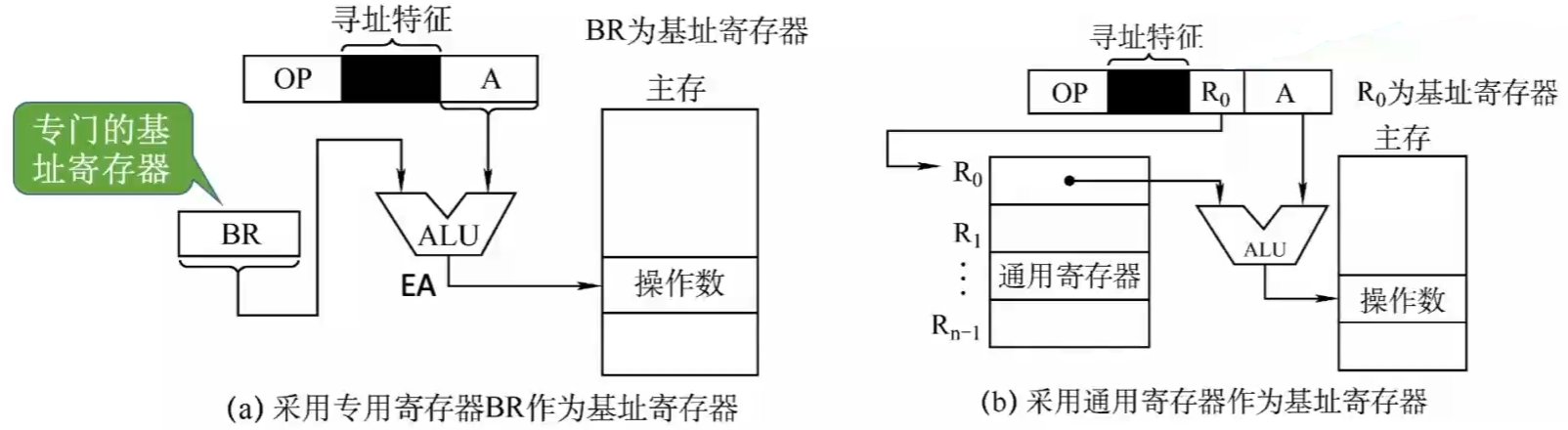

基址寻址

将CPU中基址寄存器(BR)的内容加上指令格式中的形式地址A,而形成操作数的有效地址,即EA=(BR)+A。

BR对程序员透明

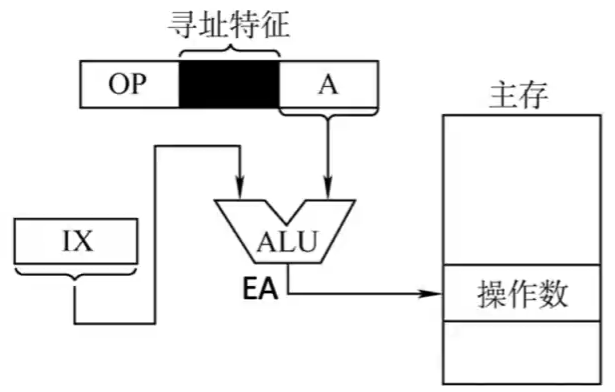

变址寻址

有效地址EA等于指令字中的形式地址A与变址寄存器IX的内容相加之和,即EA= (IX)+A,其中IX可为变址寄存器(专用),也可用通用寄存器作为变址寄存器。

与基址寻址区别:IX对程序员不透明

与基址寻址区别:IX对程序员不透明

便于实现循环程序

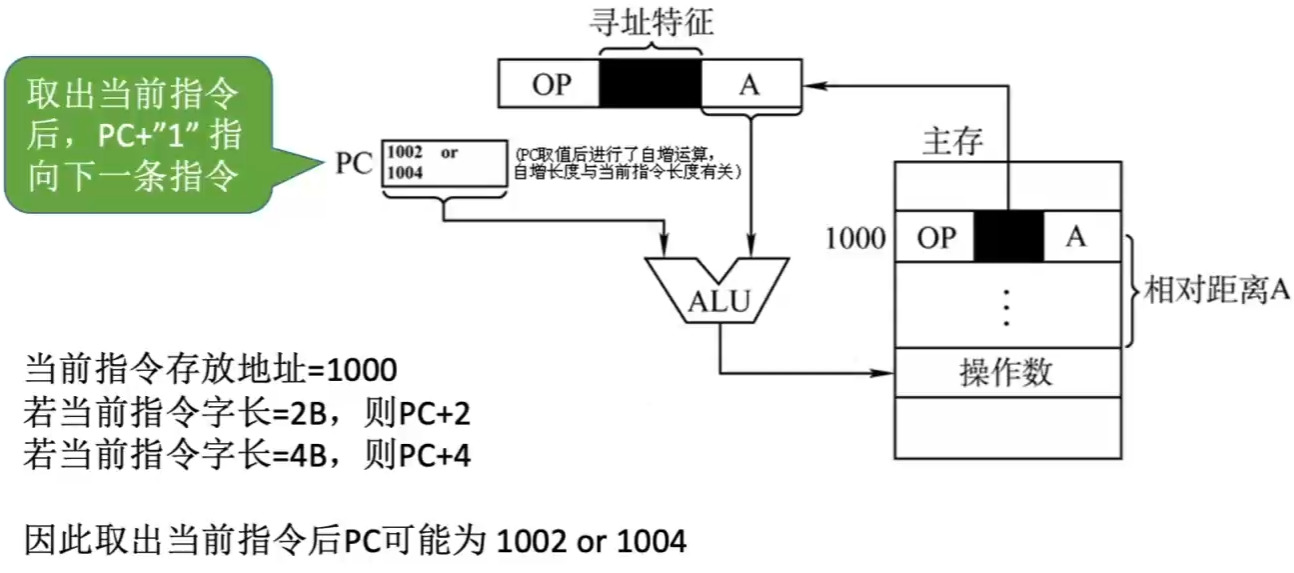

相对寻址

把程序计数器PC的内容加上指令格式中的形式地址A而形成操作数的有效地址,即EA=(PC)+A,其中A是相对于PC所指地址的位移量,可正可负,补码表示。

指令所提供的相对地址是本条指令的下条指令在内存中的首地址为基准位置的偏移量

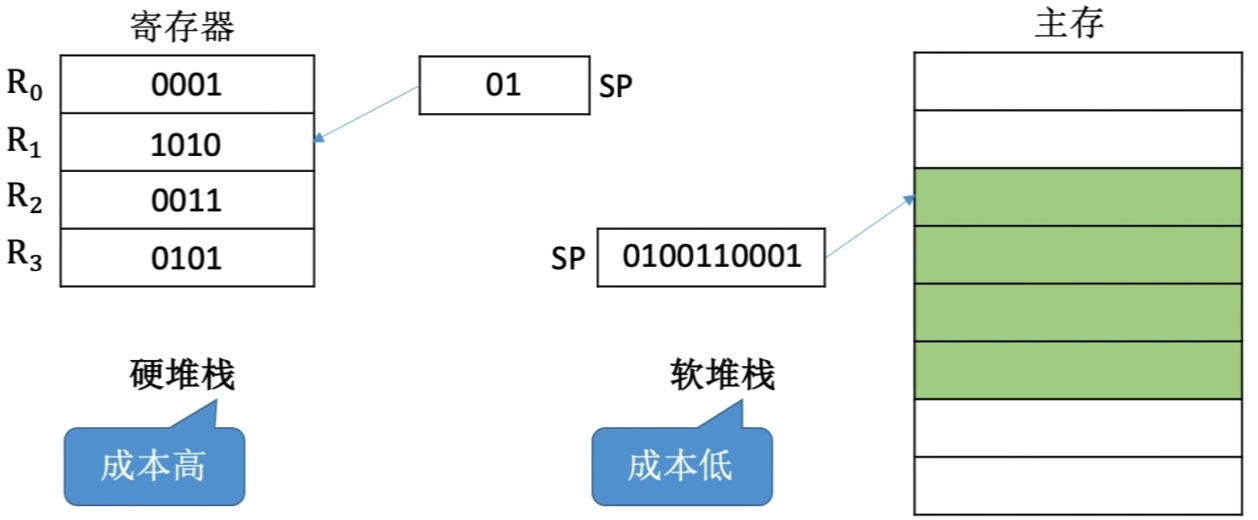

其他:堆栈寻址

操作数存放在堆栈中,隐含使用堆栈指针(SP)作为操作数地址。

MIPS指令

- MIPS是一种精简指令集计算机(RISC),它的指令长度和操作码字段长度都是固定的,这样可以简化指令译码和执行过程。

- MIPS的寻址方式简单,只有三种:相对寻址、伪直接寻址和基址寻址。相对寻址用于分支、跳转等指令,伪直接寻址用于跳转目标地址的计算,基址寻址用于加载和存储等指令。

- MIPS只有Load/Store指令才访问存储器,其他指令都是在寄存器之间进行操作。这样可以减少存储器访问次数和延迟。

- MIPS的寄存器数量较多,有32个通用寄存器和32个浮点寄存器。这样可以提高数据处理能力和并行度。

- MIPS的相对寻址和伪直接寻址都需要将地址左移两位,这是为了实现按32位整数边界对齐存放。这样可以提高数据传输效率和减少错误发生概率。

- MIPS的指令中不单独设置寻址方式字段,而是根据操作码字段来确定。这样可以节省指令空间和增加编码灵活性。

- R型指令是寄存器指令,它只对寄存器中的数据进行运算,不涉及存储器地址的计算。它的操作码OP字段的值均为000000,用funct字段区分具体的指令。它既有算术运算指令,也有逻辑运算指令。

- I型指令是带立即数的指令,它最多使用两个寄存器和一个16位的立即数。它包括访问内存的指令、条件转移指令和立即数运算指令。它支持给寄存器赋立即数的操作。它通过立即数和寄存器来生成存储器地址。

- J型指令是长跳转指令,它只有一个26位的立即数。它支持无条件跳转指令。它只使用伪直接寻址方式,即将立即数左移两位后与PC高四位拼接得到跳转地址。因此,J型指令执行后,PC寄存器的值最后两位一定为00。

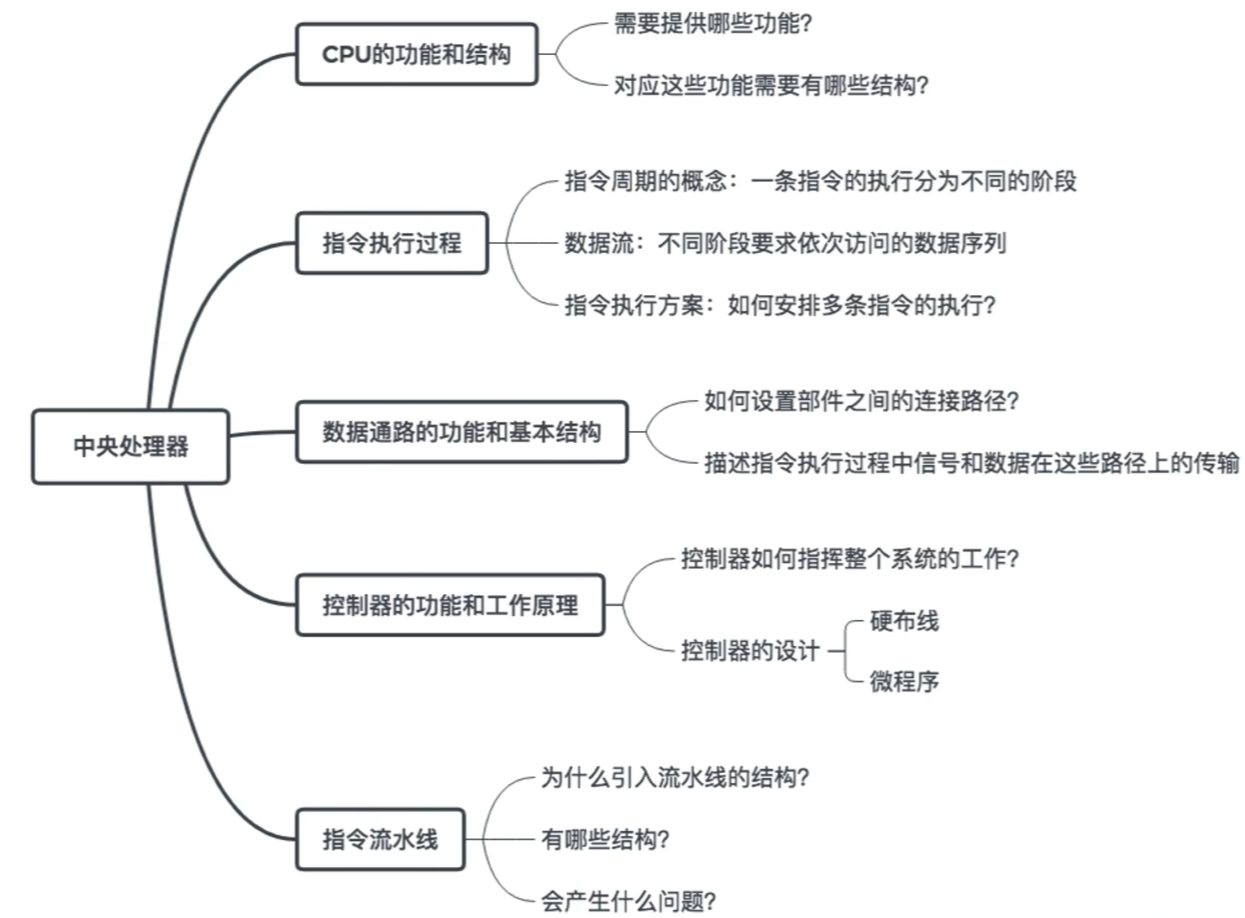

第五章-中央处理器

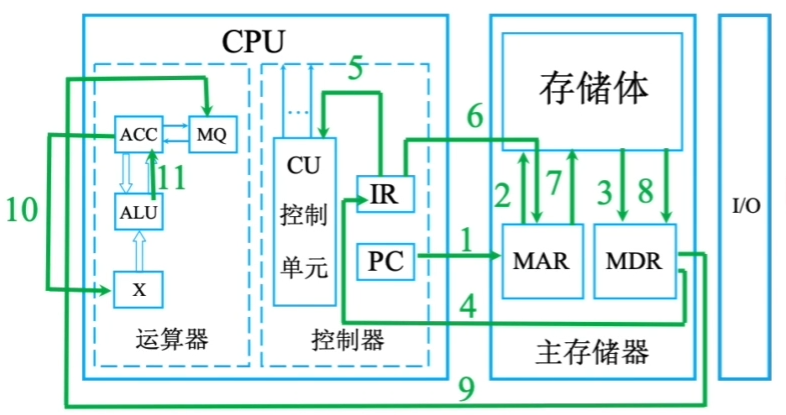

- 用户可见(不透明)的寄存器:通用寄存器组、程序状态字寄存器PSW、程序计数器PC

- 用户不可见(透明)的寄存器:MAR、MDR、IR、暂存寄存器

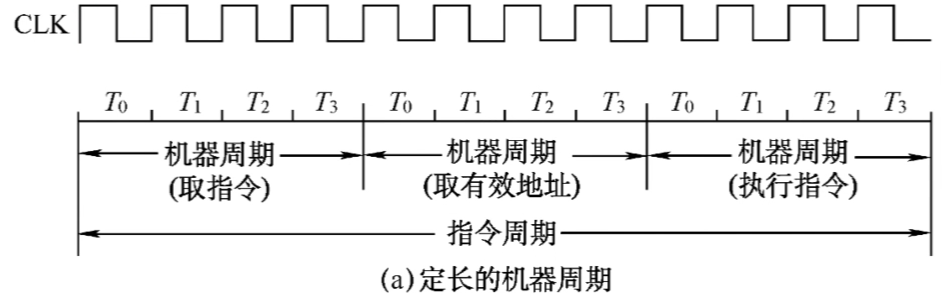

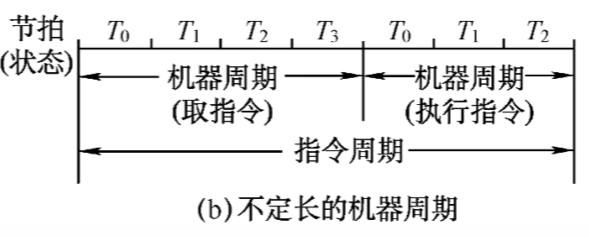

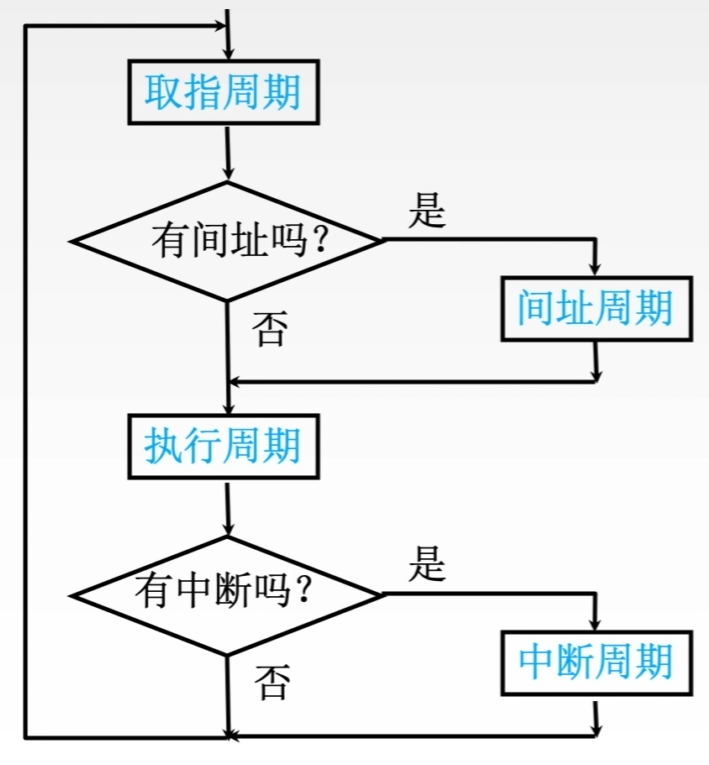

1指令周期

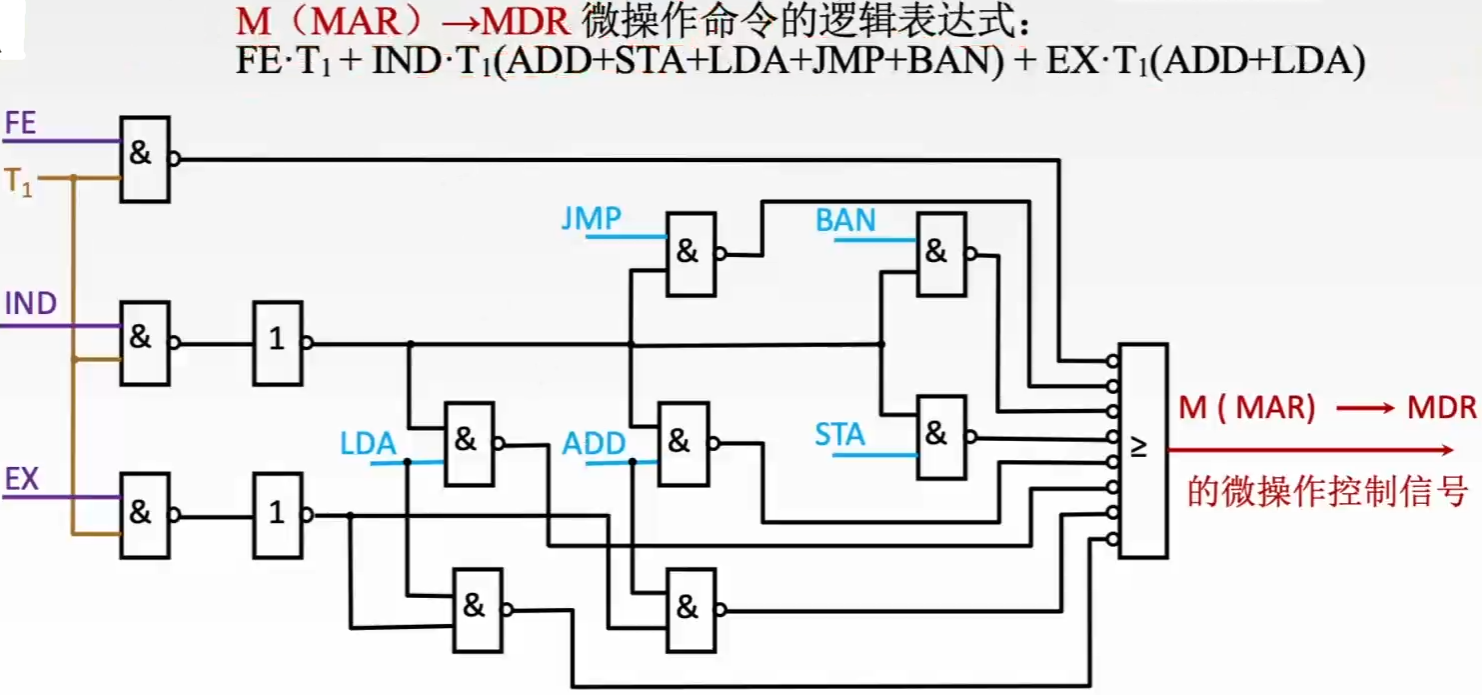

四个周期的标志触发器:FE、IND、EX、INT

四个工作周期都有CPU访存操作,只是访存的目的不同:

- 取指周期是为了取指令

- 间址周期是为了取有效地址

- 执行周期是为了取操作数

- 中断周期是为了保存程序断点

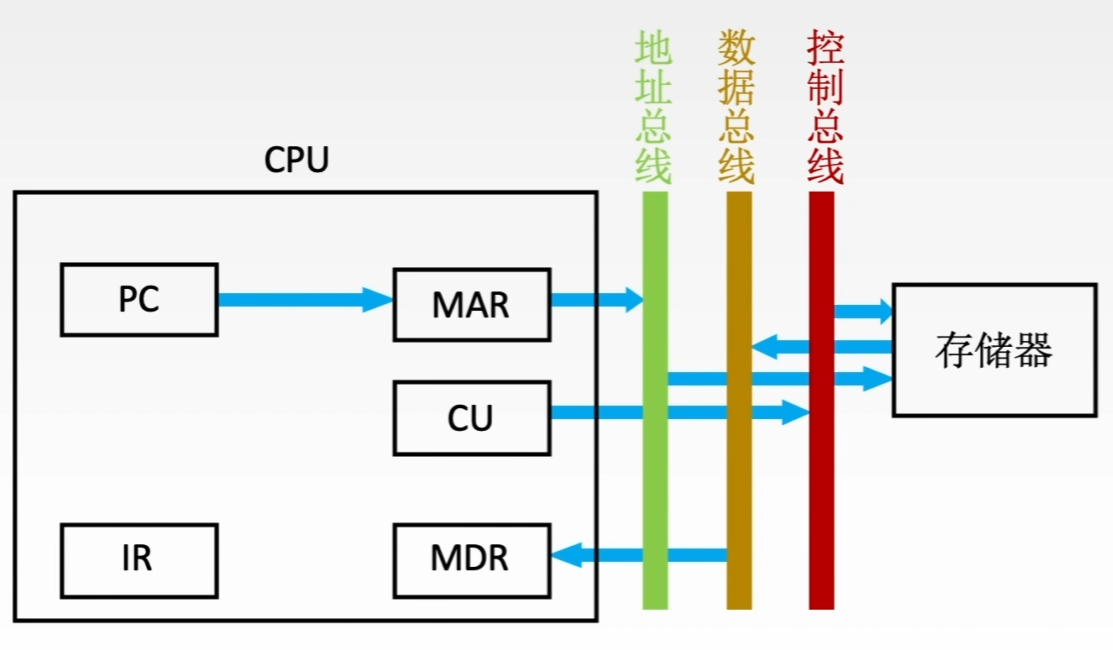

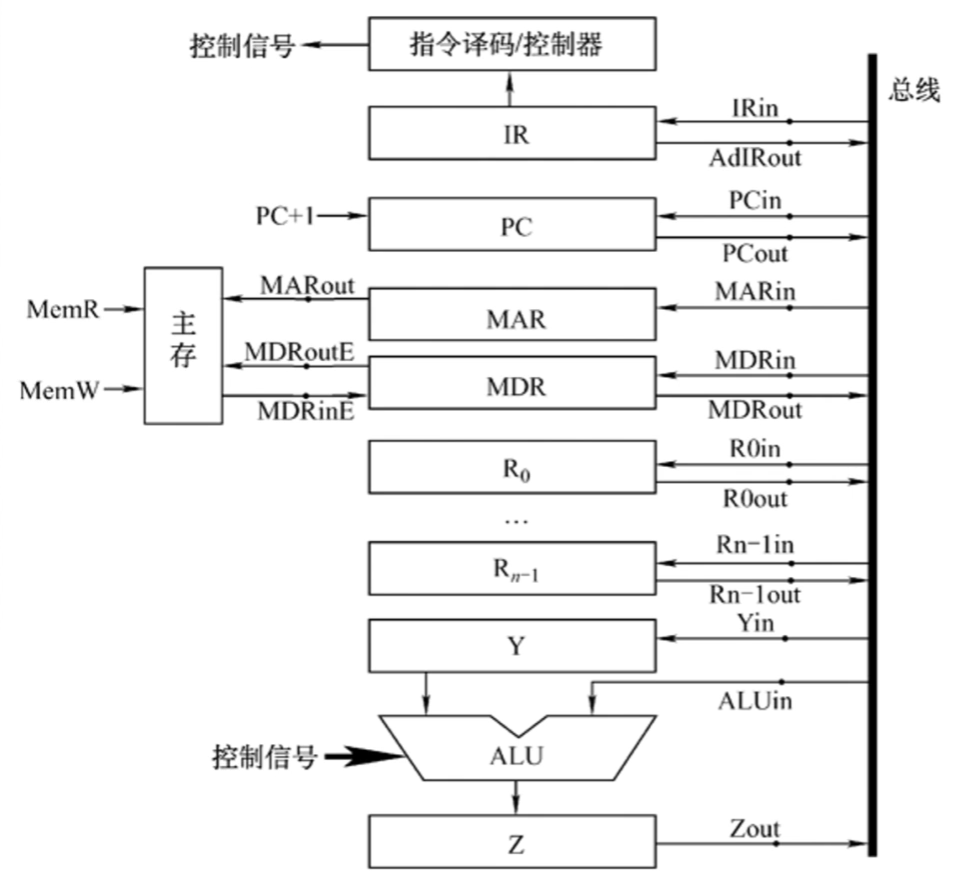

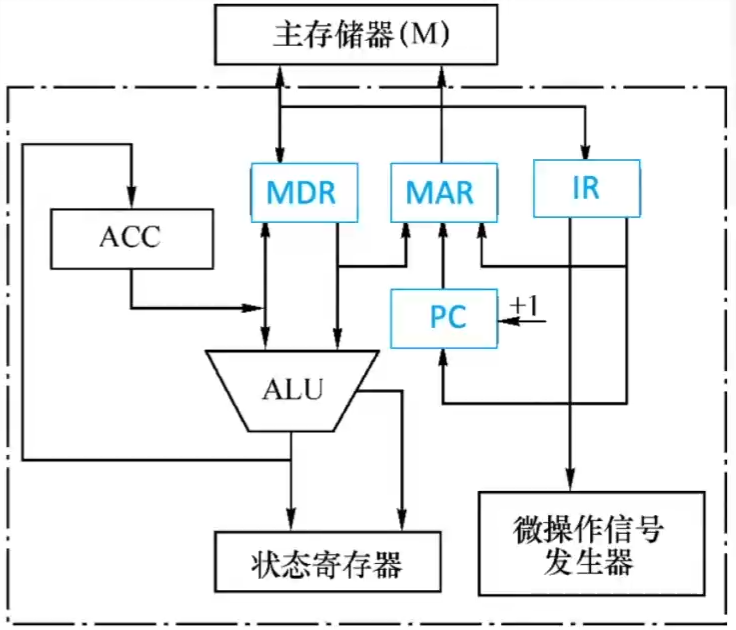

2数据通路

数据在功能部件之间传送的路径

操作控制器——根据指令译码器的输出,产生各种控制信号,用来控制数据通路中的各个部件,如寄存器、运算器、多路选择器等,实现数据在功能部件之间的传送

单总线结构数据通路

同一时刻只能有2条连接BUS的线有效

同一时刻只能有2条连接BUS的线有效

专用通路结构

数据通路的特点:

- 数据通路是指数据在功能部件之间传送的路径,如运算器、寄存器等。

- 数据通路描述了信息从什么地方开始,中间经过哪个寄存器或多路开关,最后传送到哪个寄存器。

- 数据通路由控制部件控制,需要相应的控制信号来打开或关闭开关。

- 不同指令执行使用的数据通路可以不同,同一指令在执行的不同阶段使用的数据路径也不同。

- 常用的数据通路有专用通路和共享通路两种。

- 专用通路是根据指令执行过程中的数据和地址流动方向安排线路,避免使用共享的总线,性能高,但硬件量大。

- 共享通路是将所有寄存器的输入输出端都连接到一条或多条公共总线上,结构简单,但可能存在数据冲突。

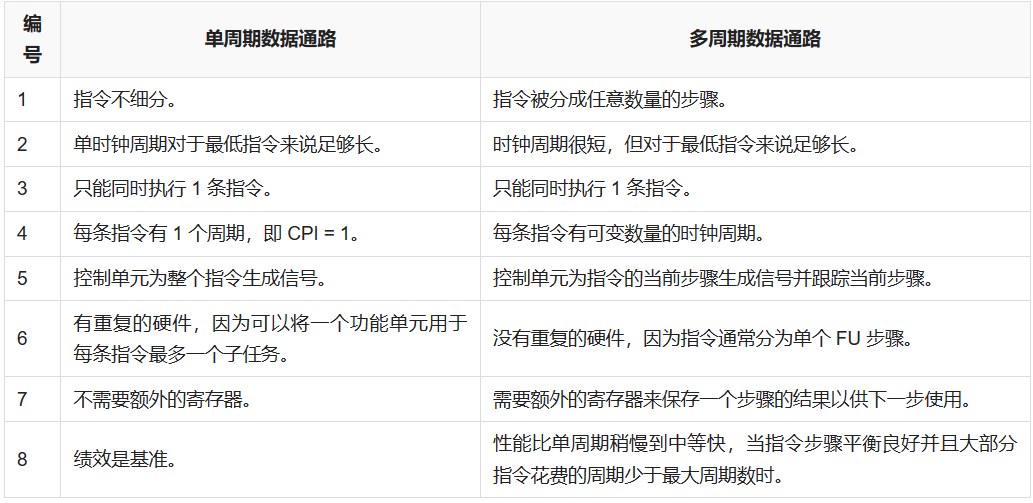

多周期数据通路和单周期数据通路的主要区别是:

- 多周期数据通路只用一个存储器代替指令存储器和数据存储器,而单周期数据通路需要两个存储器。

- 多周期数据通路可以在一个时钟周期内完成多个操作,比如取指令、分析指令、执行指令等,而单周期数据通路只能在一个时钟周期内完成一条指令。

- 多周期数据通路需要更多的寄存器来锁存中间结果,比如IR、DR等,而单周期数据通路不需要这些寄存器。

- 多周期数据通路的性能取决于不同类型指令的执行时间,而单周期数据通路的性能取决于最慢的指令

3硬布线控制器

取指→间址→执行→中断

- 原则一 微操作 的先后顺序不得随意更改

- 原则二 被控对象不同的微操作 尽量安排在一个节拍内完成

- 原则三 占用时间较短的微操作 尽量安排在一个节拍内完成并允许有先后顺序

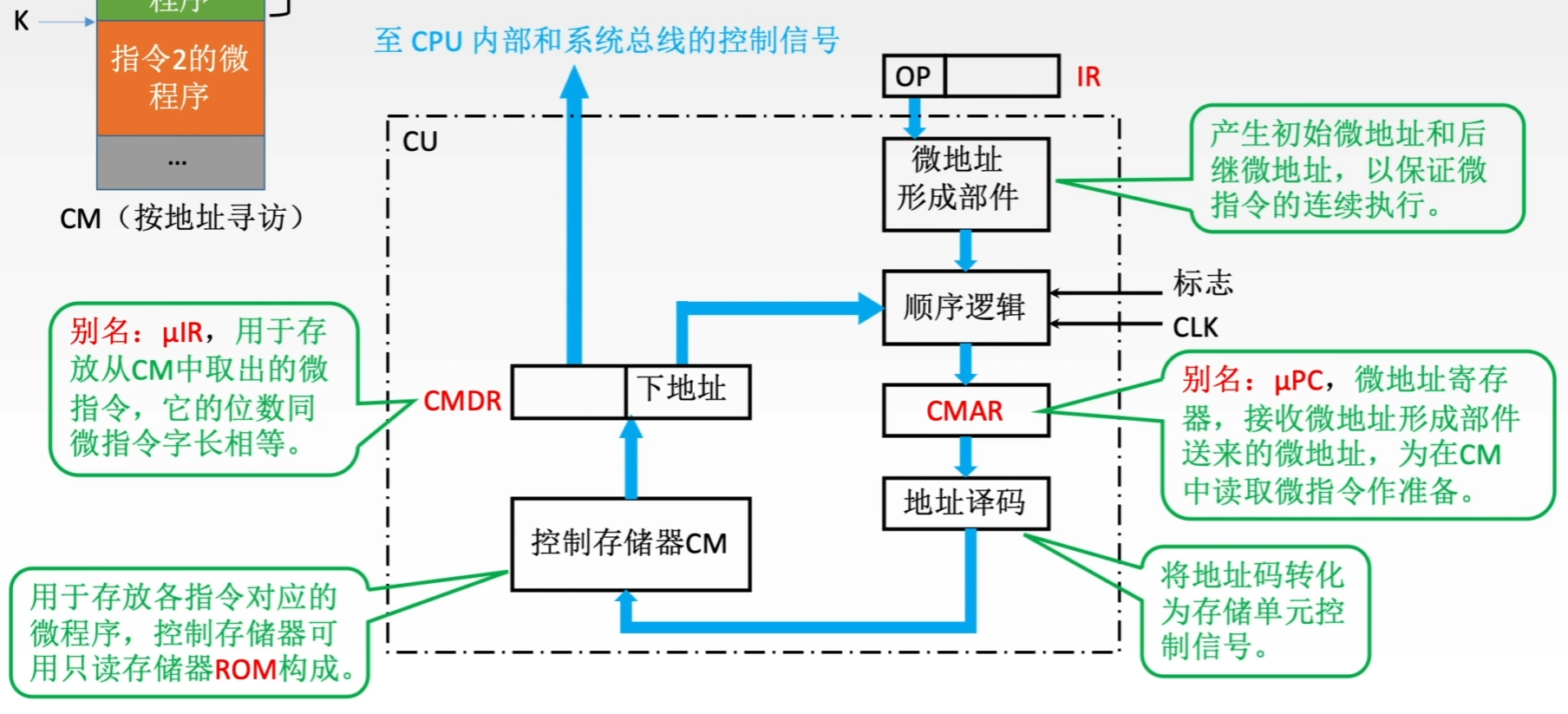

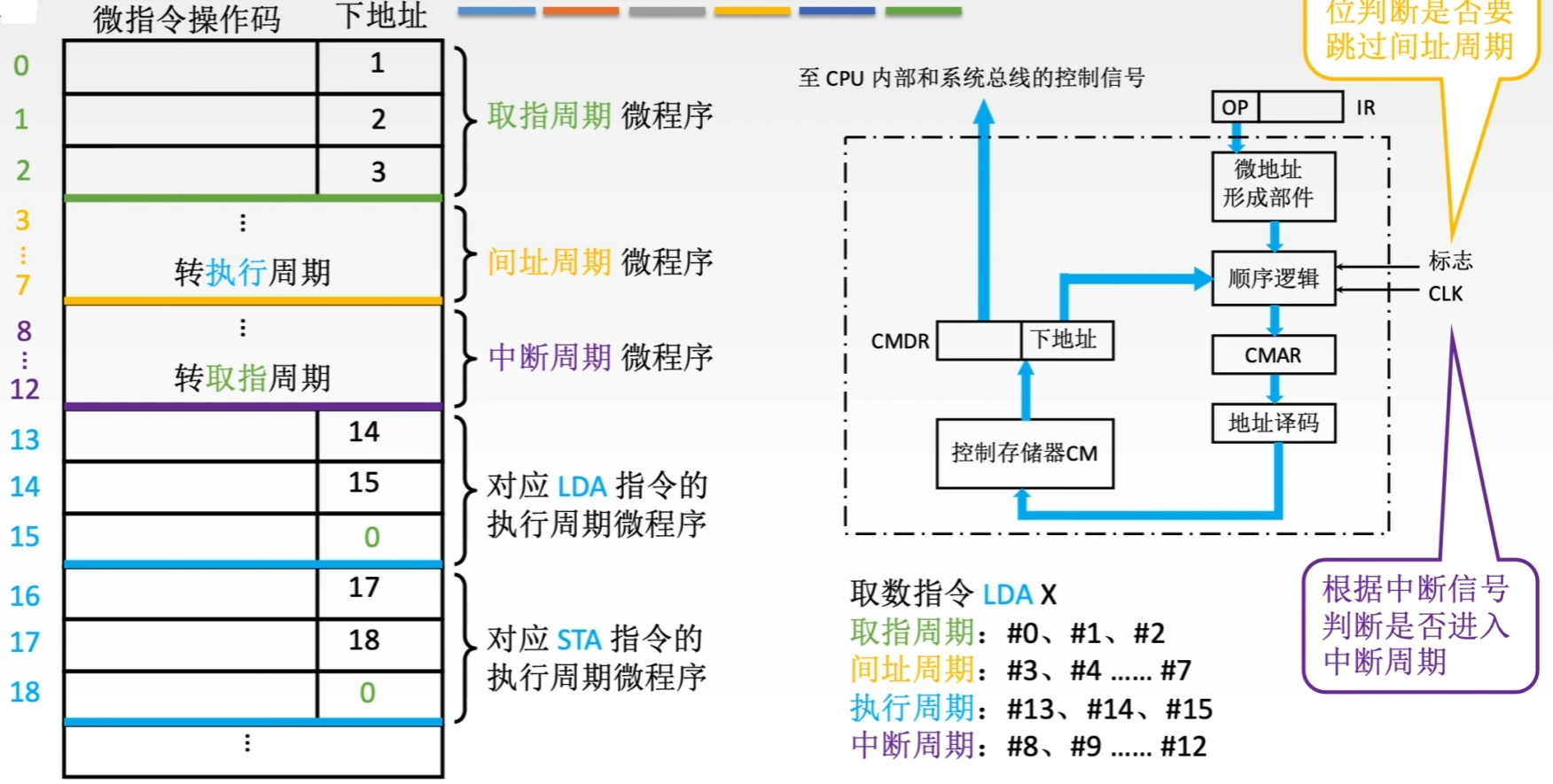

4微程序控制器CU

程序——微程序=指令(每一种指令对应一种微程序——微指令——微操作

控制存储器CM——存放微程序,由ROM构成

微地址形成部件→顺序逻辑→CMAR(μPC)→地址译码→CM→CMDR(μIR)

取指周期通常是公用的

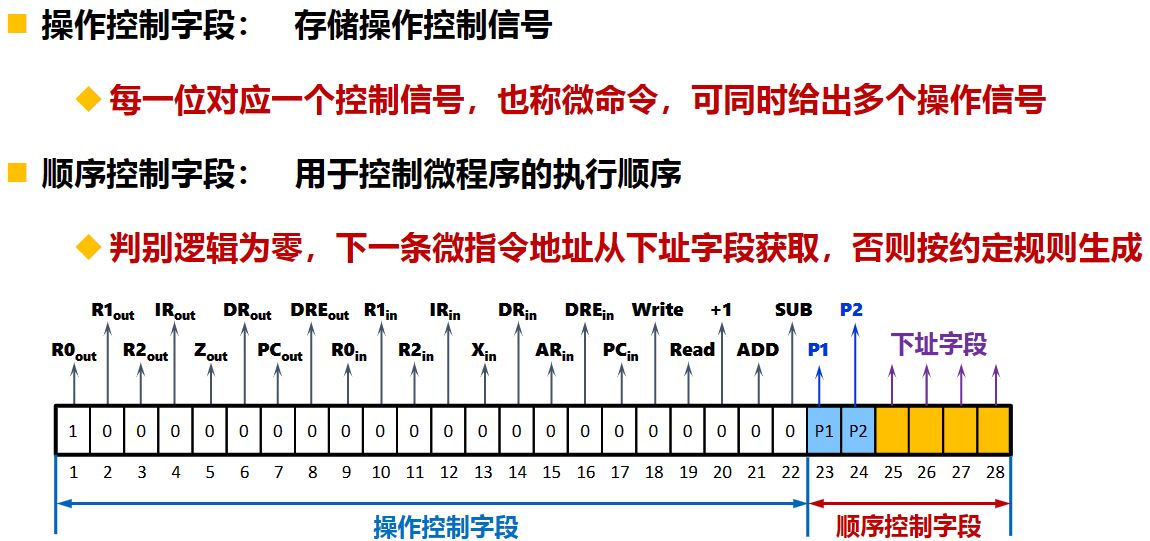

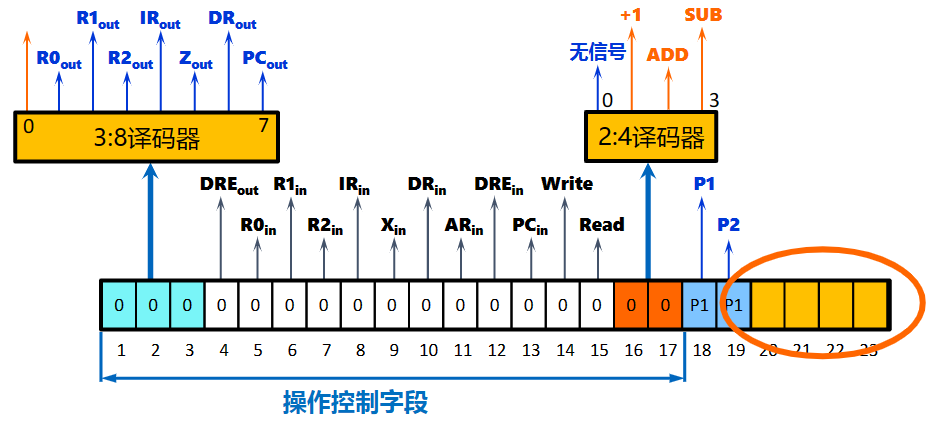

5微指令的设计

- 水平型微指令——一条微指令能定义多个可并行微命令 微程序短执行速度快 微指令长 编写程序较麻烦

- 垂直型微指令——一条微指令只能定义一个微命令,由微操作码字段规定具体功能基本格式 微程序长执行速度慢 微指令短

- 混合型微指令——在垂直型的基础上增加一些不太复杂的并行操作

- 直接编码方式——每一位代表一个微操作命令

- 字段直接编码方式——微指令分为多个段,每段译码后发出控制信号

- ①互斥性微命令分在同一段内,相容性微命令分在不同段内。

- ②每个小段中包含的信息位不能太多,否则将增加译码线路的复杂性和译码时间。

- ③一般每个小段还要留出一个状态,表示本字段不发出任何微命令。因此,当某字段的长度为3位时,最多只能表示7个互斥的微命令,通常用000表示不操作。

第六章-输入输出系统

浙公网安备 33010602011771号

浙公网安备 33010602011771号