摘要:在 SystemVerilog 中,要一次性实例化多个接口(interface),通常有两种简洁的方法:接口数组和 generate 循环。它们都允许你用很少的代码生成大量的接口实例。 方法一:接口数组(最简洁) 如果多个接口实例的结构完全相同,可以直接声明接口数组: // 假设有一个接口定义 in

阅读全文

摘要:在 SystemVerilog 中,直接声明一个 interface 类型的动态数组 是不允许的,因为 interface 本身是静态的(就像 module 一样)。你需要使用 虚拟接口(virtual interface) 的句柄来动态管理接口实例。 正确做法:声明 virtual interfa

阅读全文

摘要:在以前的使用中,scoreboard都是在build_phase中调用get函数,并且调用的前提是参数已经设置过。一个sequence是在task phase中运行的,当其设置一个参数的时候,其时间通常是不固定的。 针对这种不固定的设置参数的方式,UVM中提供了wait_modified任务,它的参

阅读全文

摘要:1.Copy函数用于实例的复制,其原型为: Extern function void copy(uvm_object rhs); 如果要把某个A实例复制到B实例中,应该使用B.copy(A)。在使用此函数前,B实例必须已经使用new函数分配好了内存空间; 2.Compare函数用于比较两个实例是否一

阅读全文

摘要:在做reset测试的时候,先start一个sequence,在其body进行的途中复位,并把它终止。记录一下遇到一系列的问题。 干掉sequence的两种方式 本节简要介绍两种终止sequence的方法,用法都非常的简单,但采用这两种方法来结束sequence的时候,都有潜在的风险,这将在下节介绍。

阅读全文

摘要:uvm_top = uvm_root::type_id::create("__top__", null); uvm_test_top = my_casen::type_id::create("uvm_test_top", this); env = my_env::type_id::create("e

阅读全文

摘要:Package在UVM中的作用是什么? 参照【SystemVerilog的语言参考手册】的定义 【SystemVerilog包提供了额外的机制在多个SystemVerilog模块,接口和程序之间,共享参数,数据,类型,任务,函数,序列,以及特性的声明。 包是显示命名的作用域。它出现在源文本的最外层。

阅读全文

摘要:其他类型 uvm_status_e // Enum: uvm_status_e // // Return status for register operations // // UVM_IS_OK - Operation completed successfully // UVM_NOT_OK -

阅读全文

摘要:核心区别概览 所属与并行关系:run_phase 与 12 个 run-time task phase(如 reset_phase、configure_phase、main_phase、shutdown_phase 等)是并行执行的;其中 run_phase 属于 common_domain,其余

阅读全文

摘要:uvm_top = uvm_root::type_id::create("__top__", null); uvm_test_top = my_casen::type_id::create("uvm_test_top", this); env = my_env::type_id::create("e

阅读全文

摘要:在验证环境中,会经常使用uvm的后门操作系列函数,uvm_hdl_force, uvm_hdl_read, uvm_hdl_deposit等。使用后门操作可以直接通过信号的字符串hierarchy路径,进行对RTL内部信号的读取和赋值。 使用uvm_hdl_read常见的写法可能是这样: ``` b

阅读全文

摘要:环境中后门获取DUT内部信号的3种方法: 信号的Hierarchy读取 interface连接 VPI访问 其中前两种方式,借助systemverilog种阻塞等待操作,可以精确地捕获信号的跳变,比如@和wait: ``` //信号Hierarchy读取 @(tb_top.dut.cnt) @(po

阅读全文

摘要:在UVM寄存器模型的操作中,寄存器用于设置DUT状态和芯片状态信息的上报,有前门和后门读写两种方式。 推而广之,其他的DUT内部信号,由于验证的需要,有时也需要进行后门读写。这些信号除了包含前门可读的寄存器以外,还会包含reg/wire信号、状态机的状态值、memory内容等。总的来看,获取DUT内

阅读全文

摘要:uvm_top = uvm_root::type_id::create("__top__", null); uvm_top= new("__top__", null); uvm_test_top = my_casen::type_id::create("uvm_test_top", this); u

阅读全文

摘要:引子 开始本文讨论之前我们先来以一个具体的例子来引出我们今天将要讨论的问题。 put_response/get_response的常规用法实例 图1是apb_master_driver中的一段代码,106-109行是关于driver中将transaction信息通过response的方式返回给发起这

阅读全文

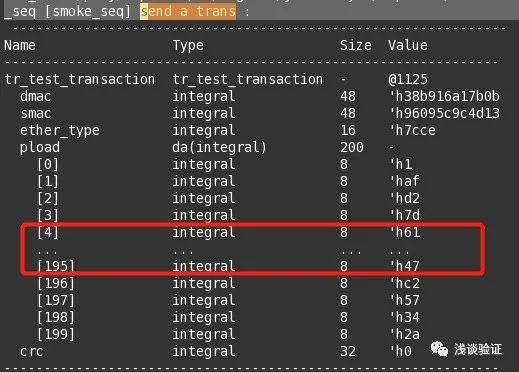

摘要:相信大多数朋友在打印类中数组成员时都遇到过数组打印信息不全的困扰:  假如图中pload[5]到pload[194]中

阅读全文

摘要:uvm_sequence_item.svh ``` // Function: get_sequencer // 返回一个指向默认sequencer的指针 // Returns a reference to the default sequencer used by this sequence. fu

阅读全文

摘要:// Task: get_response // 默认情况下,sequences必须通过调用get_response找回responses。 // 如果没有指定transaction_id, 此任务将返回发送给这个sequence的下一个response。 // 如果在response队列里面没有r

阅读全文

摘要:``` // Function: get_transaction_id // // Returns this transaction's numeric identifier, which is -1 if not set // explicitly by ~set_transaction_id~.

阅读全文

摘要:uvm_component.svh ``` typedef uvm_config_db#(uvm_bitstream_t) uvm_config_int; typedef uvm_config_db#(string) uvm_config_string; typedef uvm_config_db#

阅读全文