摘要:Verilog中复位设计详解:同步/异步复位与释放 1. 基本概念 复位类型 复位 (Reset):将电路初始化为已知状态 释放 (Release):撤销复位信号,使电路正常工作的过程 复位分类 // 四种复位方式: // 1. 同步复位,同步释放 // 2. 同步复位,异步释放 (不推荐) //

阅读全文

摘要:SystemVerilog中,initial begin-end是仿真开始就会执行的代码块。比如UVM的test入口函数run_test,一般就是在initial begin-end中调用。还有一些tb会在initial begin-end中使用fork join_none,用于创建一些仿真中的后台

阅读全文

摘要:``` $strobe $strobe 为选通显示任务。$strobe 使用方法与 $display 一致,但打印信息的时间和 $display 有所差异(也可以直接打印文本)。 当许多语句与 $display 任务在同一时间内执行时,这些语句和 $display 的执行顺序是不确定的,一般按照程序

阅读全文

摘要:``` 1.前言 在verilog仿真中,利用$fopen打开文件后,对文件进行读写操作的系统函数有$fdisplay,$fwrite, $fmonitor, $fstrobe等系统函数,利用这些系统函数,可以将数据写到对应的文件中。下面就针对这些用法做一个梳理。本文主要讲\$fdisplay和\$

阅读全文

摘要:1. +: 和 -: 动态位截取 位截取经常用到, 我们一般是使用诸如vt[7:2]这样的形式, 位边界都是常量. 如果想要位边界是变量 以实现动态截取呢, 如果我们这样写 vt[cnt+4:cnt](cnt是变量), 是编译通不过的. 正确的语法应该这样写: `vt[base+:width] or

阅读全文

摘要:下面两幅截图来自《Verilog_IEEE1364_2001》:   y = ~a; ###2.1.3 assign #(2,3,4) y = ~a; ###2.1.4 assign #

阅读全文

摘要:电路的延时 在实际电路中存在两种延迟,惯性延迟 (Inertial delay) 和传导延迟 (Transport delay)。 惯性延迟 定义:若元件的输入信号的脉冲宽度小于一定值时,元件的输出没有响应,也就是说元件具有一定的惯性。 产生原因:当脉冲到达时,由于脉冲宽度小于元件本身的延迟,当脉冲

阅读全文

摘要:module...endmodule可以有assign连续赋值语句,always语句和initial语句。 always中可以有if语句。 initial中可以有if语句。

阅读全文

摘要:下面首先定义输入输出:a和b都是有符号位的5bit端口,c和d是无符号位的5bit端口。 input signed [4:0] a; input signed [4:0] b; output [4:0] c; output [4:0] d; //右移一位 assign b = a >>> 1; as

阅读全文

摘要:偶校验: 数据和校验位中1的总数为偶数,则认为数据无误,否则标识数据有误; 奇校验: 数据和校验位中1的总数为奇数,则认为数据无误,否则标识数据有误; 奇偶校验位的计算方法: module parity_check( input clk, input rst_n, input [7:0] data_

阅读全文

摘要:($display)自动地在输出后进行换行。 ($write)则在输出后不换行。如果想在一行里输出多个信息,可以使用($write)。 在($display)和($write)中,其输出格式控制是用双引号括起来的字符串,包括以下信息: 格式说明,有(%)和格式字符组成。它的作用是将输出的数据转换成指

阅读全文

摘要:https://www.veripool.org/wiki/verilog-mode/Verilog-mode_veritedium Verilog-Mode: Reducing the Veri-Tedium Wilson Snyder wsnyder AT wsnyder.org SNUG Sa

阅读全文

摘要:verilog-mode是什么 官网的介绍(https://www.veripool.org/wiki/verilog-mode): Verilog-mode.el is the extremely popular free Verilog mode for Emacs which provides

阅读全文

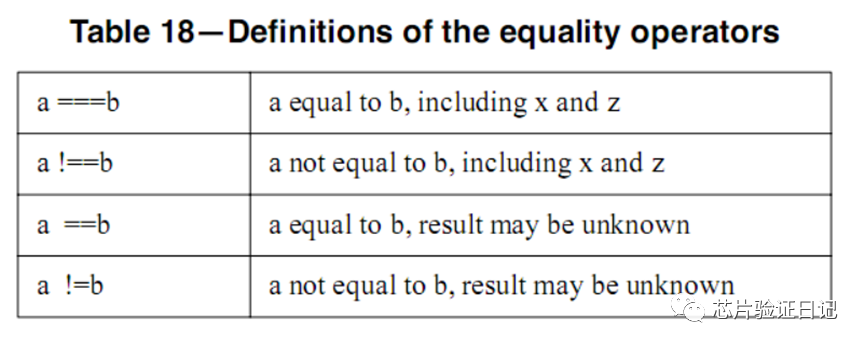

摘要:在Verilog HDL语言中,存在着4中等式运算符: == 等于 != 不等于 等于 != 不等于 注意:求反号,双等号,三等号之间不能有空格。 这四个运算符都是双目运算符,它要求有两个操作数。 ==和!=又称为逻辑等式运算符,其结果有两个操作数的值决定。由于操作数中某些为可能是不定值x和高阻值z

阅读全文

摘要:生成语句可以动态地生成Verilog代码。这一声明语句方便了参数化模块的生成。当对矢量中的多个位进行重复操作时,或者当进行多个模块的实例引用的重复操作时,或者在根据参数的定义来确定程序中是否应该包括某段Verilog代码的时候,使用生成语句能够大大简化程序的编写过程。 生成语句能够控制变量的声明、任

阅读全文

摘要:任务和函数可概括为以下特点: 1.任务和函数都是用来对设计中多处使用的公共代码进行定义;使用任务和函数可以将模块分割成许多个可独立管理的子单元,增强了模块的可读性和可维护性;它们和C语言中的子程序其相同的作用。 2.任务可以具有多个输入、输入/输出(inout)、输出变量;在任务中可以使用延迟事件和

阅读全文

摘要:在一个模块中改变另一个模块的参数时,需要使用defparm命令。例如,在做布线后仿真时,就是利用这种方法把布线延迟通过布线工具生成的延迟参数文件反标注到门级Verilog网表上。 例如: `include "Top.v" `include "Black.v" `include "Annotate.v

阅读全文

摘要:Verilog已有一些建立好的逻辑门和开关的模型。在所设计的模块中,可通过实例引用这些门与开关模型,从而对模块进行结构化的描述。 逻辑门: and (Output, Input, ...) //与门 nand (Output, Input, ...) //与非门 or (Output, Input,

阅读全文

摘要:Net是结构描述中为线路连接(连线和接线)建立的模型。net的值是由net的驱动所决定的。驱动器可以是门、UDP、实例模块或者连续赋值语句的输出。 语法: 1.supply0和supply1类型的net变量分别具有逻辑值0和1,并可以为它定义驱动能力(supply strength); 2.tri0

阅读全文