摘要:``` 本文主要给大家介绍SV宏,谈到SV宏大家应该不会感到陌生,因为大家在做前端设计或验证的时候会用到`define定义宏,进行条件编译,或者使用宏来定义参数等,做前端验证的工程师会使用`define来定义一些信号路径等。这些SV宏的用法都是比较常规的用法,很少有验证工程师使用SV宏来处理一些其他

阅读全文

摘要:VCS是一款常见的Verilog编译工具,它提供很多编译选项来控制编译过程及其输出。本文主要介绍以下两个编译选项: `-y ` 用于指定搜索路径。例如,如果你将一个设计分为若干个不同的模块或模块库,并希望在编译期间找到这些文件,就可以使用-y选项告诉编译器应该去哪里寻找它们。例如,如果你的模块库位于

阅读全文

摘要:1. +: 和 -: 动态位截取 位截取经常用到, 我们一般是使用诸如vt[7:2]这样的形式, 位边界都是常量. 如果想要位边界是变量 以实现动态截取呢, 如果我们这样写 vt[cnt+4:cnt](cnt是变量), 是编译通不过的. 正确的语法应该这样写: `vt[base+:width] or

阅读全文

摘要:文档: `User Guide: Verdi_HWSW_Debug.pdf in $VERDI_HOME/doc` 介绍: Verdi HW/SW co-debug: 对于包含CPU,需要跑嵌入式软件(C/汇编)的验证平台,可以使用verdi追踪RTL和波形对硬件debug,同时打开eclipse的

阅读全文

摘要:下面两幅截图来自《Verilog_IEEE1364_2001》:  ,define)

阅读全文

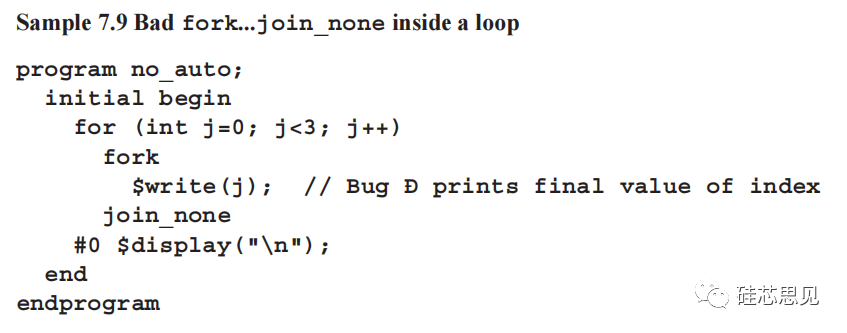

摘要: 示例中,在for循环中使用了fork...join_none结构调用$write显示每次循环执行过程中循环变量的

阅读全文

摘要:我们在工作中常常会针对数组施加各式的约束,下面列举一下有趣的Systemverilog数组约束示例: 1、如何约束动态数组的最后一个元素为特定值。(事先不知道数组的大小) ``` rand int some_dynamic_array[]; constraint last_elem_c { some

阅读全文

摘要:1. 前言: LSF(Load Sharing Facility)是IBM旗下的一款分布式集群管理系统软件,负责计算资源的管理和批处理作业的调度。它给用户提供统一的集群资源访问接口,让用户透明地访问整个集群资源。它通常是高性能计算环境中不可或缺的基础软件。LSF 是一种强大的工作负载管理平台,提供基

阅读全文

摘要:0.前言 EDA环境变量的设置可以说是芯片验证工程师的一项基本功,环顾四周,发现身边依然有不少小伙伴对EDA环境变量的设置并不是很熟悉,今天分享一份供大家参考。BTW,上次发这篇文章的时候,复制粘贴搞糊了,误把csh的部分设置粘贴到bash部分了。感谢网友及时指出,非常感谢!本篇已经做了更正,文末有

阅读全文

摘要:学过C语言都知道,在程序中添加打印信息有助于我们追踪程序执行的情况。特别是debug的时候,打印一些log信息对快速定位到问题非常有帮助。 怎么在SOC验证的C代码中打印字符串呢?用printf ? 我们来试一下: 执行结果: 没有出现 Hello world。这种结果是符合预期的。C code 通

阅读全文

摘要:汇总一下公众号的软件资源,因为破解敏感,所以以下软件均不提供破解教程,但多数都提供和谐文件,有问题可以加入软件交流群:「248615078」。大家可以在这个群互相分享不容易获得的软件,尤其是一些 IC 的软件。 Synopsys2020 2020 版本的 Synopsys,不提供破解,感兴趣的可以加

阅读全文

摘要:仿真是IC设计不可或缺的重要步聚,其中仿真波形是debug的必要条件。今天简要介绍下一下几种波形文件VCD/FSDB /SHM/VPD的dump方法。 其中VCD通用性最好,VCS/XRUN环境中直接加函数dump; 对于FSDB,本文讲述了VCS/XRUN 2种环境中基于函数和Tcl的2种dump

阅读全文

摘要:方法1:替换特定目录xxx下后缀名.sv格式的文件中aaa字符为bbb 字符 切换到对应目录, cd xxx 输入 g, 打开vim terminal vim 中切换成命令模式 :args *.sv `argdo %s/aaa/bbb/g | update` 其它文件格式同理,不再赘述。 方法2:替

阅读全文

摘要:最近在处理文件时,发现要对很多文件的某几处进行相同的修改,这让我想到用sed和awk去批量处理,但是单纯用sed和awk需要指定文件的位置,在处理大量文件的时候非常不方便。好在find帮我解决了这个问题。利用find 和xargs可以很轻松的实现批量文件的处理。接下来我和大家介绍下find和xarg

阅读全文

摘要:导言 本期主要给大家出一个简单makefile+tcl的仿真环境,支持vcs+verdi以及xrun+indago,因为最近虚拟机中的vcs不稳定,所有把以前的makefile修改一下同时支持vcs和xrun(xcelium),这两款仿真器我用的都是2020版本,如果你使用的低于这个版本,有些fea

阅读全文

摘要:VCS的仿真选项分编译(compile-time)选项和运行(run-time)选项。编译选项用于RTL/TB的编译,一遍是编译了就定了,不能在仿真中更改其特性,例如define等等。而仿真选项常用于仿真过程中控制仿真过程的选项,例如波形dump, testplusargs等等。 1.1 VCS常用

阅读全文

摘要:一,基础问答 1,Xcelium的由来? Xcelium(xrun)是cadence最新的仿真工具,Incisive(irun)的升级版本。 2,如何用xrun完成三步仿真? xrun默认是单步仿真 ``` xrun add.v //自动完成comp , elab ,sim ``` 三步仿真: ``

阅读全文

摘要:cadence,有两大验证仿真工具。一个是IUS,一个是IES。 IUS是cadence以前的仿真工具,功能略弱。代表工具,ncverilog。 官方介绍: IUS(incisive unified simulator) Cadence IUS allows to perform behaviora

阅读全文

摘要:目录 前言 一、MSIE是什么? 二、MSIE有什么好处? 三、使用步骤 1.MSIE IIP流程 2.MSIE PII 流程 3.关于HREF 总结 前言 Xcelium为了应对复杂的SOC设计和减少re-elaborate设计的时间提出了MSIE的流程(Multi-Snapshot Increm

阅读全文

摘要:为什么需要这个工具 验证工程师在初学UVM时,需要花些精力了解UVM验证环境的搭建。但是,验证工程师怎么能把有限的精力花费在搭建环境框架上呢。于是乎,有这么一个可以按需生成环境框架的工具就是必须品了。 由于是开源,可以根据验证团队的需求,做定制化的修改,这也是一个喜闻乐见的优点。 工具介绍: 官方介

阅读全文

摘要:之前有朋友问我怎么用脚本产生一个验证环境,这个问题今天和大家介绍下两种做法。 第一种用VCS自带的uvmgen工具 当你在命令行时直接输入uvmgen会输出如下信息: 选择1 然后按照提示步骤进行UVM环境的创建 创建完之后我们看看环境目录 刚才我们创建的env,agent,scoreboar,co

阅读全文

摘要:介绍一个通过GUI方式自动生成UVM环境的工具,uvm_testbench_gen。 工具来源于DVCon US 2022的一篇论文:Novel GUI Based UVM Test Bench Template Builder。 工具源码开源在git: https://github.com/hel

阅读全文

摘要:为了方便与C、C++等语言的交互,uvm中引入了DPI接口,自定义的函数需要写函数主体,然后再import后声明和使用,验证环境中便可以像调用system verilog中的函数一样使用这些函数。而且,对于C语言中内置的函数,不需要写函数主体,直接声明使用。同理c语言也可以调用sv里面的函数或者ta

阅读全文

摘要:1.可以使用 ((变量++)) 的方法实现变量递增 i=0; ((i++)); 2.可以使用 let 变量+=1 实现变量递增; i=0; let i+=1; 3.可以使用 i=

((i + 1 )) 实现变量递增; i=0 i=

((i + 1 )) 4.可以使用 i =

[i +

阅读全文