uvm中使用uvm_hdl_read的注意事项

在验证环境中,会经常使用uvm的后门操作系列函数,uvm_hdl_force, uvm_hdl_read, uvm_hdl_deposit等。使用后门操作可以直接通过信号的字符串hierarchy路径,进行对RTL内部信号的读取和赋值。

使用uvm_hdl_read常见的写法可能是这样:

bit rd_data_hdl;

if(uvm_hdl_read("tb.xxx",rd_data_hdl)) begin

....

end

if(rd_data_hdl == 1) ....

上面的这段代码有问题吗?

没问题,也有问题。

我们知道,RTL的内部信号是4态的,即一个信号的值可能是0、1、x、z. 在一些逻辑代码中,可能会存在X态或者Z态信号,比如:

从memory中读出的数据为X,然后传播下去

某输入信号没有驱动出现了高阻

非法时序导致cell输出X

...

因此上述的代码存在两个问题:

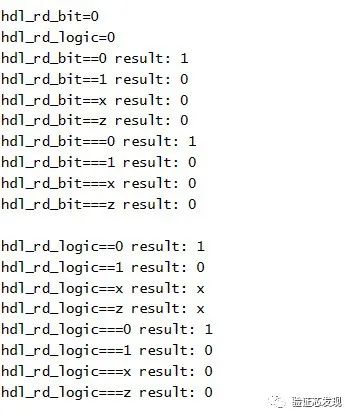

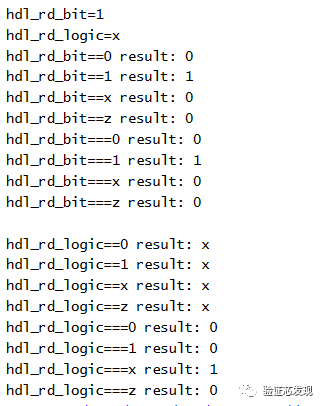

使用了bit而非logic类型数据

bit类型是两态信号,其取值可能是0或1,而logic是4态信号。所以使用bit类型数据,无法识别出RTL中X或者Z态数据。

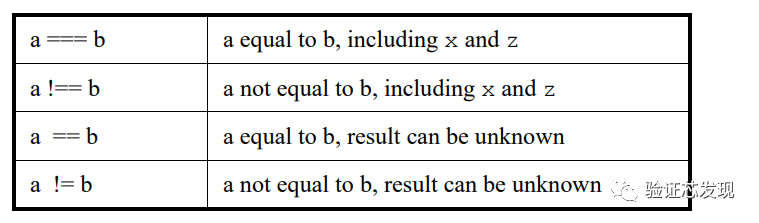

使用''判断相等,而不是'='

同样,''无法判断出x态或z态。而'='则会严格检查相等。二者区别可以参考:

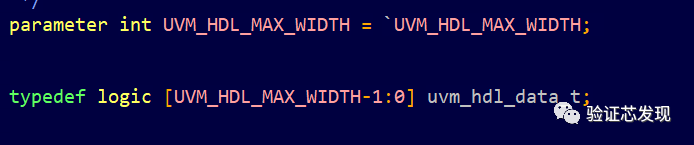

而且uvm_hdl_read函数的数据类型为uvm_hdl_data_t,也是一种logic的数据类型:

为此设计了如下的demo,作为参考:

import uvm_pkg::*;

`include "uvm_macros.svh"

class test extends uvm_test;

`uvm_component_utils(test)

function new(string name="test",uvm_component parent = null);

super.new(name,parent);

endfunction

virtual task main_phase(uvm_phase phase);

super.main_phase(phase);

phase.raise_objection(this);

hdl_read_x();

#7;

hdl_read_x();

phase.drop_objection(this);

endtask

virtual function void hdl_read_x();

logic hdl_rd_logic;

bit hdl_rd_bit;

void'(uvm_hdl_read("tb_top.clk",hdl_rd_bit));

void'(uvm_hdl_read("tb_top.clk_x",hdl_rd_logic));

$display("");

$display("hdl_rd_bit=%0x",hdl_rd_bit);

$display("hdl_rd_logic=%0x",hdl_rd_logic);

$display("hdl_rd_bit==0 result: %0d",hdl_rd_bit==0);

$display("hdl_rd_bit==1 result: %0d",hdl_rd_bit==1);

$display("hdl_rd_bit==x result: %0d",hdl_rd_bit==1'hx);

$display("hdl_rd_bit==z result: %0d",hdl_rd_bit==1'hz);

$display("hdl_rd_bit===0 result: %0d",hdl_rd_bit===0);

$display("hdl_rd_bit===1 result: %0d",hdl_rd_bit===1);

$display("hdl_rd_bit===x result: %0d",hdl_rd_bit===1'hx);

$display("hdl_rd_bit===z result: %0d\n",hdl_rd_bit===1'hz);

$display("hdl_rd_logic==0 result: %0d",hdl_rd_logic==0);

$display("hdl_rd_logic==1 result: %0d",hdl_rd_logic==1);

$display("hdl_rd_logic==x result: %0d",hdl_rd_logic==1'hx);

$display("hdl_rd_logic==z result: %0d",hdl_rd_logic==1'hz);

$display("hdl_rd_logic===0 result: %0d",hdl_rd_logic===0);

$display("hdl_rd_logic===1 result: %0d",hdl_rd_logic===1);

$display("hdl_rd_logic===x result: %0d",hdl_rd_logic===1'hx);

$display("hdl_rd_logic===z result: %0d",hdl_rd_logic===1'hz);

endfunction

endclass

program tb_top;

logic clk, clk_x;

initial begin

run_test("test");

end

initial begin

clk = 0;

forever #5 clk = ~clk;

end

initial begin

clk_x = 0;

#2;

clk_x = 'hx;

end

endprogram

仿真结果如下:

浙公网安备 33010602011771号

浙公网安备 33010602011771号