Verdi使用小技巧(一)

对于做数字集成电路的工程师来说,Verdi可以说是最常用的代码和波形观察工具了。这里列几个使用中的小技巧,说不上高明,不过自己用着感觉还是蛮有效率的。

1、总线拆分

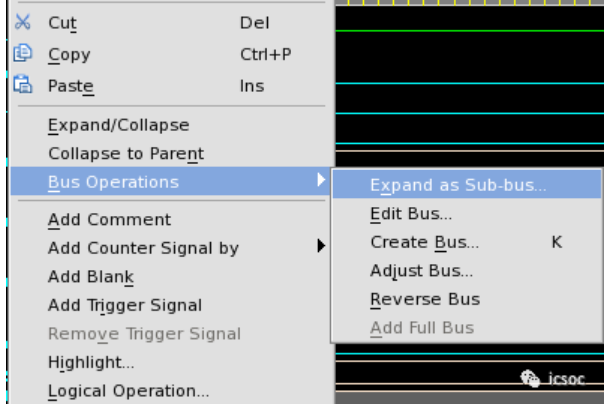

分析波形的时候有时候需要把一个多比特的bus拆分成几个位宽较小的bus,以方便观察数值。例如把一个20比特的bus拆成两个10比特的bus,可以右键点击这个bus,在弹出的菜单中点击Bus Operation,在弹出的对话框中的Every后面的输入框,输入10,意思是每10比特拆成一个bus,点击ok,就会看到出现了两个10比特的bus信号以及对应的波形。

2、统计

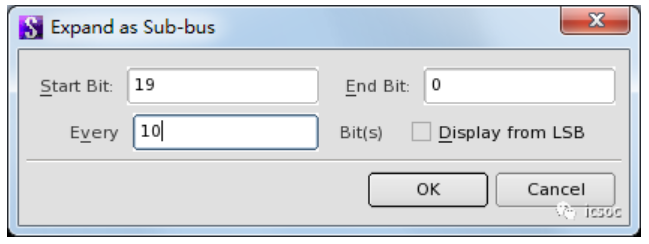

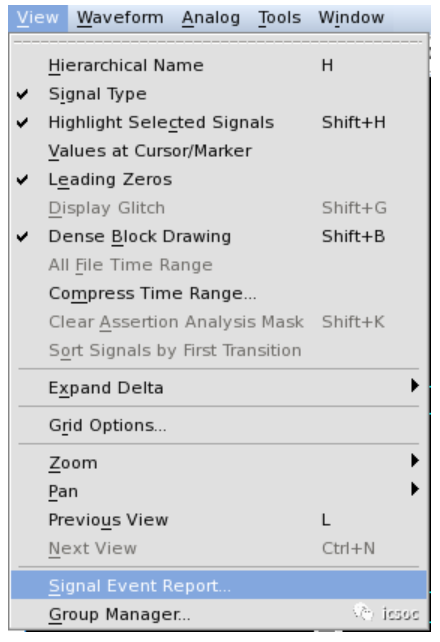

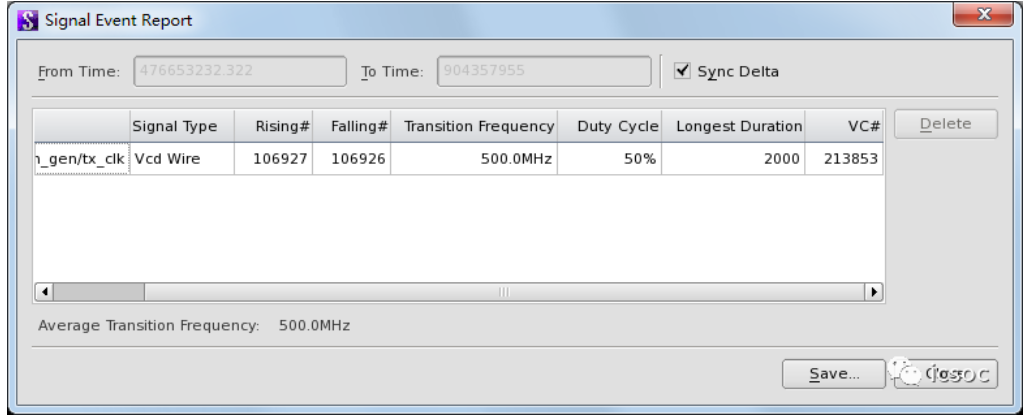

统计出某个信号在特定时间段内的跳变的次数。这个结合下一节的逻辑运算,可以把一些复杂的波形分析用直观的形式表现出来。还是右键点击波形窗口左边的某个信号名字,在弹出菜单中选择Signal Event Report。

在弹出的对话框中,可以关注感兴趣的内容,比如Rising#,指的是默认Markers标定的时间段内,该信号的上升沿次数。这样就不用很辛苦的放大波形,用眼睛一个一个去数了。

3、逻辑运算

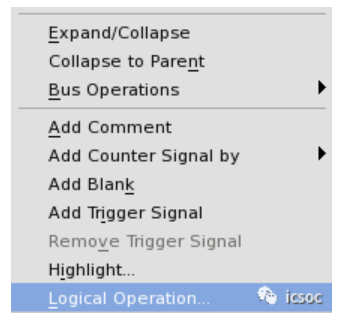

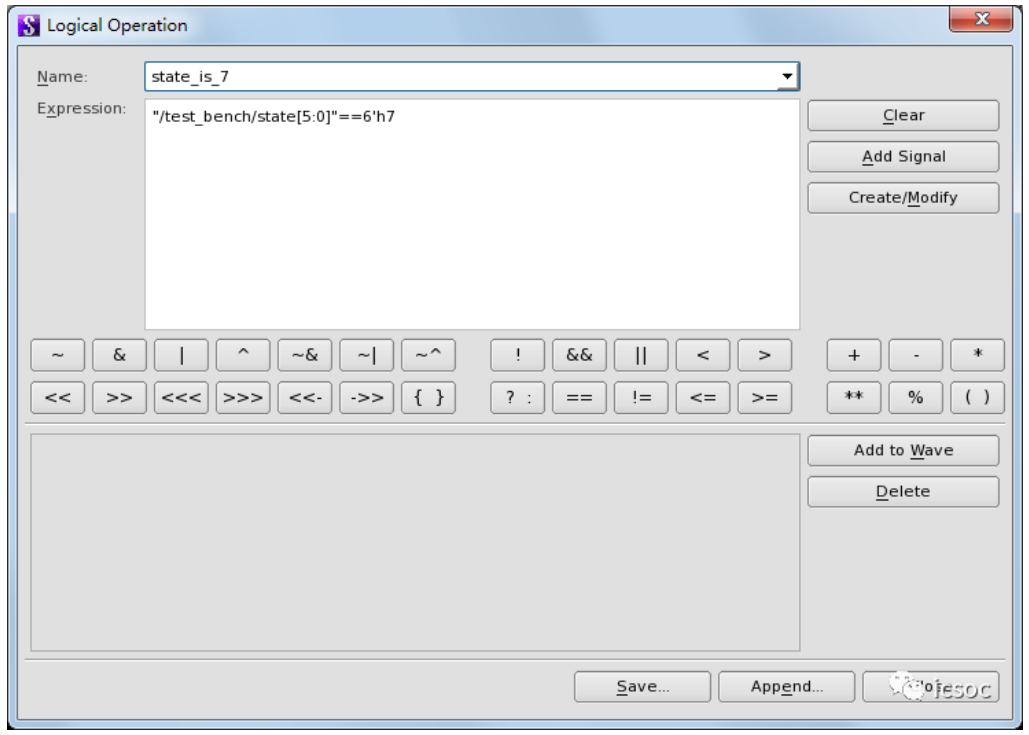

在一个频繁变化的信号、尤其是多比特的bus信号中观察是否出现了某个值,有时候可以通过搜索来追踪。但是如何一目了然地看到呢?通过右键点击该信号,在弹出的菜单上点击Logical Operation,通过新建一个信号,该信号是待观察信号的某种逻辑表达式。

比如,想知道这个state等于0x7的分布情况,就可以新建一个信号state_is_7等于state==0x7,这样看这个新信号什么时候为1,就可以了解特定状态的分布情况了。

4、manage.rc

manage.rc可以管理多个rc文件,实现每次启动Verdi都能载入预设的设置,同时不受上次启动Verdi后保存的设置影响。还可以保存本次使用过程中更改过的设置,以便更新预设设置。这个略微有些复杂。在启动Verdi时,需要加个参数。

-managercFile some_path/manage.rc

这个manage.rc的内容大概是这样的:

@Manage rc file Version 1.0

[File]

default_file = ~/load_only.rc

working_file = ./novas.rc

[Load]

default_file

[Save]

working_file = MODIFIED_KEY

例子中作为只读的default_file文件,可以放一些自己习惯或者喜欢的设置。比如tab等于4还是8,各种界面的字体,以及其它一些每次启动Verdi都希望生效的设置。working_file用来保存本次使用更改的设置,如果有想长期预设的,可以从中copy出来到default_file,这样方便升级迭代。

通过如下常规的参数调用

-rcFile some_path/some.rc

也可以读入一个rc文件实现类似预设功能,不过这种方法的缺点是这个rc文件会被当前调用覆盖。后果就是下次启动的Verdi会带有上次使用的痕迹,比如打开波形文件的目录位置。用的次数多了,不胜其烦。干脆用manage.rc来彻底的解决。

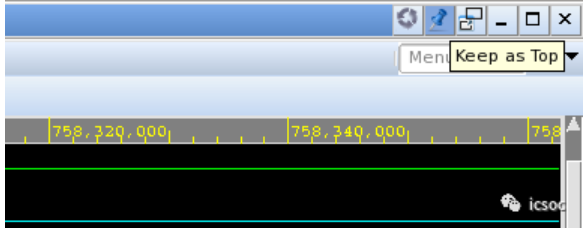

5、Trace代码过程中波形窗口保持前置

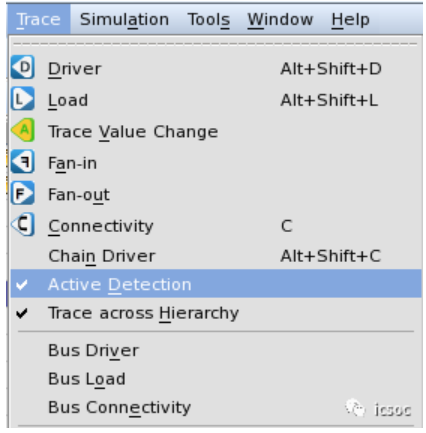

不知道从哪个版本开始,Verdi默认打开了Active Detection,Trace窗口在trace过程中会被激活前置,造成波形窗口被遮挡,也是不胜其烦。当然这也属于个人喜好问题。

那如何保持波形窗口始终在前呢?首先需要在Trace下拉菜单中取消Active Detection,然后点击波形窗口右上角的Keep as Top。

这样在代码Trace时,波形始终可以看到,方便debug。Active Detection可以在rc文件中预设。Keep as Top还没有找到预设的方法。

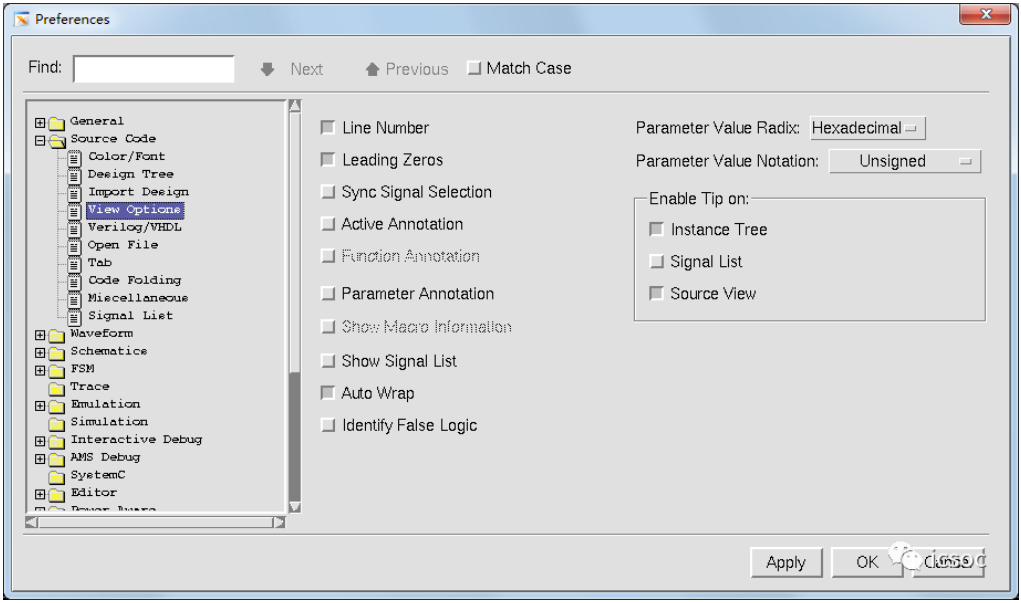

6、Parameter 提示的默认进制

在Verdi中,如果把鼠标放到Verilog代码中的parameter上,可以提示其值是多少。因为各种原因,有时候会以二进制的形式提示,如果这个parameter是32比特,那把这个二进制看明白也太费眼睛了。简单的话还是16进制比较易读。这个可以在下图中的Parameter Value Radix中设置。当然也可以把它加入rc文件进行预设。

浙公网安备 33010602011771号

浙公网安备 33010602011771号