Icarus verilog编译器相关

Overview

最近在github上看到一个AXI示例,非常详细,想看一看学习,作者表示运行需要预装Icarus verilog,虽然三大EDA的仿真软件都玩过,但这个软件我并不熟悉,遂在自己的虚拟机上安装并了解了一些内容

Icarus Verilog is not aimed at being a simulator in the traditional sense, but a compiler that generates code employed by back-end tools.

Icarus并不是一个仿真器,而是一个编译器

How Icarus Verilog Works

Icarus包含一个解析器,读取verilog文件随后产生一个中间网表,随后网表可以通过不同的处理步骤形成优化或实际的设计

实际上还包括一系列操作:前处理Preprocessing、解析Parse、精细化Elaboration、优化Optimization以及最后的代码生成Code Generation,感兴趣的可以官网深究一下

实操

按github的readme装好软件后实操玩一玩,先cp一个简单的代码示例

1 // ------------------------ hello.v ---------------------------- 2 module main(); 4 5 initial 6 begin 7 $display("Hello World"); 8 $finish ; 9 end 10 11 endmodule

使用 `iverilog hello.v` 即可进行编译

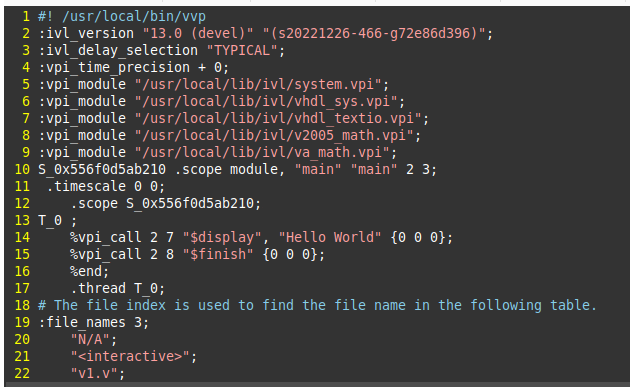

随后产生一个 `./a.out` 文件,打开一下,可以看到是我无法理解的网表格式?

实际上这里是通过软件的形式去生成对应的解析文件了,而不是常规流程中的先把hdl电路综合成对应的门级网表,在进行编译

直接执行,会产生正确的输出

![]()

https://github.com/steveicarus/iverilog?tab=readme-ov-file