数字电路设计优化

在进行rtl设计时,需要关注代码综合成门级网表之后的情况,因此coding时也有许多注意事项,本文将持续更新学习到的优化思路与方法。

1. 运算符优先级调整

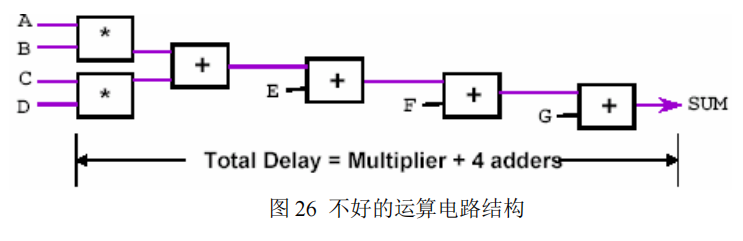

对于SUM <= A*B + C*D + E + F + G来说,综合后对应的电路结构如下图:

很明显,这样的延时太大了。而针对运算可以通过交换运算次序和加入括号形成优化的结构

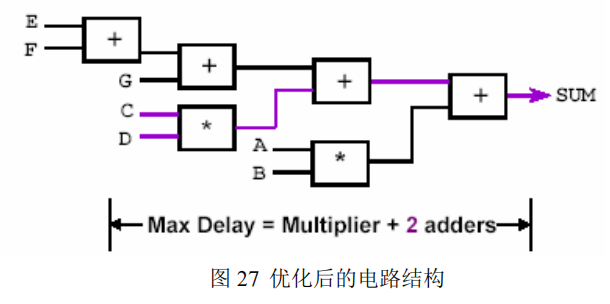

SUM <= (A*B) + ((C*D) + ((E + F)+G)),综合后对应的电路结构为:

可以看出Critical path只有一个乘法器和两个加法器的延时,时序得到了改善。